时钟分频方法---verilog代码

时钟分频方法---verilog代码

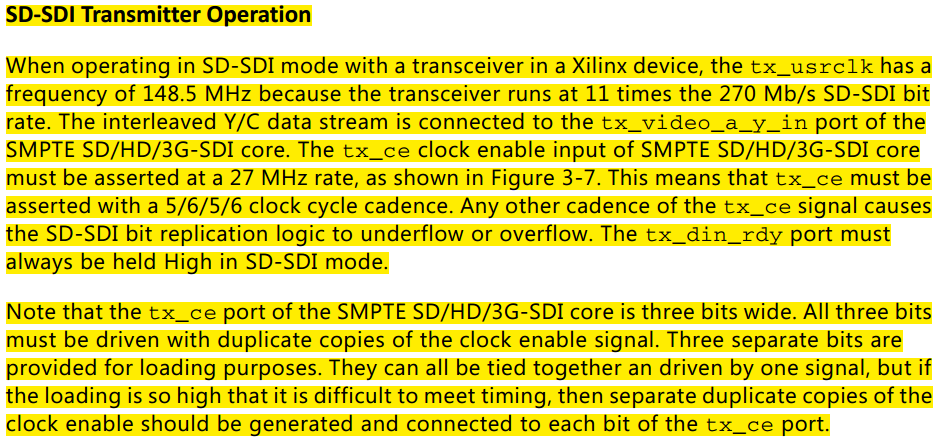

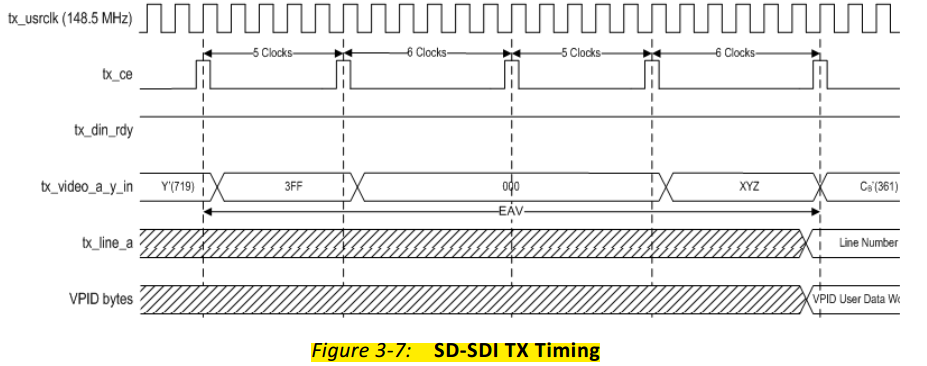

本文以SDI播出部分的工程为例,来说明一种时钟分频的写法。SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据采样与tx_ce(门控时钟)有关。通过对tx_usrclk时钟进行分频,5clocks---6clocks---5clocks---6clocks,得到tx_ce信号。

verilog代码写法如下:

reg [:] tx_ce = 'b111;

reg tx_sd_ce = 'b0;

reg [:] tx_gen_sd_ce = 'b00000100001; // Generates 5/6/5/6 cadence SD-SDI TX clock enable

wire tx_ce_mux; // Used to generate the tx_ce signals

//

// TX clock enable generator

//

// sd_ce runs at 27 MHz and is asserted at a 5/6/5/6 cadence

// tx_ce is always 1 for 3G-SDI and HD-SDI and equal to sd_ce for SD-SDI

//

// Create 3 identical but separate copies of the clock enable for loading purposes.

//

always @ (posedge tx_usrclk)

if (tx_fabric_reset) //复位信号来源于?

tx_gen_sd_ce <= 'b00000100001;

else

tx_gen_sd_ce <= {tx_gen_sd_ce[:], tx_gen_sd_ce[]}; //此段代码用于产生 always @ (posedge tx_usrclk)

tx_sd_ce <= tx_gen_sd_ce[]; assign tx_ce_mux = tx_mode == 'b01 ? tx_gen_sd_ce[10] : 1'b1; always @ (posedge tx_usrclk)

tx_ce <= { {tx_ce_mux}};

重点关注tx_gen_sd_ce = 11'b00000100001信号,用来生成5/6/5/6序列。

always @ (posedge tx_usrclk)

if (tx_fabric_reset) //复位信号来源于?

tx_gen_sd_ce <= 'b00000100001;

else

tx_gen_sd_ce <= {tx_gen_sd_ce[:], tx_gen_sd_ce[]}; //此段代码用于产生

always @ (posedge tx_usrclk)

tx_sd_ce <= tx_gen_sd_ce[];

每当tx_usrclk上升沿到来时,tx_gen_sd_ce左移一位,最高位移到最低位。tx_sd_ce取tx_gen_sd_ce的最高位,需要注意的是:tx_gen_sd_ce 和tx_sd_ce是同时变化的,都由tx_usrclk上升沿控制。

当tx_gen_sd_ce = 10000100000时,tx_sd_ce为高电平,由此开始,当下一次tx_sd_ce为高电平时,tx_gen_sd_ce = 10000010000需要花费5clocks,当tx_sd_ce再次为高电平时,tx_gen_sd_ce = 10000100000需要花费6clocks,循环下去,由此就产生了5/6/5/6序列。

时钟分频方法---verilog代码的更多相关文章

- HD,3G视频数据中行号的插入方法---Verilog代码实现

HD,3G视频数据中行号的插入方法---Verilog代码实现 行号的生成: `timescale 1ns / 1ps //////////////////////////////////////// ...

- 分享:FIFO 同步、异步以及Verilog代码实现

FIFO 很重要,之前参加的各类电子公司的逻辑设计的笔试几乎都会考到. FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线 ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- FIFO 的控制逻辑---verilog代码

FIFO 的控制逻辑---verilog代码 //fifo的例化 wire fifo_full; wire fifo_empty; : ] fifo_dout; :]rd_data_count; :] ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

随机推荐

- C语言基础:数组 分类: iOS学习 c语言基础 2015-06-10 21:40 7人阅读 评论(0) 收藏

数组:是由一组具有相同数据类型的数据组合而来. 数组定义:元素类型修饰符 数组名[数组个数]={元素1,元素2....}; int arr[ 2 ]={1,2}; //正确 int arr[ ...

- promise、async和await之执行顺序

async function async1(){ console.log('async1 start') await async2() console.log('async1 end') } asyn ...

- Spring Relational Database

为了避免持久化的逻辑分散到应用的各个组件中,将数据访问功能放到一个或多个专注于此项任务的组件中,这样的组件通常称为数据访问对象(DAO)或Repository. 为了避免应用与特定的数据访问策略耦合在 ...

- PAP认证(单向、双向)

实验要求:掌握PAP单向.双向认证 拓扑如下: 单向验证 R1(认证方)enable 进入特权模式configure terminal 进入全局模式hostname R1 设置主机名interface ...

- python学习笔记第一周

目录: 一.基础概念 1.变量与常量介绍 2.引号的使用 3.条件判断 4.while与for循环 5.input输入 6.getpass模块 7.python编码 二.作业 1.个人登录系统 2.多 ...

- Mac 终端添加代码到SVN

从SVN拉取代码步骤: 1.cd /Users/mark/zkh/Work/BC/(本地路径) 2.svn checkout https://192.168.2.99/svn/bc_android ...

- json2的基本用法

<script type="text/javascript" src="/CoreResource/JS/json2.min.js"></sc ...

- mac os x lipo 工具

lipo是管理Fat文件的工具,可以查看平台列表,提取.重新打包 dreamdeMac-mini:test dream$ lipo -info libtest001.a Architectures i ...

- ORACLE RAC 11.2.0.4 CentOS release 6.9 静默安装1.0版本

RAC11.2.0.4静默安装 1.0版本,20180613 #本文档IP地址使用X隐藏,个人可按照自己的当前环境IP进行适当修改 1. 清除原环境中的单实例软件 #清除原环境: 删除/etc/ora ...

- 将button或者input角变为圆弧

style="border-radius:5px;" input框时,不能用type属性