【FPGA】高斯白噪声的Verilog实现

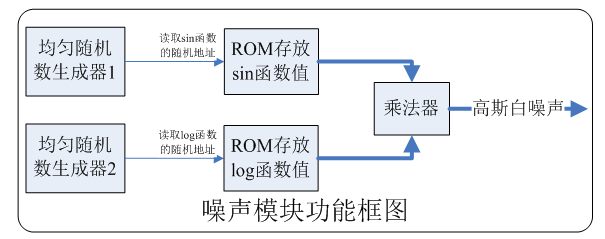

本文章主要讨论高斯白噪声的FPGA实现。简单的方法可以采用在Matlab中产生服从一定均值和方差的I、Q两路噪声信号。然后将两组数据存在FPGA中进行回放,以此来产生高斯白噪声。这种方法优点是产生方法简单占用FPGA资源少,但是他只能保证在回放噪声的一段数据是满足不相关特性的,段与段之间的数据是相关的。为了使整个过程中的噪声都满足不相关特性,可以通过LSFR序列的交错异或,得到均匀分布的伪随机信号,采用在一个ROM中存储sin函数值另一个ROM中存储log函数值。通过产生随机读地址的方式随机读取两个ROM中的数据,将两组随机的函数值相乘得到高斯白噪声。模块功能框图如下图。

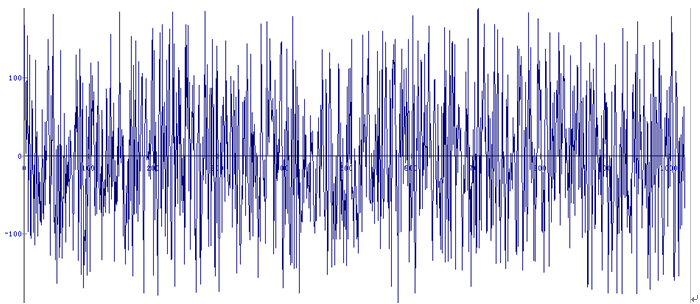

chipscope调试结果:

//////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////子模块1

module rand_gen(

input wire clk100,

input wire rst,

output reg [:] orbit_sin_addr, //rand number for sin ROM addr, [10:]

output reg [:] orbit_log_addr //rand number for log ROM addr, [9:0]

);

wire resetup; // asynchronous clear, high active

wire [:] orbit_1;

wire [:] orbit_2;

wire [:] orbit_3;

wire [:] orbit_4;

parameter initval_1='b010110010010110111110001,

initval_2='b100000111100010111010001,

initval_3='b001101000001010010010001,

initval_4='b111010100110010011110001;

// 交错异或子模块

inter_feedback_rand_1 inter_feedback_rand_1_inst (

.orbit(orbit_1), //[10:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_1) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

inter_feedback_rand_2 inter_feedback_rand_2_inst (

.orbit(orbit_2), //[10:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_2) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

inter_feedback_rand_3 inter_feedback_rand_3_inst (

.orbit(orbit_3), //[9:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_3) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

inter_feedback_rand_4 inter_feedback_rand_4_inst (

.orbit(orbit_4), //[9:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_4) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

// orbit_sin_addr [10:0] //

//////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk100 or posedge rst) begin

if(rst) begin

orbit_sin_addr <= 'b0;

end

else

orbit_sin_addr <= orbit_1 ^ orbit_2;

end

//////////////////////////////////////////////////////////////////////////////////

// orbit_log_addr [9:0 ] //

//////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk100 or posedge rst) begin

if(rst) begin

orbit_log_addr <= 'b0;

end

else

orbit_log_addr <= orbit_3 ^ orbit_4;

end

//////////////////////////////////////////////////////////////////////////////////

// resetup //

//////////////////////////////////////////////////////////////////////////////////

reg resetup_r = 'b0;

assign resetup = resetup_r;

always @ (posedge clk100 or posedge rst) begin

if(rst)

resetup_r <= 'd1;

else

resetup_r <= 'd0;

end

endmodule

//////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////子模块2

module noise_gen(

input wire clk100,

input wire rst,

input wire noise_en,

input wire [:] orbit_sin_addr,

input wire [:] orbit_log_addr,

output wire [:] noise_out

);

wire [:] sin_data;

wire [:] log_data;

// 正弦、对数、乘法IP核

Sin Sin_inst (

.clka(clk100), // input clka

.ena(noise_en), // input ena

.addra(orbit_sin_addr), // input [10 : 0] addra

.douta(sin_data) // output [7 : 0] douta

);

Log Log_inst (

.clka(clk100), // input clka

.ena(noise_en), // input ena

.addra(orbit_log_addr), // input [9 : 0] addra

.douta(log_data) // output [7 : 0] douta

);

Mult_signed Mult_signed_inst (

.clk(clk100), // input clk

.a(sin_data), // input [7 : 0] a

.b(log_data), // input [7 : 0] b

.ce(noise_en), // input ce

.sclr(rst), // input sclr

.p(noise_out) // output [15 : 0] p

);

endmodule

//////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////顶层模块(部分)

rand_gen rand_gen_inst_1 (

.clk100(clk100),

.rst(rst),

.orbit_sin_addr(orbit_sin_addr_1),

.orbit_log_addr(orbit_log_addr_1)

);

noise_gen noise_gen_inst_1 (

.clk100(clk100),

.rst(rst),

.noise_en(noise_en),

.orbit_sin_addr(orbit_sin_addr_1),

.orbit_log_addr(orbit_log_addr_1),

.noise_out(noise_out_1)

);

/////////////////////////////////////////////////////////////////////////////////feedback1

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_1(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit[:]=sr_a[:];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

/////////////////////////////////////////////////////////////////////////////////feedback2

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_2(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

/////////////////////////////////////////////////////////////////////////////////feedback3

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_3(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit=sr_a[:];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

/////////////////////////////////////////////////////////////////////////////////feedback4

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_4(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

转载请声明出处,谢谢。

【FPGA】高斯白噪声的Verilog实现的更多相关文章

- Matlab实现加性高斯白噪声信道(AWGN)下的digital调制格式识别分类

Matlab实现加性高斯白噪声信道(AWGN)下的digital调制格式识别分类 内容大纲 加性高斯白噪声信道(AWGN)下的digital调制格式识别分类 (1. PSK; 2. QPSK; 3.8 ...

- [转] Matlab中给信号加高斯白噪声的方法

MATLAB中产生高斯白噪声非常方便,可以直接应用两个函数,一个是WGN,另一个是AWGN.WGN用于产生高斯白噪声,AWGN则用于在某一信号中加入高斯白噪声. 1. WGN:产生高斯白噪声 y = ...

- 高斯白噪声(white Gaussian noise,WGN)

本文科普一下高斯白噪声(white Gaussian noise,WGN). 百度百科上解释为“高斯白噪声,幅度分布服从高斯分布,功率谱密度服从均匀分布”,听起来有些晦涩难懂,下面结合例子通俗而详细地 ...

- MATLAB中产生高斯白噪声的两个函数

MATLAB中产生高斯白噪声非常方便,可以直接应用两个函数,一个是WGN,另一个是AWGN.WGN用于产生高斯白噪声,AWGN则用于在某一信号中加入高斯白噪声.1.WGN:产生高斯白噪声 y = wg ...

- FPGA按键去抖verilog代码

按键去抖的原因及其分类就不罗嗦了. 在这里解释一段代码,代码是网上找的,看了半天没懂,无奈查了半天想了半天,终于明白了... module sw_debounce(clk,rst_n,sw1,sw2, ...

- FPGA 状态机-序列检测器verilog

实现功能:检测出串行输入数据4位Data二进制序列0101,当检测到该序列的时候,out=1,否则out=0 (1)给出状态编码,画出状态图 (2)门电路实现 (3)verilog实现 首先规定Q3Q ...

- 【FPGA篇章三】FPGA常用语句:Verilog基本语法要素

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章 Verilog中总共有十九种数据类型,我们先介绍四个最基本的数据类型,他们是: reg型.wire型.integer型.parameter型 ...

- 【MATLAB】对离散采样信号添加高斯白噪声(已知Eb/N0)

(1)首先计算已知信号序列(采样之后得到的信号)的平均功率.该序列在第n个点处的功率为: 如果已知的信号序列中的总共的点数为N个,则该序列的平均功率为: 在MATLAB中求平均功率的方法是: Pav= ...

- python 写matlab中的加性高斯白噪声AWGN

定义 原始信号:x 噪声信号:n 信噪比:SNR 信号长度:N def wgn(x, snr): snr = 10**(snr/10.0) xpower = np.sum(x**2)/len(x) n ...

随机推荐

- 在c++中,标准输入string时cin 与getline两个函数之间的区别

cin: cin函数是标准库的输入函数,在读取string时遵循以下规则: 1)读取并忽略开头所有的空白符(包括空格.换行符.制表符). 2)读取字符直到遇到空白符,读取终止. 例如: 当输入的是“ ...

- angular二级联动菜单

<!doctype html> <html lang="en" ng-app='App'> <head> <meta charset=&q ...

- poj2594最小顶点覆盖+传递闭包

传递闭包最开始是在Floyd-Warshall算法里面出现的,当时这算法用的很少就被我忽视了.. 传递闭包是指如果i能到达k,并且k能到达j,那么i就能到达j Have you ever read a ...

- 关于WebService、WebApi的跨域问题

随着移动互联网的发展, 传统营销模式往网站以及移动客户端转移已经成为一种趋势.接触过互联网开发的开发者肯定会很熟悉两种网络服务WebApi.WebService.在使用JavaScript进行数据交互 ...

- 2017Wow!新媒体营销深度分享会值得参加吗?

"Wow!新媒体营销深度分享会"是虎嗅打造的创新跨界营销平台,以引领营销趋势和洞察技术奇点为目标,推动前沿技术创新与营销的碰撞融合. 在这里,你将看到2017年最前瞻的营销趋势.最 ...

- 我的开发环境搭建(ubuntu菜鸟)

前段时间把系统换成了ubuntu,经过一段时间到发展,终于可以比较正常到完成开发工作了,但是就在今天,我的系统崩了,进不了桌面,而且终端里边到中文也显示乱码,尝试了网上说到各种方法无效,最终我决定重装 ...

- 玩转mongodb(九):通过log4jmongo来实现分布式系统的日志统一管理

背景 在分布式系统中,我们有多个web app,这些web app可能分别部署在不同的物理服务器上,并且有各自的日志输出.当生产问题来临时,很多时候都需要去各个日志文件中查找可能的异常,相当耗费人力. ...

- 设计模式--MVC(C++版)

MVC 模式代表 Model-View-Controller(模型-视图-控制器) 模式.这种模式用于应用程序的分层开发. Model(模型)-是应用程序中用于处理应用程序数据逻辑的部分.通常模型对象 ...

- Gartner:当商业智能成熟度低时,如何加快分析采用率

文 | 水手哥 本文出自:知乎专栏<帆软数据应用研究院>--数据干货&资讯集中地 根据Gartner近7年的调查结果,71%的受访企业处于低成熟度阶段,也就是Gartner五级BI ...

- 在R中整理数据

原始数据一般分散杂乱,并含有缺失和错误值,因此在进行数据分析前首先要对数据进行整理. 一.首先,了解原始数据的结构. 可使用如下函数(归属baseR)来查看数据结构: class(dataobject ...