Verilog有符号整型数(signed int)比大小

本文参考了https://blog.csdn.net/wenxinwukui234/article/details/42119265/ 关于2进制补码的思考和讨论。

======================================================================================================

即使在变量声明的时候定义了signed属性, 在Verilog中使用>(大于),>=(大于等于),<(小于)和<=(小于等于)进行有符号数的大小比较时还是没有想要的结果。

现在需要实现一个有符号数比较的功能。

1、一些注记。

以8位有符号数(signed int)为例,表示范围是-128~+127,有一些边缘的数很有特征,记下来方便使用:

0000_0000 表示 0;

0000_0001 表示 +1;

1111_1111 表示 -1;

0111_1111 表示 +127;

1000_0001 表示 -127;

1000_0000 表示 -128.

我们发现,(1)除了0和-128,其他相反数按无符号相加,得到的是0000_0000(即0000_0000)。

(2)非负数的MSB(最高位)=0;负数的MSB=1。

2、比较规则。

我们设a和b为输入的两个signed 8类型的比较数,并且a>=b(GE)时输出信号y为1,否则输出为0。比较的规则如下:

(1)非负数一定大于负数。

(2)负数一定小于非负数。

(3)a、b同是非负数,则按unsigned比较两个数:a>=b则y=1;a<b则y=0。

(4)a、b同是负数,则按unsigned比较a和b的[6:0]即除去符号位:a[6:0]>=b[6:0]则y=1;a[6:0]<b[6:0]则y=0。

3、Verilog模块。

//************************************

// A >= B -> 1

// A < B -> 0

//

//************************************

module ageb_s8(

rst_n,

sys_sam_clk,

a,

b,

cmp_out ); //****************************************

// Port Def.

//

//****************************************

input wire rst_n;

input wire sys_sam_clk; input wire[:] a;

input wire[:] b; output wire cmp_out; //****************************************

// Define

//

//****************************************

localparam YES = 'b1;

localparam NO = 'b0; //****************************************

// Variables

//

//****************************************

reg cmp_reg; //****************************************

// Behaviour

//

//****************************************

assign cmp_out = cmp_reg; //*** Compare Logic

always@(posedge sys_sam_clk)begin

if(!rst_n)begin

cmp_reg <= 1'b0;

end

else begin

case({a[], b[]})

'b01:begin // a+, b-

cmp_reg <= 'b1;

end

'b10:begin // a-, b+

cmp_reg <= 'b0;

end

'b00:begin // a+, b+, Compare Amplitude

if(a[:] >= b[:])begin // Unsigned Compare

cmp_reg <= 'b1;

end

else begin

cmp_reg <= 'b0;

end

end

'b11:begin // a-, b-, Compare [6:0]

if(a[:] >= b[:])begin

cmp_reg <= 'b1;

end

else begin

cmp_reg <= 'b0;

end

end

default:begin

cmp_reg <= 'b0;

end

endcase

end

end endmodule

4、仿真

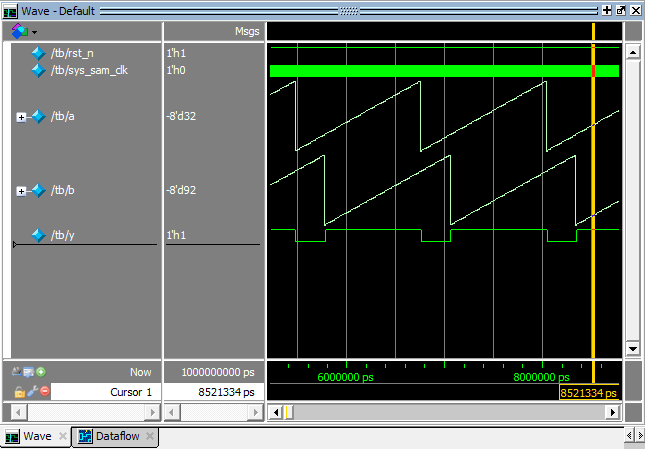

整体:比较结果y是PWM信号的形式。

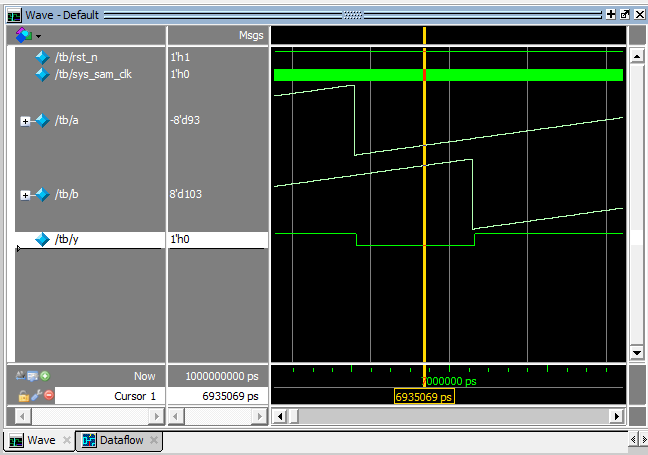

局部:a<b

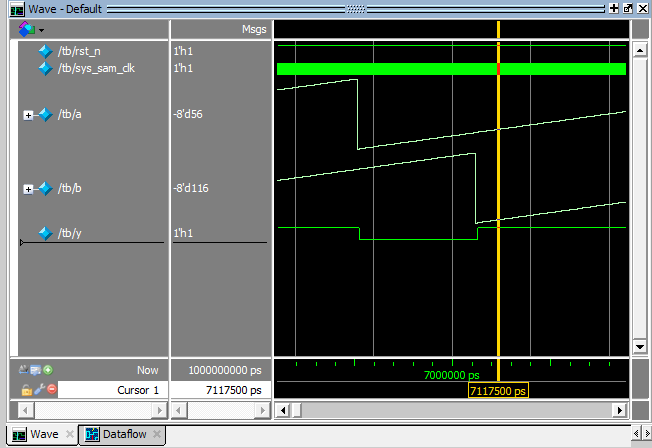

局部:a>b

仿真结果满足我的需要。

Verilog有符号整型数(signed int)比大小的更多相关文章

- v.size() return size_t not int 返回无符号整型数

In the C++ STL, the vector size() function return size_t, which is unsigned int, not int. So imagine ...

- 无符号整型 unsigned int、unsigned long、usigned long long、size_t 比较和格式控制

位数比较 由于数据的长度和平台相关,所以基于 64 位系统比较. Windows Linux unsigned int 32 bits/4294967295 32 bits unsigned long ...

- leetcode菜鸡斗智斗勇系列(1)---把一个链表中的二进制数字转换为一个整型数(int)

Convert Binary Number in a Linked List to Integer这道题在leetcode上面算作是“easy”,然而小生我还是不会做,于是根据大佬的回答来整理一下思路 ...

- 使用程序获取整型数据和浮点型数据在内存中的表示---gyy整理

使用程序获取整型数据和浮点型数据在内存中的表示. C++中整型(int).短整型(short int).单精度浮点数(float).双精度浮点数(double)在内存中所占字节数不同,因此取值范围也不 ...

- strtoul (将字符串转换成无符号长整型数)

strtoul strtoul (将字符串转换成无符号长整型数) 相关函数 atof,atoi,atol,strtod,strtol 表头文件 #include<stdlib.h> 定义函 ...

- 求一个整型数字中有没有相同的部分,例如12386123这个整型数字中相同的部分是123,相同的部分至少应该是2位数,如果有相同部分返回1,如果没有则返回0。方法是先将整型数字转换到数组中,再判断。函数为 int same(int num)其中num是输入的整型数字

import java.util.ArrayList; import java.util.List; import java.util.Scanner; public class Test { pub ...

- 整型:int

整型:int 整型变量的定义和输出 注意://short<=int<=long<=longlong 代码示例一: #include<stdio.h> int ma ...

- PHP中IP地址与整型数字互相转换详解

这篇文章主要介绍了PHP中IP地址与整型数字互相转换详解,本文介绍了使用PHP函数ip2long与long2ip的使用,以及它们的BUG介绍,最后给出自己写的两个算法,需要的朋友可以参考下 IP转换成 ...

- 使用头文件climits中的符号常量获知整型数据的表数范围---gyy整理

在头文件climits(limits.h)以宏定义的方式定义了各种符号常量来表示各种整型类型表示数的范围,如int的最大最小值,long的最大最小值等. 符号常量 表示 CHAR_BIT char 的 ...

随机推荐

- pandas读取文件的read_csv()方法

import pandas as pd pd.read_csv(filepath_or_buffer,header,parse_dates,index_col) 返回数据类型:DataFrame:二维 ...

- 输入url到展示页面过程发生了什么?

输入网址,首先在书签或者历史记录里面去搜索相关的网址推荐给你 浏览器查找域名的IP的地址(在hosts文件有没有对应IP -> 浏览器发出一个DNS请求到本地DNS服务器,本地服务器一般是网 ...

- vs下载为0的问题

问题描述:win10 下无法安装VS2017,visual studio installer下载进度始终为0,点击取消按钮后,也没有反应,visual studio installer也关闭不掉: 具 ...

- Scrapy 分布式爬取

由于受到计算机能力和网络带宽的限制,单台计算机运行的爬虫咋爬取数据量较大时,需要耗费很长时间.分布式爬取的思想是“人多力量大”,在网络中的多台计算机同时运行程序,公童完成一个大型爬取任务, Scrap ...

- Maven笔记一

简介:什么是maven Maven是一个跨平台的项目管理工具,主要用于基于java平台的项目构建,依赖管理. 如图为项目构建的过程. 解决的项目的问题: 1. 如果有好几个项目,这好几个项目中,需要 ...

- if,while,for循环

目录 if条件 while循环 for循环 拓展知识点 if条件 if 条件: code elif 条件: code else: code # 三元运算符 x = 10 y = 20 print(y ...

- 吴裕雄 Bootstrap 前端框架开发——Bootstrap 排版:设定引用右对齐

<!DOCTYPE html> <html> <head> <title>菜鸟教程(runoob.com)</title> <meta ...

- ANSYS-MFC二次开发

目录 1. 开发流程 2. 开发代码 1. 开发流程 ANSYS-MFC二次开发的思路其实是特别简单的,通常MFC主要是设计界面,然后从MFC界面中读取要设计的参数,然后根据这些设置了的参数生成APD ...

- 第1节 Scala基础语法:1、2、概述,什么是scala

Scala编程 1. 课程目标 1.1. 目标1:熟练使用scala编写Spark程序 1.2. 目标2:动手编写一个简易版的Spark通信框架 1.3. 目标3:为阅读Spark内核源码 ...

- 调用天气预报webservice接口

1.将 服务端的wsdl文档保存至 本地 http://ws.webxml.com.cn/WebServices/WeatherWS.asmx?WSDL 2.将里面的 <s:element re ...