[原创][FPGA]时钟分频之奇分频(5分频)

0. 简介

有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录。

1. 奇分频

其实现很简单,主要为使用两个计数模块分别计数,得到两个波形进行基本与或操作完成。直接贴出代码部分如下。

module div_freq(

iCLK,

iRST_n,

oCLK

);

input wire iCLK;

input wire iRST_n;

output oCLK;

'd5;

reg clk_p;

:] cnt_p;

always @ (posedge iCLK or negedge iRST_n) begin

if (!iRST_n)

cnt_p <= 'd0;

)

cnt_p <= 'd0;

else

cnt_p <= cnt_p + 'b1;

end

always @ (posedge iCLK or negedge iRST_n) begin

if (!iRST_n)

clk_p <= 'b0;

) / )

clk_p <= ~clk_p;

)

clk_p <= ~clk_p;

else

clk_p <= clk_p;

end

reg clk_n;

:] cnt_n;

always @ (negedge iCLK or negedge iRST_n) begin

if (!iRST_n)

cnt_n <= 'd0;

)

cnt_n <= 'd0;

else

cnt_n <= cnt_n + 'b1;

end

always @ (negedge iCLK or negedge iRST_n) begin

if (!iRST_n)

clk_n <= 'b0;

) / )

clk_n <= ~clk_n;

)

clk_n <= ~clk_n;

else

clk_n <= clk_n;

end

assign oCLK = clk_p | clk_n;

endmodule

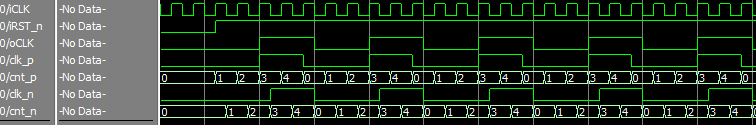

modelsim仿真结果如下图

[原创][FPGA]时钟分频之奇分频(5分频)的更多相关文章

- FPGA时钟分频(转)

http://www.cnblogs.com/fpga/archive/2009/10/24/1589318.html 占空比为50%的分频 偶数分频比较简单 比如N分频,那么计数到N/2-1,然后时 ...

- 一站式入口服务|爱奇艺微服务平台 API 网关实战 原创 弹性计算团队 爱奇艺技术产品团队

一站式入口服务|爱奇艺微服务平台 API 网关实战 原创 弹性计算团队 爱奇艺技术产品团队

- [原创][FPGA][IP-Core]altlvds_tx & altlvds_rx

1. 概述 Alter公司的QuartusII软件提供了LVDS发送和接收的IP核供我们使用,其在本质上可以理解为并行-串行数据的转换器.其在官方文档(见附件)上也这样说过.其中的应用场景有告诉AD/ ...

- [原创][FPGA]有限状态机FSM学习笔记(一)

1. 概述--何为有限状态机FSM? 有限状态机-Finite State Machine,简写为FSM,是表示有限个状态及在这些状态之间的转移和动作等行为的数学模型,在计算机领域有着广泛的应用.通常 ...

- [原创]FPGA JTAG工具设计(二)

经过前期打样 基于FT2232H的JTAG &UART板级已经初步形成 在Viado环境和ISE(13.2+)环境可以使用 速度支持10MHz/15MHz/30MHz 在ISE iMpact下 ...

- [原创]FPGA JTAG工具设计(一)

先来看不同JTAG方案,下载配置QSPI Flash所耗时间 基于FTDI方案,JTAG下载时间为494sec JTAG chain configuration ------------------- ...

- [原创][FPGA]Quartus实用小技巧(长期更新)

0. 简介 在使用Quartus软件时,经常会时不时的发现一些小技巧,本文的目的是总结所查阅或者发现到的小技巧,本文长期更新. 1. Quartus中的模板功能 最近在Quartus II的菜单里找到 ...

- [原创][FPGA]Quartus中调用Modelsim波形仿真步骤说明

0. 简介 在使用QuartusII软件的过程中,经常地需要跑仿真,那么说到仿真就不得不说Modelsim这个仿真软件了,我们这里介绍下该软件在QuartusII中的使用方法. 1. 建立Quartu ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

随机推荐

- vue 顶级组件

快 有时候懒的把一些通用组件写到template里面去,而业务中又需要用到,比如表示loading状态这样组件. 如果是这样的组件,可以选择把组件手动初始化,让组件在整个app生命周期中始终保持活跃. ...

- 【php】 phpword下载文件问题

这个问题是在 科锐国际 工作过程中发现的 word文档的名字(有汉字和空格)在windows系统上遍历是查不到文件的,但是在linux系统上市可以的压缩包里面的中文名word文档,如果出现汉字和空格, ...

- Cheese Aizu - 0558 (搜索题)

Time limit8000 ms Memory limit131072 kB チーズ () 問題 今年も JOI 町のチーズ工場がチーズの生産を始め,ねずみが巣から顔を出した.JOI 町は東西南北に ...

- Linux学习-善用判断式

利用 test 指令的测试功能 要检测系统上面某些文件或者是相关的属性时,利用 test 这个指令来工作真是好用得不 得了, 举例来说,我要检查 /dmtsai 是否存在时,使用: [dmtsai@s ...

- Linux学习-进程管理

为什么进程管理这么重要呢? 这是因为: 首先,我们在操作系统时的各项工作其实都是经过某个 PID 来达成的 (包括你的 bash 环境), 因此,能不能进行某项工作,就与该进程的权限有关了. 再来,如 ...

- 在alert里面加入一个页面,子页面传值父页面

把easyDialog v2.0这个插件加入到了项目中,在做选择部门功能时运用这个插件,在easyDialog.open里面的content函数中套了一个iframe标签,把部门页面的地址放入到src ...

- HDU 2852 KiKi's K-Number 主席树

题意: 要求维护一个数据结构,支持下面三种操作: \(0 \, e\):插入一个值为\(e\)的元素 \(1 \, e\):删除一个值为\(e\)的元素 \(2 \, a \, k\):查询比\(a\ ...

- luogu3469 [POI2008]BLO-Blockade

#include <iostream> #include <cstring> #include <cstdio> using namespace std; type ...

- 03_HibernateSessionFactory源码分析

文章导读: 讲解了一个线程为什么要使用同一个connection, 我们分析了HiberatenSessionFactory的实现机制, 然后根据Hibernate的写法重构了我们的代码. 最后测试可 ...

- python-高级编程-06-长连接&连接池

我们都知道tcp是基于连接的协议,其实这个连接只是一个逻辑上面的概念,在ip层来看,tcp和udp仅仅是内容上稍有差别而已. tcp 的连接仅仅是连接两端对于四元组和sequence号的一种约定而已 ...