8421BCD转余3码Verilog HDL的设计(1)

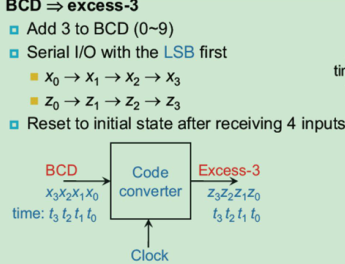

近期阅读Verilog HDL高级数字设计(第二版)中,遇到了串行比特流BCD码转余3码转换器的设计,比较独特的是:

(1)该转换器的输入为1位串行比特流,输出也为1位串行比特流。

BCD码与余三码的转换关系如下:

8421BCD码=余3码+0011

| 10进制 | 8421BCD码 | 余3码 | 10进制 | 8421BCD码 | 余3码 |

| 0 | 0000 | 0011 | 8 | 1000 | 1011 |

| 1 | 0001 | 0100 | 9 | 1001 | 1100 |

| 2 | 0010 | 0101 | 10 | 1010 | 1101 |

| 3 | 0011 | 0110 | 11 | 1011 | 1110 |

| 4 | 0100 | 0111 | 12 | 1100 | 1111 |

| 5 | 0101 | 1000 | 13 | 1101 | 10000 |

| 6 | 0110 | 1001 | 14 | 1110 | 10001 |

| 7 | 0111 | 1010 | 15 | 1111 | 10010 |

由表1可知,当8421BCD码为13、14、15时候,余三码已经超出了4位二进制能表示的范围(无符号数0~15),因此本次中暂不考虑。

转换器的输入为1位串行比特流,输出为1位相应余三码的串行比特流,设计思路如下:

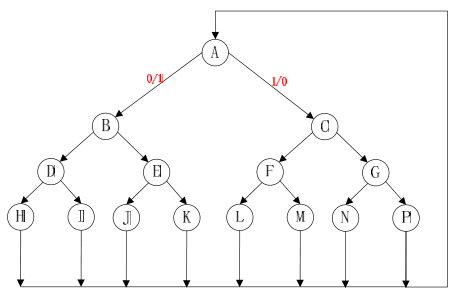

图1 状态转换示意图

设BCD码输入比特流Bin在t0,t1,t2,t3的输入分别为t0t1t2t3,设余三码输出比特流Bout在t0,t1,t2,t3时刻的输出分别为T0T1T2T3

假设转换器的初始状态为状态A:

(1)在状态A下,t0时刻Bin输入的值可能为0或者1:当bin输入0时,进入B状态;当bin输入1时,进入C状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

A状态(t0时刻,Bin=0),Bout=1 |

A状态(t0时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:B | t3t2t1t0 | T3T2T1T0 | 下一个状态:C |

| 0000 | 0011 | 0001 | 0010 | ||

| 0010 | 0101 | 0011 | 0110 | ||

| 0100 | 0111 | 0101 | 1000 | ||

| 0110 | 1001 | 0111 | 1010 | ||

| 1000 | 1011 | 1001 | 1100 | ||

| 1010 | 1101 | 1011 | 1110 | ||

| 1100 | 1111 | 1101 | (1)0000 | ||

(2)在B状态,t1时刻Bin输入的值可能为0或者1:当bin输入0时,进入D状态;当bin输入1时,进入E状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

B状态(t1时刻,Bin=0),Bout=1 |

B状态(t1时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:D | t3t2t1t0 | T3T2T1T0 | 下一个状态:E |

| 0000 | 0011 | 0010 | 0101 | ||

| 0100 | 0111 | 0110 | 1001 | ||

| 1000 | 1011 | 1010 | 1101 | ||

| 1100 | 1111 | 1110 | (1)0001 | ||

(3)在D状态,t2时刻Bin输入的值可能为0或者1:当bin输入0时,进入H状态;当bin输入1时,进入I状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

D状态(t2时刻,Bin=0),Bout=0 |

E状态(t2时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:H | t3t2t1t0 | T3T2T1T0 | 下一个状态:I |

| 0000 | 0011 | 0100 | 0111 | ||

| 1000 | 1011 | 1100 | 1111 | ||

(4)在H状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

H状态(t3时刻,Bin=0),Bout=0 |

H状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0000 | 0011 | 1000 | 1011 | ||

(5)在I状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

I状态(t3时刻,Bin=0),Bout=0 |

I状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0100 | 0111 | 1100 | 1111 | ||

(6)在E状态,t2时刻Bin输入的值可能为0或者1:当bin输入0时,进入J状态;当bin输入1时,进入K状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

E状态(t2时刻,Bin=0),Bout=1 |

E状态(t2时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:J | t3t2t1t0 | T3T2T1T0 | 下一个状态:K |

| 0010 | 0101 | 0110 | 1001 | ||

| 1010 | 1101 | 1110 | (1)0001 | ||

(7)在J状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

J状态(t3时刻,Bin=0),Bout=0 |

J状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0010 | 0101 | 1010 | 1101 | ||

(8)在K状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

K状态(t3时刻,Bin=0),Bout=1 |

K状态(t3时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0110 | 1001 | 1110 | (1)0001 | ||

未完待续。。。

8421BCD转余3码Verilog HDL的设计(1)的更多相关文章

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

- 浅谈Verilog HDL代码编写风格

消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周末这会儿有时间,写点东西,记录下来.首先我学习FPGA才一年多,我知道自己没有资格谈论一些比较深层次 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- 你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点. 二十进制编码器及Verilog HDL描述 二十进制编码器是数字电路中常用的电路单元 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- Verilog HDL模块的结构

一个设计是由一个个模块(module)构成的.一个模块的设计如下: 1.模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字 ...

随机推荐

- Sqlite教程(4) Activity

之前我们已经有了DbHelper.Data Access Object.Configuration. 那麽现在就是由Activity去创建它们,然後就可以存取Sqlite. 架构图表示了它们的关系. ...

- single-value grouping |limit grouping|cutpoint grouping|Lower class limit|Upper class limit|Class width|Class mark|rounding error or roundoff error|Histograms|Dotplots|Stem-and-Leaf

2.3 Organizing Quantitative Data group quantitative data: To organize quantitative data, we first gr ...

- python之urllib模块和requests模块

一.urllib模块 python标准库自带的发送网络请求的模块. # 用python怎么打开浏览器,发送接口请求 import urllib from urllib.request import u ...

- file_get_contents为何无法采集某些压缩过的网站

有些网站直接用file_get_contents就能采集, 但是有些不行. 于是可以在网址前加入 'compress.zlib://‘ $url = 'compress.zlib://' . 'htt ...

- Python之循环条件、变量、字符串格式化

一.认识python python语言的优缺点,自行百度,这里不概述,简单说下,python是一门面向对象,解释型计算机语言.那么问题来了,解释型和编译型语言有什么区别? 1.解释型和编译型语言区别 ...

- python学习笔记(4)数据类型-元组

元组其实和列表一样,不一样的是,元组的值不能改变,一旦创建,就不能再改变了,比如说,要存数据库的连接信息,这个连接信息在程序运行中是不能被改变的,如果变了那数据库连不上了,就程序就完犊子了,这样的就可 ...

- @echo off 批处理

一个批处理文件 @echo off ipconfig /all @pause -------------------------------- @echo off 是什么意思 就是说关闭回显@echo ...

- SpringCloud快速搭建

1.SpringCloud 为开发人员提供了快速构建分布式系统的一些工具,包括配置管理.服务发现.断路器.路由.负载均衡.微代理.事件总线.全局锁.决策竞选.分布式会话等等.它运行环境简单,可以在开发 ...

- Struts2开发基本步骤

1 加载jar文件 commons-fileupload.jar commons-io.jar commons-lang.jar freemaker.jar ognl.jar ...

- leetcode 1.回文数-(easy)

2019.7.11leetcode刷题 难度 easy 题目名称 回文数 题目摘要 判断一个整数是否是回文数.回文数是指正序(从左向右)和倒序(从右向左)读都是一样的整数. 思路 一些一定不为回文数的 ...