ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言

在Block design中引出AXI接口给外部,检查设计告警如下:

[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly. Please update ASSOCIATED_BUSIF parameter of a clock port to include this interface port.

在块设计中,时钟、复位、bus是分开的,需要把时钟复位引出。

同时在时钟管脚上关联上引出的AXI名称,否则vivado会告个警,但不解决应该也没啥问题,只要相应的信号引出了的话。

参考文档:

https://forums.xilinx.com/t5/Design-Entry/making-AXI-interface-a-external-port/m-p/465418#M5638

操作流程

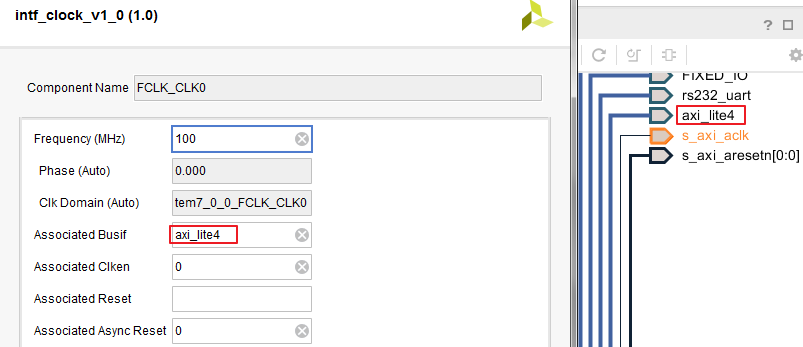

双击下图中的引出时钟,出现左侧界面,修改关联bus为axi_lite4(引出的总线名字)。

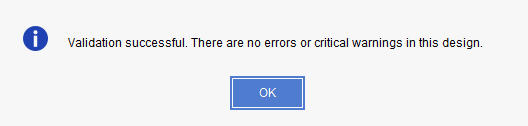

再检查设计的合理性,可以看到不再报警告。

以上。

ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.的更多相关文章

- ZYNQ Block Design中总线位宽的截取与合并操作

前言 在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作. 在verilog下,截位操作可如下所示: wire [7:0] w_in; wire ...

- 使用Vivado的block design

使用Vivado的block design (1)调用ZYNQ7 Processing System (2)配置ZYNQ7系统 (3)外设端口配置 根据开发板原理图MIO48和MIO49配置成了串口通 ...

- Block Design 小技巧之添加RTL代码到block_design

Block Design 小技巧之添加RTL代码到block_design 1.首先得打开Block Design,右击RTL文件,才会出现Add module to Block Design选项. ...

- Vivado中备份设计好的block design

参考链接 https://blog.csdn.net/dimples_song/article/details/81391615 前言 为了不每次都重新生成block design,避免重复劳动. 可 ...

- 方差分析|残差|MSA/MSE|Completely randomized design|Randomized block design|LSD|主效应|intercept|多重比较|

符合方差分析的三个条件: 残差=实际值-预测值(其实是均值). 在原假设下,MSA的期望会等于MSE的期望:在备选假设下,MSA的期望会大于MSE的期望,所以MSA/MSE的取值范围在(1,正无穷), ...

- simplify the design of the hardware forming the interface between the processor and thememory system

Computer Systems A Programmer's Perspective Second Edition Many computer systems place restrictions ...

- 在ZYBO板卡上实现PL-PS交互(通过AXI的方式)

前情提要:参考的是下面所说的原网页,只是原作者用的是vivado 2014.4,我用vivado 2018.2跑的,图是新的,内容大多“换汤不换药”,但是我在做的时候存在一些问题,我记录了下来并将解决 ...

- ZYNQ笔记(2):PS端——Hello World !

PL端使用过后,来到了ZYNQ核心的部分:PS端,现在用Vivado软件对ZYNQ-7000开发板的PS端进行第一个程序设计:Hello World. 一.新建Vivado工程 1.打开Vivado, ...

- (转) 使用vivado创建工程 1

此文全文转自:http://svenand.blogdrive.com/archive/169.html#.WaUV9IiGNPY ,非常感谢! 本人在vivado 2015.4版本测试! When ...

随机推荐

- 范仁义html+css课程---4、文本标签

范仁义html+css课程---4.文本标签 一.总结 一句话总结: 文本标签大致掌握一下,做到它站在你对面的时候最好认得,认不得也没关系,直接百度 1.ins标签.u标签和del标签 作用? ins ...

- Jmeter命令行运行配置环境变量

Jmeter命令行运行配置环境变量 在打开jmeter GUI界面时会弹出cmd命令窗口提示:压测时不要用GUI,要用命令行 在cmd命令行里面运行jmeter的话,需要配置jmeter环境变量,下面 ...

- linux学习(5):linux 性能瓶颈排查

作为开发人员,肯定遇到过以下场景,应用突然卡住了,或者异常退出,cpu占用过高等各种异常情况,一般遇到这些异常情况,该如何去查找具体原因呢? linux和jdk提供了一些命令和工具来查看内存.cpu. ...

- @MatrixVariable的使用

@MatrixVariable的使用 博客分类: J2EE 在Spring3.2 后,一个@MatrixVariable出现了,这个注解的出现拓展了URL请求地址的功能. Matrix Varia ...

- Oracle系列五 多表查询

笛卡尔集笛卡尔集会在下面条件下产生: 省略连接条件 连接条件无效 所有表中的所有行互相连接 为了避免笛卡尔集, 可以在 WHERE 加入有效的连接条件. Oracle 连接 使用连接在多个表中查询数据 ...

- Visual Studio 2017 vcvarsall.bat 环境配置对应关系

博客参考:https://chenzehe.iteye.com/blog/1703429 安装Visual Studio 2017之后,vcvarsall.bat ,vcvars32.bat,vcva ...

- Docker搭建ES集群

Spring Boot连接ES,spring-boot-starter-data-elasticsearch. 必须为集群方式!否则报错! 报错: None of the configured nod ...

- 数据分析入门——pandas之DataFrame多层/多级索引与聚合操作

一.行多层索引 1.隐式创建 在构造函数中给index.colunms等多个数组实现(datafarme与series都可以) df的多级索引创建方法类似: 2.显式创建pd.MultiIndex 其 ...

- Linux下查找命令 —— find、grep、 which、 whereis、 locate

find命令 基本格式 find < path > < expression > < cmd > ''' path: 所要搜索的目录及其所有子目录.默认为当前目录. ...

- (转)自动微分(Automatic Differentiation)简介——tensorflow核心原理

现代深度学习系统中(比如MXNet, TensorFlow等)都用到了一种技术——自动微分.在此之前,机器学习社区中很少发挥这个利器,一般都是用Backpropagation进行梯度求解,然后进行SG ...