【iCore4 双核心板_FPGA】例程十七:基于FIFO的ARM+FPGA数据存取实验

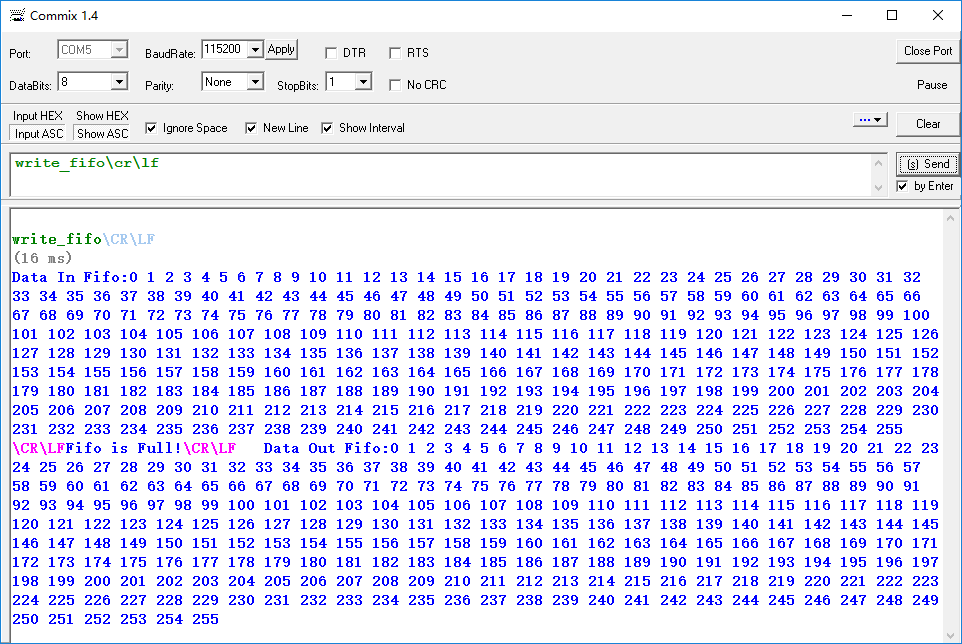

实验现象:

核心代码:

int main(void)

{ /* USER CODE BEGIN 1 */

int i;

int fsmc_read_data;

char error_flag = ;

char receive_data[];

char buffer[];

char *p;

/* USER CODE END 1 */ /* MCU Configuration----------------------------------------------------------*/ /* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init(); /* USER CODE BEGIN Init */ /* USER CODE END Init */ /* Configure the system clock */

SystemClock_Config(); /* USER CODE BEGIN SysInit */ /* USER CODE END SysInit */ /* Initialize all configured peripherals */

MX_GPIO_Init();

MX_USART6_UART_Init();

MX_FMC_Init(); /* USER CODE BEGIN 2 */

usart6.initialize();

usart6.printf("Hello,I am iCore4!\r\n");

LED_GREEN_ON;

/* USER CODE END 2 */ /* Infinite loop */

/* USER CODE BEGIN WHILE */

while ()

{

/* USER CODE END WHILE */ /* USER CODE BEGIN 3 */

if(usart6.receive_ok_flag == ){

usart6.receive_ok_flag = ;

memset(receive_data,,sizeof(receive_data));

memset(buffer,,sizeof(buffer));

for(i = ;i < ;i ++){

receive_data[i] = usart6.receive_buffer[i];

}

p = receive_data;

i = ;

while(*p != '\r'){ //»ñÈ¡²Ù×÷ÃüÁî

buffer[i++] = *p++;

if(i > sizeof(buffer))i = ;

}

for(i = ;i < sizeof(buffer);i++){//½«ÃüÁîת»¯ÎªÐ¡Ð´×Ö·û

buffer[i] = tolower(buffer[i]);

} if(memcmp(buffer,"write_fifo",strlen("write_fifo")) == ){//Ö´ÐÐдFifo

error_flag = ;

usart6.printf("Data In Fifo:");

for(i = ;;i++){

fpga_write(,i);

usart6.printf("%d ",i);

if(FIFO_FULL){

fpga_write(,i+);

usart6.printf("%d ",i+);

usart6.printf(" \r\nFifo is Full!\r\n Data Out Fifo:");

for(i = ;i < ;i++){ //¿ªÊ¼¶ÁÈ¡256¸öÊý¾Ý

fsmc_read_data = fpga_read();

usart6.printf("%d ",fsmc_read_data); //¶ÁÈ¡Öµ·¢ËÍÖÁ´®¿Ú

}

break;

}

}

}else{

error_flag = ;

} if(error_flag){

LED_RED_ON;

LED_GREEN_OFF;

usart6.printf("Bad Command!\r\n");

}else{

LED_RED_OFF;

LED_GREEN_ON;

}

}

}

/* USER CODE END 3 */ }

module fifo_wr_rd(

input clk_25m,

input rst_n,

input wrn,

input rdn,

input cs0,

input nadv,

input [:]ab,

inout [:]db,

output fifo_full_flag,

output led_red,

output led_green,

output led_blue

); pll u1(

.inclk0(clk_25m),

.c0(clk_150m)

); wire [:]data_out;

my_fifo u2(

.data(data_in),

.wrreq('d1),

.wrclk(wr2),

.rdreq('d1),

.rdclk(!rd),

.wrfull(fifo_full_flag),

.q(data_out)

); reg [:]data_in;

always@(posedge wrn or negedge rst_n)

if(!rst_n)

data_in <= 'd0;

else

data_in <= db; reg wr1,wr2;

always@(posedge clk_150m or negedge rst_n)

if(!rst_n)

begin

wr1 <= 'd0;

wr2 <= 'd0;

end

else

{wr2,wr1} <= {wr1,wr}; wire rd = rdn | cs0;

wire wr = wrn | cs0; assign db = rd ? 'hzzzz : data_out;

assign led_red = 'd1;

assign led_green = 'd0;

assign led_blue = 'd1; endmodule

源代码下载链接:

链接:http://pan.baidu.com/s/1jHFNhwq 密码:qktz

iCore4链接:

【iCore4 双核心板_FPGA】例程十七:基于FIFO的ARM+FPGA数据存取实验的更多相关文章

- 【iCore3 双核心板_FPGA】实验二十:基于FIFO的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1cmisnO iCore3 购买链接: https://item.taobao.com/item.htm?id=5242294 ...

- 【iCore4 双核心板_FPGA】例程十三:基于SPI的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符HELLO. 3.通过串口精灵发送命令可以控制ARM·LE ...

- 【iCore4 双核心板_FPGA】例程十四:基于I2C的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符GINGKO. 3.通过串口精灵发送命令可以控制ARM·L ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 【iCore4 双核心板_FPGA】例程十二:基于UART的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,会接收到字符GINGKO. 3.通过串口精灵发送命令可以控制ARM·LED和FPGA·LED. 核心代码: int main ...

- 【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf 读RAM命令格式:read:地址(0-255)\cr\lf 核心代码: int main(void) ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore4 双核心板_FPGA】例程四:Signal Tapll 实验——逻辑分析仪

实验现象: 三色led轮流闪烁,具体的逻辑分析仪使用教程请参考iCore3逻辑分析仪例程 核心代码: module signal_ctrl( input clk_25m, input rst_n, o ...

- 【iCore4 双核心板_FPGA】例程八:乘法器实验——乘法器使用

实验现象: 程序运行时,绿色led闪烁(目前,具体的乘法器调用请参考iCore3乘法器例程) 核心代码: module multiplier_ctrl( input clk_25m, input rs ...

随机推荐

- npm、webpack、vue-cli 快速上手版

Node.js npm 什么是Node.js 以及npm 简单的来说 Node.js 就是运行在服务端的JavaScript,基于Chrome V8 引擎的. npm 是Node.js 的包管理 ...

- 解决在VUE中绑定WebSocket事件无法传值的问题

this.webSocket.onerror =(env)=>{ this.onError(env) }; https://jsfiddle.net/dko6g9a4/1/

- 潭州课堂25班:Ph201805201 django 项目 第二十三课 文章主页 轮播图前端实现 热门新闻推荐实现 详情页实现 (课堂笔记)

前台代码 // 在static/js/news/index.js文件中 $(function () { // 新闻列表功能 let $newsLi = $(".news-nav ul li& ...

- System.out.println()和System.err.println()

在一次笔试中遇到了一个System.err.println()的输出,之前没有见过,回来查一查,自己还是见识太短,来补充一下. 首先看一看jdk中 来一个简单的实验 第一次显示 第二次显示 1. 发现 ...

- win7生成ssh key配置到gitlab

测试服务上使用ip访问gitlab,比如http://192.168.0.2/,创建用户并登陆后创建一个项目,比如git@gitlab.demo.com:demo/helloworld.git 如果想 ...

- bzoj1708:[Usaco2007 Oct]Money奶牛的硬币(完全背包

1708: [Usaco2007 Oct]Money奶牛的硬币 Time Limit: 5 Sec Memory Limit: 64 MBSubmit: 797 Solved: 540[Submi ...

- 微信公众号开发之通过获取token等信息

<?php /** * 发送post请求 * @param string $url * @param string $param * @return bool|mixed */ function ...

- C# 计算地图上某个坐标点的是否在多边形内

这个方法引用自群友的博客 https://www.xiaofengyu.com/?p=143 使用百度地图的时候,常常会用到判断一个点是否在一个多边形的范围内,该方法用到的是射线法, 通过修改Java ...

- 11、jQuery其余操作

上篇主要介绍了jQuery,和一些基本用法,这篇主要讲解动画.常用事件.还有一些jQuery的补充内容. 本篇导航: 动画 常用事件 插件 jQuery API 中文文档 一.动画 1.基本 show ...

- 关于kafka重新消费数据问题

我们在使用consumer消费数据时,有些情况下我们需要对已经消费过的数据进行重新消费,这里介绍kafka中两种重新消费数据的方法. 1. 修改offset 我们在使用consumer消费的时候,每个 ...