【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

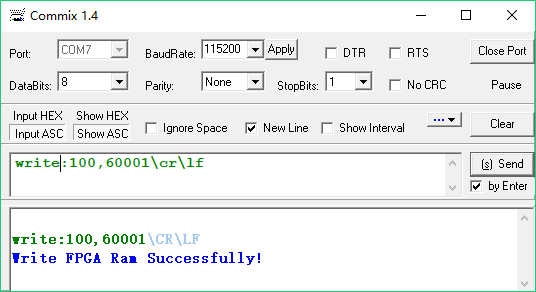

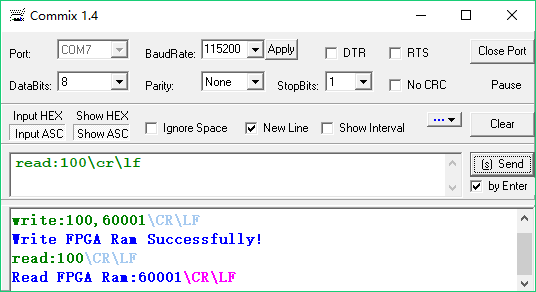

实验现象:

写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf

读RAM命令格式:read:地址(0-255)\cr\lf

核心代码:

int main(void)

{ /* USER CODE BEGIN 1 */

int i;

int address,data;

char error_flag = ;

char receive_data[];

char buffer[];

char *p;

/* USER CODE END 1 */ /* MCU Configuration----------------------------------------------------------*/ /* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init(); /* USER CODE BEGIN Init */ /* USER CODE END Init */ /* Configure the system clock */

SystemClock_Config(); /* USER CODE BEGIN SysInit */ /* USER CODE END SysInit */ /* Initialize all configured peripherals */

MX_GPIO_Init();

MX_USART6_UART_Init();

MX_FMC_Init(); /* USER CODE BEGIN 2 */

usart6.initialize();

usart6.printf("Hello, I am iCore4!\r\n"); /* USER CODE END 2 */ /* Infinite loop */

/* USER CODE BEGIN WHILE */

while ()

{

/* USER CODE END WHILE */ /* USER CODE BEGIN 3 */

if(usart6.receive_ok_flag == ){

usart6.receive_ok_flag = ;

memset(receive_data,,sizeof(receive_data));

memset(buffer,,sizeof(buffer));

for(i = ;i < ;i ++){

receive_data[i] = usart6.receive_buffer[i];

}

p = receive_data;

i = ;

while(*p != ':'){ //»ñÈ¡²Ù×÷ÃüÁwrite or read£©

buffer[i++] = *p++;

if(i > sizeof(buffer))i = ;

}

for(i = ;i < sizeof(buffer);i++){//½«ÃüÁîת»¯ÎªÐ¡Ð´×Ö·û

buffer[i] = tolower(buffer[i]);

}

if(memcmp(buffer,"write",strlen("write")) == ){//Ö´ÐÐд²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

p = strchr(p,',');

if(p == NULL)error_flag = ;

if(!error_flag){

p++;

data = atoi(p);

if(data > )error_flag = ; if(!error_flag){

fpga_write(address,data);

usart6.printf("Write FPGA Ram Successfully!");

}

}

}else{

if(memcmp(buffer,"read",strlen("read")) == ){//Ö´ÐжÁ²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

if(strchr(p,','))error_flag = ;

if(!error_flag){

data = fpga_read(address);

usart6.printf("Read FPGA Ram:%d\r\n",data);

}

}else{

error_flag = ;

}

}

if(error_flag){

LED_RED_ON;

LED_GREEN_OFF;

usart6.printf("Bad Command!\r\n");

}else{

LED_RED_OFF;

LED_GREEN_ON;

}

}

}

/* USER CODE END 3 */ }

module ram_ctrl(

input clk_100m,

input rst_n,

input wr_n,

input rd_n,

input cs0,

input [:]ab,

inout [:]db,

output led_red,

output led_green,

output led_blue

);

//----------------------------clk------------------------------//

wire wr,rd;

wire [:]data_out; assign wr = wr_n | cs0;

assign rd = rd_n | cs0; reg wr_0,wr_1;

always@(posedge clk_100m or negedge rst_n)

if(!rst_n)

begin

wr_0 <= 'd1;

wr_1 <= 'd1;

end

else

{wr_1,wr_0} <= {wr_0,wr}; wire clk = !wr_1 | !rd;

assign db = !rd ? data_out:'hzzzz; //----------------------------ram------------------------------//

ram u1(

.clock(clk),

.wren(!wr),

.rden(!rd),

.address(ab),

.data(db),

.q(data_out)

); //----------------------------led_ctrl-------------------------//

reg led;

always@(posedge clk or negedge rst_n)

if(!rst_n)

led <= 'd1;

else

led <= ~led; assign {led_red,led_green,led_blue} = {'d1,led,1'd1}; endmodule

源代码下载链接:

链接:http://pan.baidu.com/s/1pKZTJAj 密码:pkf7

iCore4链接:

【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

- 【iCore3 双核心板_FPGA】实验十八:基于单口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1i58Ssvz iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板】例程十五:USB_CDC实验——高速数据传输

实验指导书及代码包下载: http://pan.baidu.com/s/1gemYjz9 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore4 双核心板_FPGA】例程十:FSMC总线通信实验——复用地址模式

实验原理: STM32F767上自带FMC控制器,本实验将通过FMC总线的地址复用模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

- 【iCore4 双核心板_FPGA】例程十四:基于I2C的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符GINGKO. 3.通过串口精灵发送命令可以控制ARM·L ...

- 【iCore4 双核心板_FPGA】例程十一:FSMC总线通信实验——独立地址模式

实验原理: STM32F767上自带FMC控制器,本实验将通过FMC总线的地址独立模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

随机推荐

- Flutter常用组件(Widget)解析-ListView

一个可滚动的列表组件 不管在哪,列表组件都尤为重要和常用. 首先来看个例子: import 'package:flutter/material.dart'; void main () => ru ...

- ogg - 从oracle到mysql的同步

说明:这篇文章将介绍如何配置oracle到mysql的ogg同步 源端:ip-192.168.56.11 数据库类型-oracle 11.2.0.4目标端:ip-192.168.56.71 数据库类型 ...

- python新手总结(二)

random模块 随机小数 random uniform 随机整数 randint randrange 随机抽取 choice sample 打乱顺序 shuffle random.random() ...

- linux manjaro 配置 pytorch gpu 环境

manjaro目前中国资料偏少,踩了很多坑. 安装gpu版本就这么几个步骤 1 安装英伟达的驱动cuda 2 安装 cudnn 3 安装支持gpu的pytorch 或者其他的运算框架 manja ...

- JS-排序详解-选择排序

说明 时间复杂度指的是一个算法执行所耗费的时间 空间复杂度指运行完一个程序所需内存的大小 稳定指,如果a=b,a在b的前面,排序后a仍然在b的前面 不稳定指,如果a=b,a在b的前面,排序后可能会交换 ...

- 每日踩坑 2018-01-09 WebAPI会如何面对 枚举 参数?

这一块确实有些疑问, 众所周知 枚举参数我们传送枚举值所对应的数字就行了, 以前 Leader 跟我讲过,枚举参数会将字符串值也能够成功转化,而且枚举值定义之外的数字也可以被转为枚举值. 主要的问题在 ...

- 项目冲刺Third

Third Sprint PS:经今天讨论,我们小队决定撤掉用GUI设计界面,改用html和php制作,所以需要修改前面的博客及重新分配任务 1.各个成员今日完成的任务 蔡振翼:撰写博客 谢孟轩:借阅 ...

- bzoj 3991: [SDOI2015]寻宝游戏 虚树 set

目录 题目链接 题解 代码 题目链接 bzoj 3991: [SDOI2015]寻宝游戏 题解 发现每次答案就是把虚树上的路径*2 接在同一关键点上的点的dfs序是相邻的 那么用set动态维护dfs序 ...

- bzoj 4737: 组合数问题

Description 组合数C(n,m)表示的是从n个物品中选出m个物品的方案数.举个例子,从(1,2,3)三个物品中选择两个物品可以有( 1,2),(1,3),(2,3)这三种选择方法.根据组合数 ...

- 【洛谷】3960:列队【Splay】

P3960 列队 题目描述 Sylvia 是一个热爱学习的女孩子. 前段时间,Sylvia 参加了学校的军训.众所周知,军训的时候需要站方阵. Sylvia 所在的方阵中有n×m名学生,方阵的行数为 ...