vivado 创建PL工程

参考来源

https://china.xilinx.com/video/hardware/i-and-o-planning-overview.html

前言

我Win10系统上的Xilinx Platform Studio打不开,无奈之下换用Vivado。这篇粗略地介绍Vivado创建FPGA工程的流程

使用Vivado

新建工程

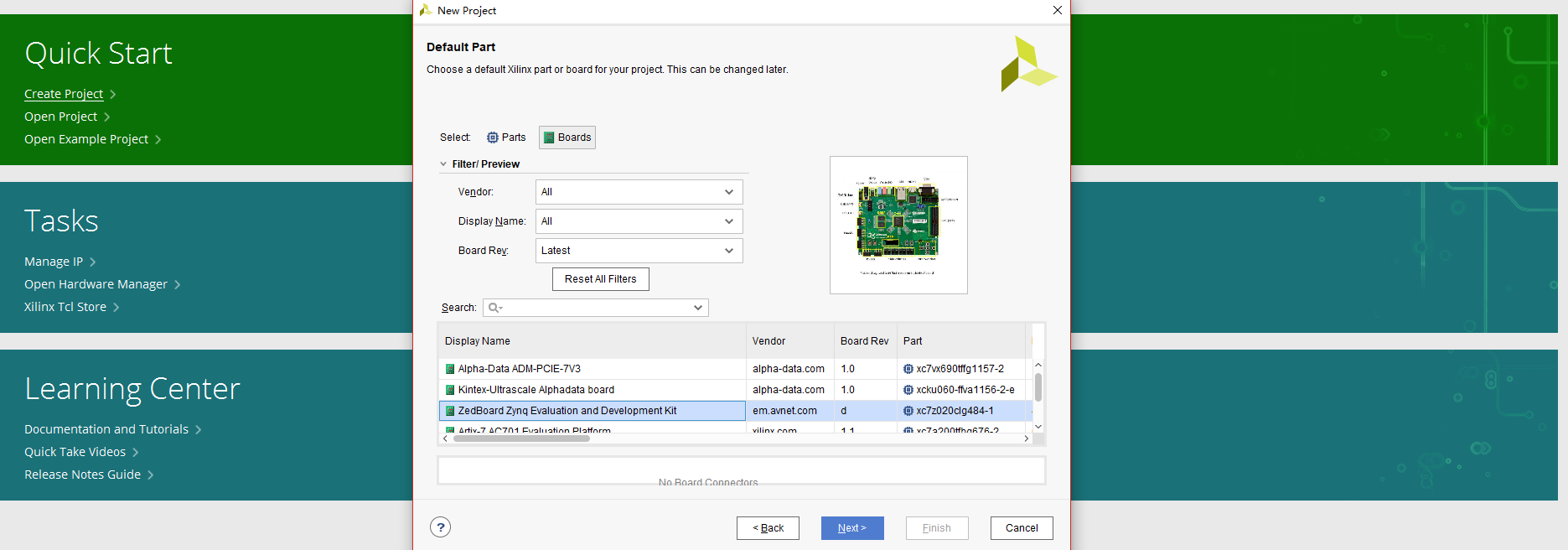

打开vivado,点New Project然后Create a New Vivado Project点next再填写工程名、工程路径点next

在Project Type选择 RTL 工程,单击 NEXT

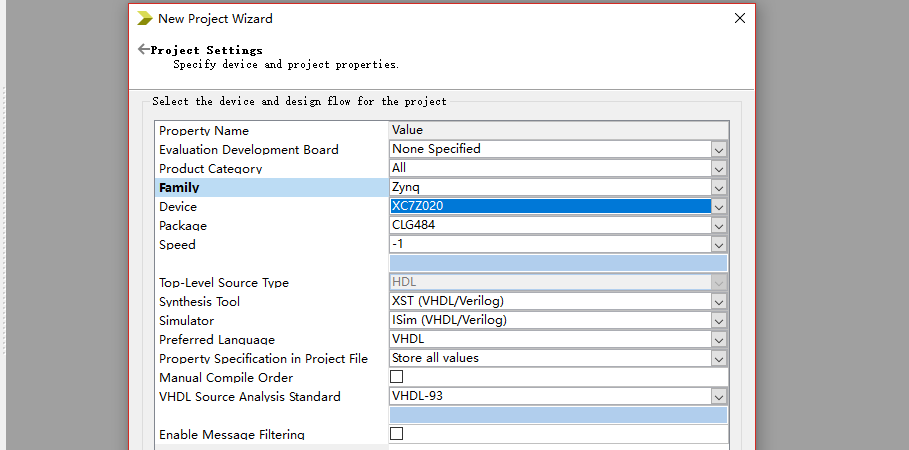

选择板子,我的是Zedboard,然后next-finish

设计输入

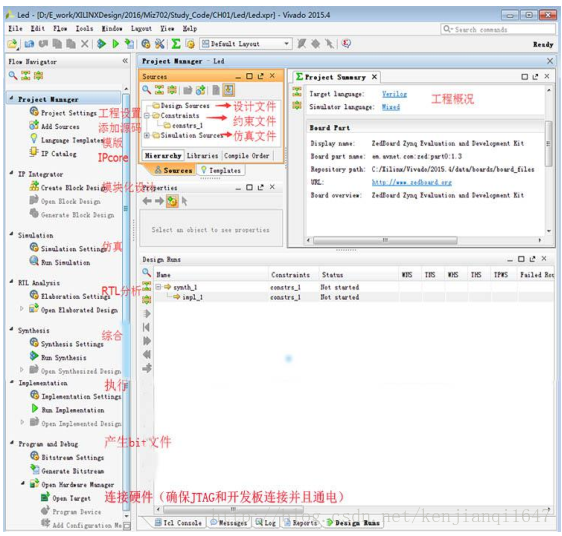

界面如下,图片来源https://blog.csdn.net/kenjianqi1647/article/details/79199657

代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Flowing LED

-- 先分频再移位

entity LED is

port(

GCLK,BTNU:in std_logic;

LDS:out std_logic_vector(7 downto 0)

);

end LED;

architecture Behavioral of LED is

-- 计数

signal count:std_logic_vector(25 downto 0);

signal clk_temp:std_logic;

signal LDS_temp:std_logic_vector(7 downto 0):="00000001";

begin

process(GCLK,BTNU)

--分频系数

variable N :std_logic_vector(25 downto 0):="10111110101111000010000000";

begin

if BTNU='1' then

count<="00000000000000000000000001";

clk_temp<='1';

elsif (GCLK'EVENT and GCLK='1')then

if (count=N)then

count<="00000000000000000000000001";

clk_temp<='1';

else

count<=count+1;

clk_temp<='0';

end if;

end if;

end process;

--得到的clk_temp为2Hz,占空比1/50000000

process(clk_temp,BTNU)

begin

if BTNU='1' then

LDS_temp<="00000001";

elsif (clk_temp'EVENT and clk_temp='1')then

LDS_temp(0)<=LDS_temp(7);

LDS_temp(7 downto 1)<=LDS_temp(6 downto 0);

end if;

end process;

LDS<=LDS_temp;

end Behavioral;

引脚约束

NET "BTNU" IOSTANDARD = LVCMOS18;

NET "GCLK" IOSTANDARD = LVCMOS33;

NET "BTNU" LOC = T18;

NET "GCLK" LOC = Y9;

NET "LDS[7]" LOC = U14;

NET "LDS[6]" LOC = U19;

NET "LDS[5]" LOC = W22;

NET "LDS[4]" LOC = V22;

NET "LDS[3]" LOC = U21;

NET "LDS[2]" LOC = U22;

NET "LDS[0]" LOC = T22;

NET "LDS[1]" LOC = T21;

# PlanAhead Generated IO constraints

NET "LDS[7]" IOSTANDARD = LVCMOS33;

NET "LDS[6]" IOSTANDARD = LVCMOS33;

NET "LDS[5]" IOSTANDARD = LVCMOS33;

NET "LDS[4]" IOSTANDARD = LVCMOS33;

NET "LDS[3]" IOSTANDARD = LVCMOS33;

NET "LDS[2]" IOSTANDARD = LVCMOS33;

NET "LDS[1]" IOSTANDARD = LVCMOS33;

NET "LDS[0]" IOSTANDARD = LVCMOS33;

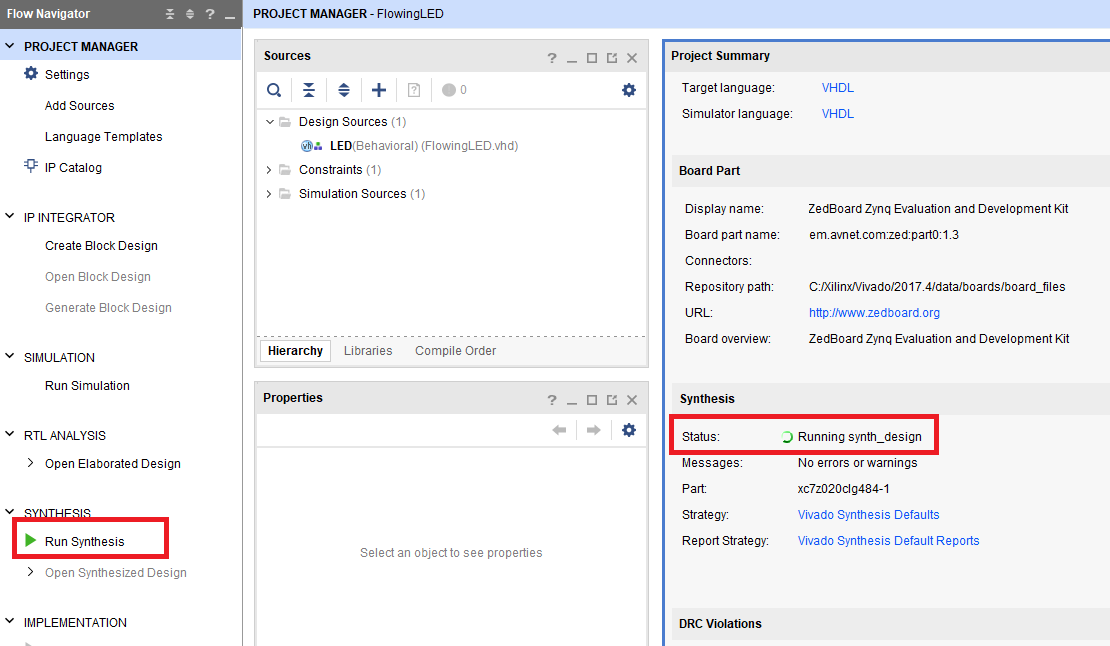

设计综合

设计综合过程会完成语法检查,编译,映射等步骤

点击Run Synthesis,可以在Project Summary 查看状态

综合完毕后

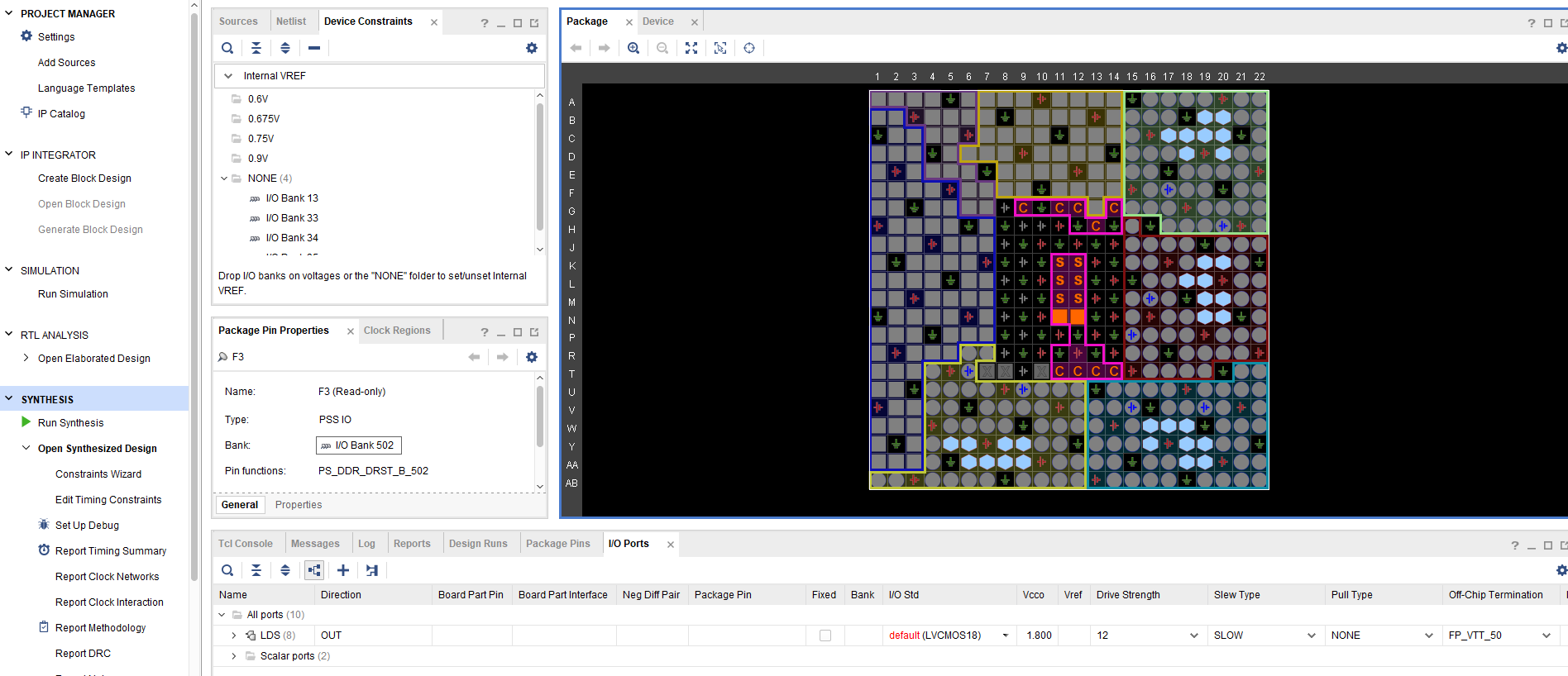

点击open synthesized design打开synthesized design,此时点击菜单栏的window-I/O ports 即可规划管脚。点击菜单栏Layout-I/O planning打开Package

设计实现

点击Run Implementation,完成后点击Generate Bitstream,生成比特文件

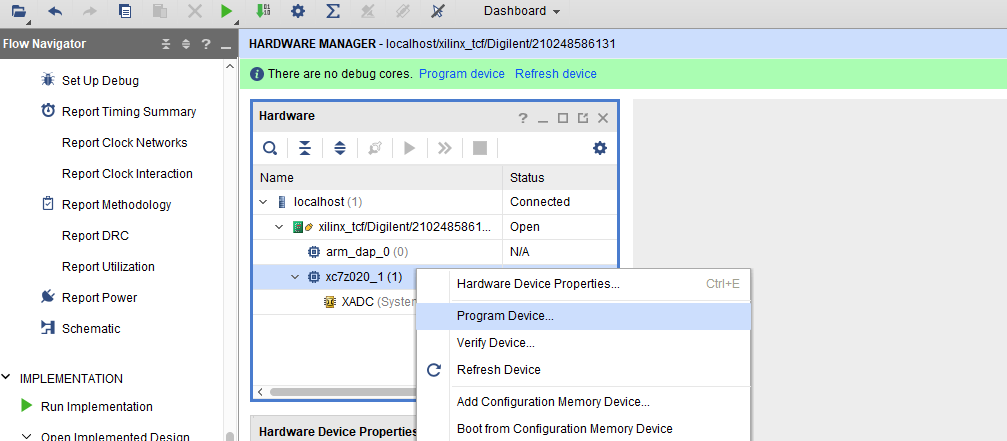

下载执行

将开发板通电并连接到电脑,点击Hardware Manager ,在fpga芯片上右键program,

现象

8个LED从右到左流水点亮,如果按BTNU从LED0开始重新流水点亮

使用ISE

流程:创建工程、设计输入、引脚约束、设计综合、设计实现、生成比特文件、下载执行

开发工具

ISE

硬件连接

Zedboard 的8个LED共阴极,置高电平点亮

100MHz时钟源接入GCLK引脚

BTNU按钮按下时是高电平,可用于高电平复位

器件属性配置

代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Flowing LED

-- 先分频再移位

entity LED is

port(

GCLK,BTNU:in std_logic;

LDS:out std_logic_vector(7 downto 0)

);

end LED;

architecture Behavioral of LED is

-- 计数

signal count:std_logic_vector(25 downto 0);

signal clk_temp:std_logic;

signal LDS_temp:std_logic_vector(7 downto 0):="00000001";

begin

process(GCLK,BTNU)

--分频系数

variable N :std_logic_vector(25 downto 0):="10111110101111000010000000";

begin

if BTNU='1' then

count<="00000000000000000000000001";

clk_temp<='1';

elsif (GCLK'EVENT and GCLK='1')then

if (count=N)then

count<="00000000000000000000000001";

clk_temp<='1';

else

count<=count+1;

clk_temp<='0';

end if;

end if;

end process;

--得到的clk_temp为2Hz,占空比1/50000000

process(clk_temp,BTNU)

begin

if BTNU='1' then

LDS_temp<="00000001";

elsif (clk_temp'EVENT and clk_temp='1')then

LDS_temp(0)<=LDS_temp(7);

LDS_temp(7 downto 1)<=LDS_temp(6 downto 0);

end if;

end process;

LDS<=LDS_temp;

end Behavioral;

引脚约束

NET "BTNU" IOSTANDARD = LVCMOS18;

NET "GCLK" IOSTANDARD = LVCMOS33;

NET "BTNU" LOC = T18;

NET "GCLK" LOC = Y9;

NET "LDS[7]" LOC = U14;

NET "LDS[6]" LOC = U19;

NET "LDS[5]" LOC = W22;

NET "LDS[4]" LOC = V22;

NET "LDS[3]" LOC = U21;

NET "LDS[2]" LOC = U22;

NET "LDS[0]" LOC = T22;

NET "LDS[1]" LOC = T21;

# PlanAhead Generated IO constraints

NET "LDS[7]" IOSTANDARD = LVCMOS33;

NET "LDS[6]" IOSTANDARD = LVCMOS33;

NET "LDS[5]" IOSTANDARD = LVCMOS33;

NET "LDS[4]" IOSTANDARD = LVCMOS33;

NET "LDS[3]" IOSTANDARD = LVCMOS33;

NET "LDS[2]" IOSTANDARD = LVCMOS33;

NET "LDS[1]" IOSTANDARD = LVCMOS33;

NET "LDS[0]" IOSTANDARD = LVCMOS33;

现象

8个LED从右到左流水点亮,如果按BTNU从LED0开始重新流水点亮

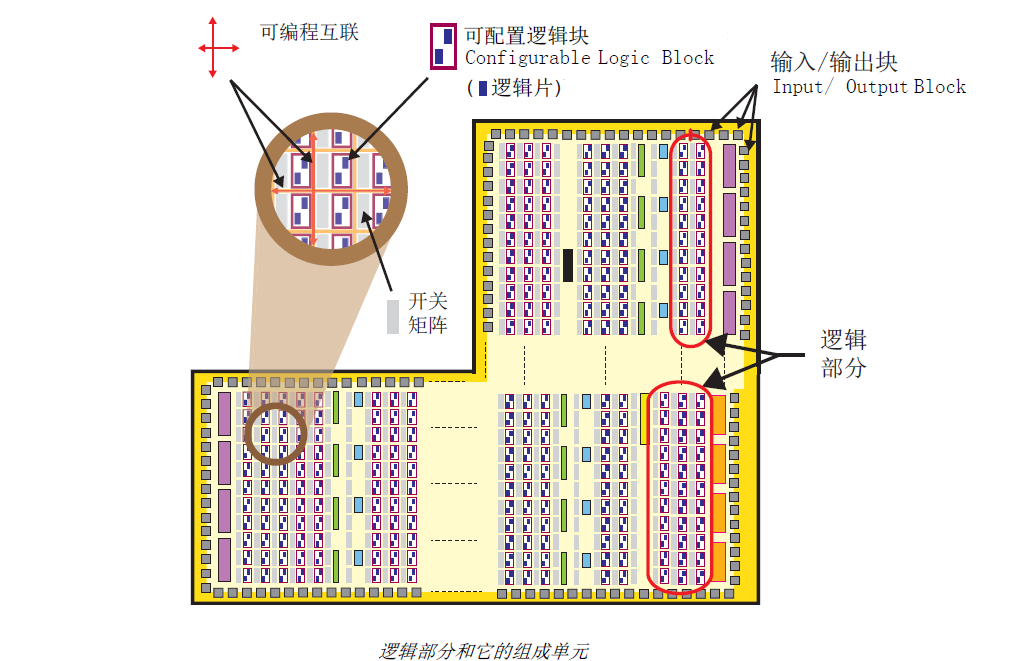

关于逻辑部分

通用FPGA逻辑部分如下所示

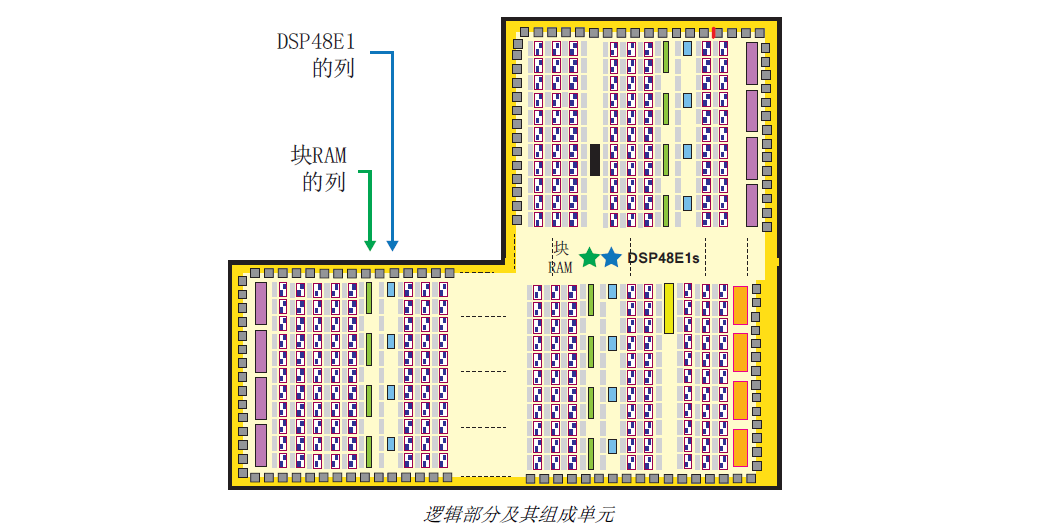

zynq的PL部分的特殊资源包括满足密集存储的块RAM和用于高速算术的DSP48E1。当然逻辑资源也可以用来搭建RAM,但是块RAM是经过优化的,使用很小的物理空间就可以存储大量数据;逻辑资源的查找表(LUT)也可以用来算术运算,但是会占用很多逻辑资源,DSP48E1是专用于长字长信号的高速算术运算的逻辑块。

其他硬IP部件

- GTX收发器实现与独立的外部芯片的连接,支持PCI Express和SATA等接口

- XDAC块,两个独立的12位ADC,采样速率达到1Msps,使用PS控制

- 独立的时钟

- JTAG实现配置和调试

vivado 创建PL工程的更多相关文章

- vivado 创建PS工程

前言 本文简要介绍在vivado中创建PS工程.单纯使用zynq芯片的PS部分就像使用普通ARM芯片一样,只是多了建立Zynq硬件系统这一个步骤.vivado创建PL工程参见此处 新建工程 与viva ...

- Vivado SDK 2014.2 创建新工程后,BSP版本不对的解决办法

问题描述如下: 1. 使用Vivado SDK 2014.2已经创建了工程,但是此时,hdf文件增加了外设,需要重新创建工程以更新SDK中的外设描述: 2. 使用新的hdf创建工程后,发现system ...

- Eclipse创建Maven工程报错

问题 用Eclipse创建maven工程的时候,总是会报错,例如提示: Unable to create project from archetype [org.apache.maven.archet ...

- MyEclipse创建Maven工程

先要在MyEclipse中对Maven进行设置:

- 关于Xcode6创建的工程在Xcode5打开

Xcode6创建的工程在Xcode5打开- 4.0只显示3.5大小的问题 只需要在工程里添加Default-568h@2x.png,即可以解决

- windows下无法创建django工程的问题

环境:python2.7 django1.7 安装好django后,将C:\Python27\Lib\site-packages\Django-1.7.7-py2.7.egg\django\bin; ...

- 在VS2015 RC打开CTP中创建的工程

VS2015终于出了RC了!小伙伴们快来安装试用吧,地址在这里,还有新的Windows 10开发工具哦,要不然是开发不了Universal Windows App的,安装前记得卸载CTP版本. 新的R ...

- iOS创建子工程

实际开发中,我们可能会同时开发好几个端,比如楼主目前开发的家教平台,需要老师端,家长端,助教端三个端.有很多工具方法,或者封装的自定义控件都是可以复用的.我们就可以把公用的代码抽取出去,新建一个工程, ...

- Myeclipse中创建Maven工程的时候没有 webapp-javaee6

1. http://mvnrepository.com/artifact/org.codehaus.mojo.archetypes/webapp-javaee6/1.5 中有描述

随机推荐

- CPanel/服务器文件及目录

cPanel服务器默认的各主要目录及配置文件的路径.cPanel服务器很多配置文件的路径和通常情况下安装LAMP的不同,另外还有很多是属于cPanel面板自己的配置文件. 目录 1 Apache 2 ...

- HTTPclient 4.2.2 传参数和文件流

package com.http; import java.io.File; import java.io.IOException; import java.io.UnsupportedEncodin ...

- 通过阿里云命令行工具 aliyuncli 购买服务器

开始想通过 aliyuncli 的 golang 源码进行编译安装(注:python 版的 aliyuncli 已不再维护),但没成功,详见 通过 golang 源码编译阿里云命令行工具 aliyun ...

- ZOJ 4062 - Plants vs. Zombies - [二分+贪心][2018 ACM-ICPC Asia Qingdao Regional Problem E]

题目链接:http://acm.zju.edu.cn/onlinejudge/showProblem.do?problemCode=4062 题意: 现在在一条 $x$ 轴上玩植物大战僵尸,有 $n$ ...

- LeetCode 19 - 删除链表的倒数第N个节点 - [链表]

题目链接:https://leetcode-cn.com/problems/remove-nth-node-from-end-of-list/ 题解: 两个 $p,q$ 指针均指向头,然后 $q$ 先 ...

- 4、 LwIP协议栈规范翻译——流程模型

4.流程模型 协议实现的流程模型描述了系统被划分为不同的流程的方式.用于实现通信协议的一个流程模型是让每个协议作为一个独立的进程运行.有了这个模型,严格的协议分层被强制执行,并且协议之间的通信点必须严 ...

- 006-mac下finder操作

1. 在 Finder 窗口显示更多信息 打开任意 Finder 窗口.前往并打开「显示」-「显示路径栏」.「显示」-「显示状态栏」和「显示」-「显示预览」三项. 选择了显示路径栏 路径栏通常是从磁盘 ...

- java框架之SpringCloud(1)-微服务及SpringCloud介绍

微服务概述 是什么 业界大牛 Martin Fowler 这样描述微服务: 参考[微服务(Microservices)-微服务原作者Martin Flower博客翻译]. 下面是关于上述博客中的部分重 ...

- Cartographer源码阅读(5):PoseGraph位姿图

PoseGraph位姿图 mapping2D::PoseGraph类的注释: // Implements the loop closure method called Sparse Pose Adju ...

- GitHub学习总结

一.安装git:下载Git,官网地址:https://git-scm.com/,进入官网首页,然后点击download,下载对应系统的git就行. 二.我用的是win系统,打开git界面是这样的: 在 ...