Verilog 加法器和减法器(1)

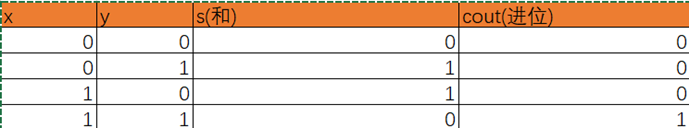

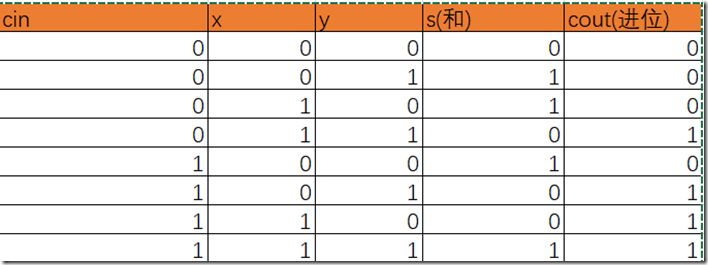

两个一位的二进制数x,y相加,假设和为s,进位为cout,其真值表为:

从真值表中,我们可以得到:s = x^y, cout = x&y,实现两个一位数相加的逻辑电路称为半加器。

实现该电路的verilog代码如下:

module halfadd(x,y,s,cout); input x;

input y; output s;

output cout; assign s = x^y;

assign cout = x&y; endmodule

相对应的testbench文件如下代码。在代码中,我们采用系统函数$random来产生随机激励。半加器电路中并没有使用时钟,但在testbench中,产生了时钟信号,主要是为了功能验证时候,有一个时间单位信号,便于检查结果。

`timescale 1ns/1ns

`define clock_period 20 module halfadd_tb;

reg x,y; wire cout;

wire s;

reg clk; halfadd halfadd_0(

.x(x),

.y(y),

.s(s),

.cout(cout)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

#(`clock_period*20)

$stop;

end endmodule

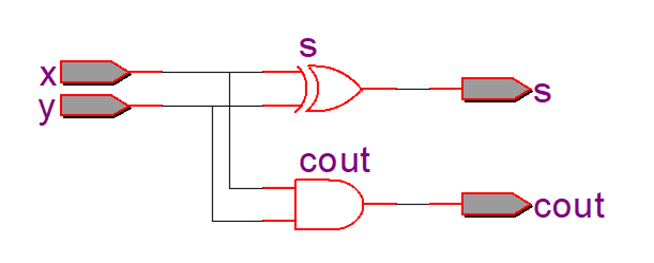

在quartus II中,分析与综合后,用rtl view 可以得到 halfadd的电路如下,和我们预想的一样。

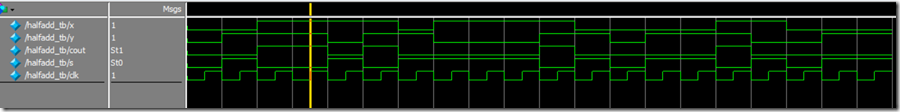

功能仿真结果如下,从波形中可以看到结果正确。

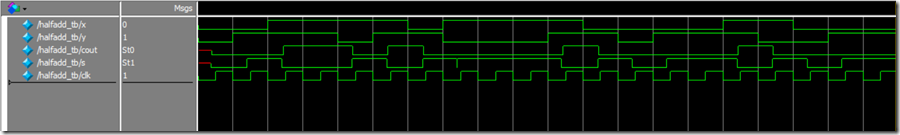

全编译后,在Cyclone IV E-EP4CE10F17C8中的门级仿真结果如下,输入和输出之间,会有几ns的时延。

通常,我们更感兴趣的是多位二进制数的相加,在多位二进制数相加时,对每一位而言,除了考虑相加的两位数(第i位),还要考虑来自低位(i-1位)的进位。实现带低位进位的两个一位数相加的逻辑电路,称为全加器。

它的真值表如下:

从真值表中,我们可以得知:s = ~x & y & ~cin + x&~y&~cin+~x&~y&cin+x&y&cin = (~x&y+x&~y)&~cin+(~x&~y+x&y)&cin=(x^y)&~cin+~(x^y)&cin=x^y^cin,

这儿我们用~表示非,+表示或。cout = x&y+x&cin+y&cin

全加器verilog代码如下:

module fulladd(cin,x,y,s,cout); input cin;

input x;

input y; output s;

output cout; assign s = x^y^cin;

assign cout = (x&y)|(x&cin)|(y&cin); endmodule

对应的testbench代码如下:

`timescale 1ns/1ns

`define clock_period 20 module fulladd_tb;

reg cin,x,y; wire cout;

wire s;

reg clk; fulladd fulladd_0(

.cin(cin),

.x(x),

.y(y),

.s(s),

.cout(cout)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

cin = 0;

repeat(2)

#(`clock_period*10) cin = {$random}; end initial begin

#(`clock_period*20)

$stop;

end endmodule

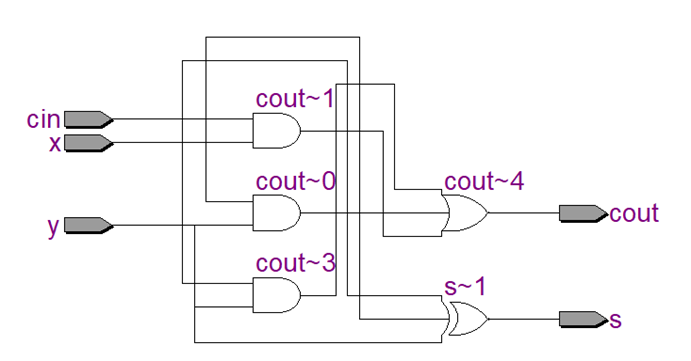

从rtl view中,可以看到全加器逻辑电路图如下:包括3个与门,一个三输入的异或门,一个三输入的或门。

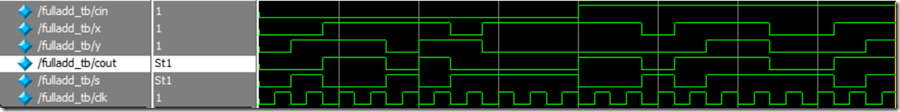

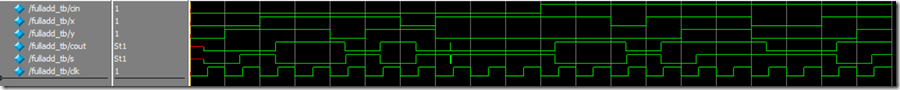

功能仿真和门级仿真的波形如下,信号符合预期。

Verilog 加法器和减法器(1)的更多相关文章

- Verilog 加法器和减法器(8)-串行加法器

如果对速度要求不高,我们也可以使用串行加法器.下面通过状态机来实现串行加法器的功能. 设A=an-1an-2-a0, B=bn-1bn-2-b0,是要相加的两个无符号数,相加的和为:sum=sn-1s ...

- Verilog 加法器和减法器(4)

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作. 比如下图是4位二进制减法逻辑电路图. 8位二进制减法的verilog代码如下: module subn(x, y, d,cin) ...

- Verilog 加法器和减法器(7)

在计算机中浮点数 表示通常采用IEEE754规定的格式,具体参考以下文章. https://www.cnblogs.com/mikewolf2002/p/10095995.html 下面我们在Veri ...

- Verilog 加法器和减法器(6)

为了减小行波进位加法器中进位传播延迟的影响,可以尝试在每一级中快速计算进位,如果能在较短时间完成计算,则可以提高加法器性能. 我们可以进行如下的推导: 设 gi=xi&yi, pi = xi ...

- Verilog 加法器和减法器(3)

手工加法运算时候,我们都是从最低位的数字开始,逐位相加,直到最高位.如果第i位产生进位,就把该位作为第i+1位输入.同样的,在逻辑电路中,我们可以把一位全加器串联起来,实现多位加法,比如下面的四位加法 ...

- Verilog 加法器和减法器(2)

类似半加器和全加器,也有半减器和全减器. 半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位.它们的真值表如下: 对半减器,diff = x ^y, ...

- Verilog 加法器和减法器(5)

前面二进制加法运算,我们并没有提操作数是有符号数,还是无符号数.其实前面的二进制加法对于有符号数和无符号数都成立.比如前面的8位二进制加法运算,第一张图我们选radix是unsigned,表示无符号加 ...

- 基于Xilinx的Synthesize

所谓综合.就是讲HDL语言.原理图等设计输入翻译成由与.或.非们和RAM.触发器登记本逻辑单元的逻辑连接(即网表).并依据目标和要求(约束条件)优化生成的逻辑连接. ISE-XST XST是Xilin ...

- FPGA综合工具--Synplify Pro的常用选项及命令

最近要用到Synplify,但以前没使用过,无基础,找到一篇帖子,隧保存下来. 本文转自:http://blog.sina.com.cn/s/blog_65fe490d0100v8ax.html Sy ...

随机推荐

- [js]BOM篇

一.什么是BOM BOM(Browser Object Model)即浏览器对象模型. BOM提供了独立于内容 而与浏览器窗口进行交互的对象: 由于BOM主要用于管理窗口与窗口之间的通讯,因此其核心对 ...

- csp刷题

title: csp刷题 date: 2018-12-13 16:41:33 tags: --- Markdown 在第7个点挂了,,,不改了,,,太恶心了这种题QAQ,,,, 有谁想改的改完了告诉我 ...

- Android Socket

Android Socket 参考资料 菜鸟教程 怎么理解TCP的面向连接和UDP的无连接 https://www.cnblogs.com/xiaomayizoe/p/5258754.html htt ...

- Oracle数据库11gR2的卸载 - deinstall

从Oracle 11gR2开始,Oracle推荐使用deinstall来卸载Oracle数据库.使用Oracle Universal Install(OUI) 的图形方式来卸载Oracle数据库软件了 ...

- VMware虚拟机中CentOS设置固定IP

因为需要配置固定IP,在网上找了很久终于找到一个可行的例子,自己配置成功了. 1.首先获取你的GATEWAY 方便后面在cento系统配置里使用选取菜单栏:Edit->Virtual Netwo ...

- [USACO08OCT]Watering Hole

[USACO08OCT]Watering Hole 题目大意: Farmer John 有\(n(n\le300)\)个牧场,他希望灌溉他的所有牧场.牧场编号为\(1\sim n\),要灌溉一个牧场有 ...

- hdu 4451 37届金华赛区 J题

题意:给出衣服裤子鞋子的数目,有一些衣服和裤子,裤子和鞋子不能搭配,求最终的搭配方案总数 wa点很多,我写wa了很多次,代码能力需要进一步提升 #include<cstdio> #incl ...

- 使用MFC做一个简单的‘能自动生成小学生四则运算的软件’

这是软件工程的第一次作业!但由于我们python还没入门,所以这次的要求是‘语言不限’. 小学期做过一个关于MFC的‘资金管理系统’,也正好可以有界面,所以就选择了自己很熟悉的MFC来做这个作业! 1 ...

- (67)Wangdao.com第十一天_JavaScript 数组的遍历

for 普通方式遍历 var arr = [0,1,2,3,4,5,6]; for(i=0; i<arr.length; i++){ document.write("["+i ...

- A brief CRC tutorial

https://www.kernel.org/doc/Documentation/crc32.txt A brief CRC tutorial. A CRC is a long-division re ...