am335x system upgrade kernel ethernet(四)

1 Scope of Document

This document describes ethernet hardware design and porting KZS8081 to uboot and kernel

2 Requiremen

2.1 Function Requirement

Use KZS8081 in am335x, user space use network interface

2.2 Performance Requirement

Support Highest Link-Up Speed( 10/100 Mbps )

3 Hardware Overview

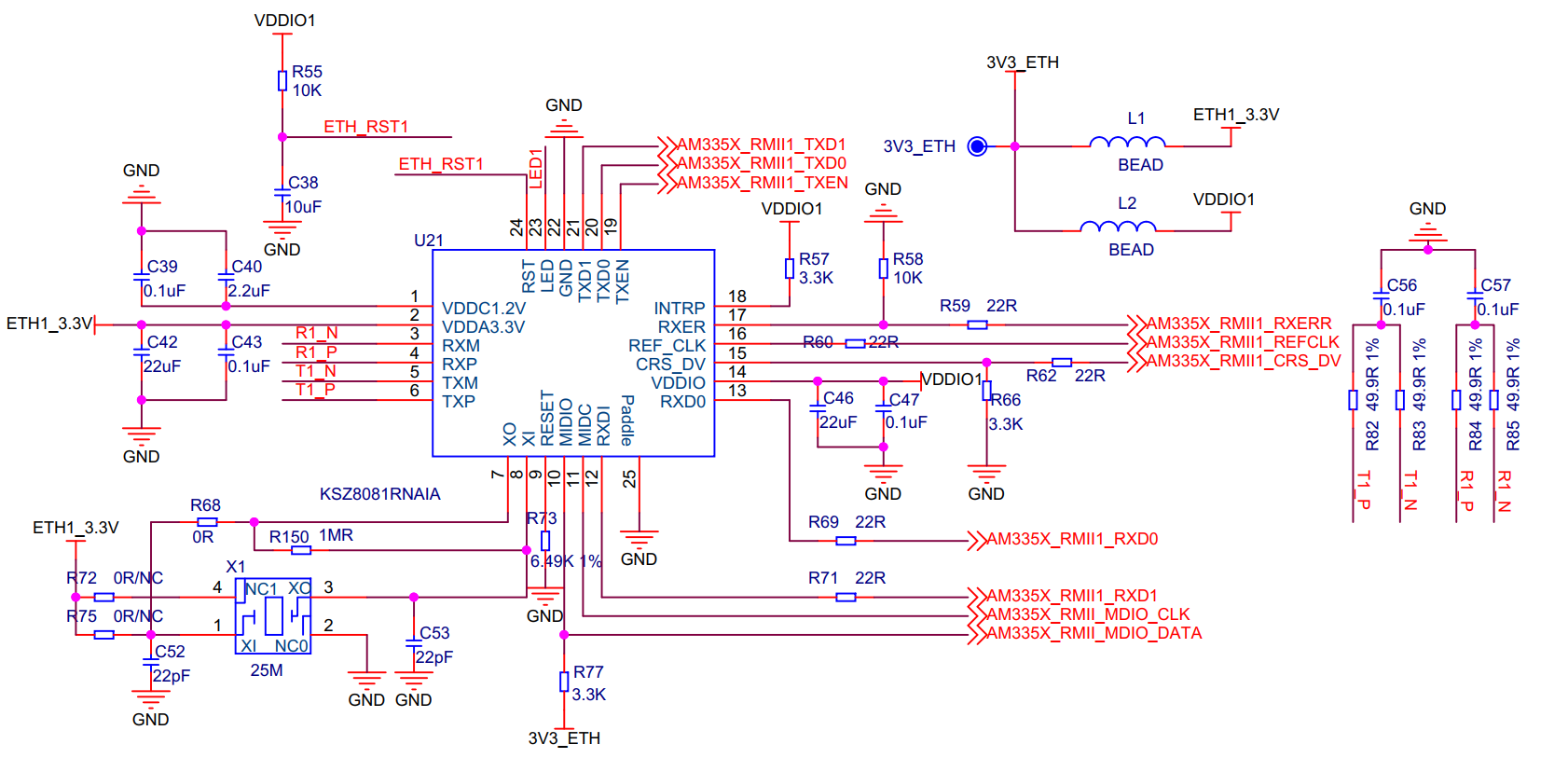

ethernet interface,pin map:

// send signal

AM335X_RMII1_TXD1 -------------MII1_TXD1

AM335X_RMII1_TXD0 -------------MII1_TXD0

AM335X_RMII1_TXEN -------------MII1_TXEN

// receive signal

AM335X_RMII1_RXD0 -------------MII1_RXD0

AM335X_RMII1_RXD1 -------------MII1_RXD1

AM335X_RMII1_RXERR ---------------MII1_RXERR

AM335X_RMII1_REFCLK --------------MII1_REFCLK

// relate with phy addr

AM335X_RMII1_CRS_DV-------------RMII1_CRS

// control signal

AM335X_RMII1_MDIO_CLK -------------MDIO_CLK

AM335X_RMII1_MDIO_DATA------------MDIO_DATA

Figure 1 ethernet interface block diagram

4 Functional Description

4.1 Functional Block Diagram

Figure 2 EMAC connect to KSZ8081 phy

AM335X EMAC module connect to KSZ8081 phy

4.2 mdio bus specification

4.2.1 Overview

Most network devices are connected to a PHY by means of a management bus.Different devices use different busses (though some share common interfaces).

The MDIO interface is implemented by two signals:

MDC clock: driven by the MAC device to the PHY.

MDIO data: bidirectional, the PHY drives it to provide register data at the end of a read operation.

The bus only supports a single MAC as the master, and can have up to 32 PHY slaves.

The MDC can be periodic, with a minimum period of 400 ns, which corresponds to a maximum frequency of 2.5 MHz. Newer chips, however, allow faster accesses.

The MDIO requires a specific pull-up resistor of 1.5 kΩ to 10 kΩ, taking into account the total worst-case leakage current of 32 PHYs and one MAC.

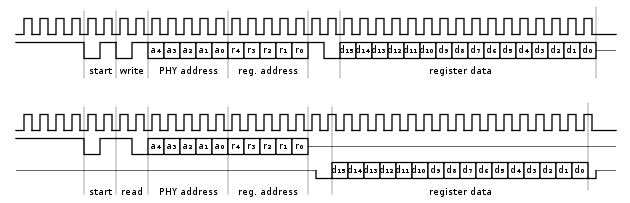

4.2.2 Bus timing

Before a register access, PHY devices generally require a preamble of 32 ones to be sent by the MAC on the MDIO line. The access consists of 16 control bits, followed by 16 data bits. The control bits consist of 2 start bits, 2 access type bits (read or write), the PHY address (5 bits), the register address (5 bits), and 2 "turnaround" bits.

During a write command, the MAC provides address and data. For a read command, the PHY takes over the MDIO line during the turnaround bit times, supplies the MAC with the register data requested, then releases the MDIO line.

When the MAC drives the MDIO line, it has to guarantee a stable value 10 ns (setup time) before the rising edge of the clock MDC. Further, MDIO has to remain stable 10 ns (hold time) after the rising edge of MDC.

When the PHY drives the MDIO line, the PHY has to provide the MDIO signal between 0 and 300 ns after the rising edge of the clock. Hence, with a minimum clock period of 400 ns (2.5 MHz maximum clock rate) the MAC can safely sample MDIO during the second half of the low cycle of the clock.

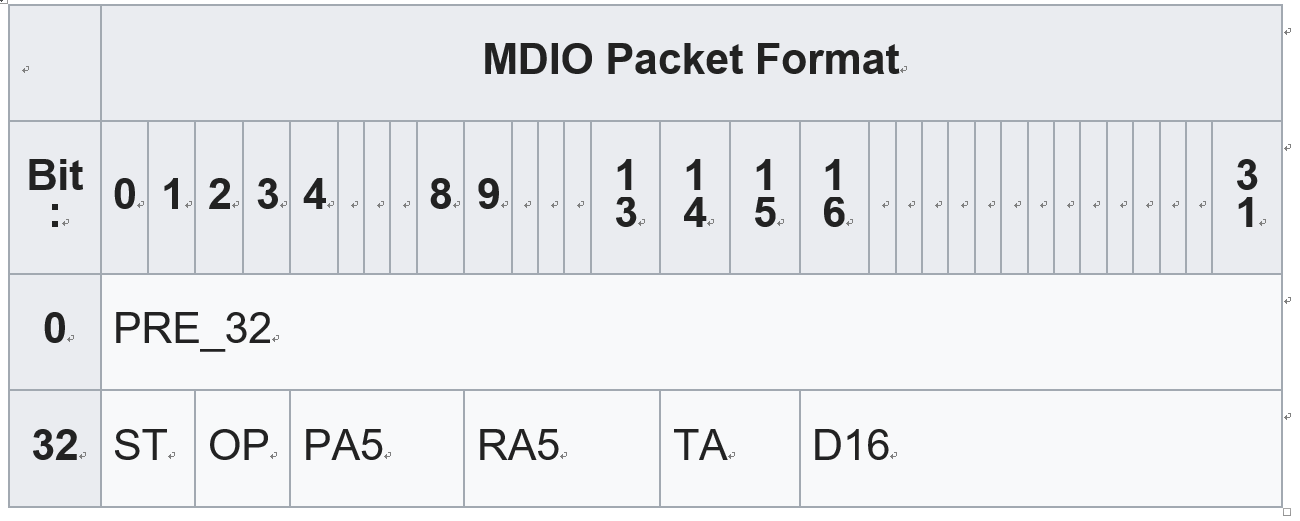

4.2.3 MDIO Packet Format

PRE_32

The first field in the MDIO header is the Preamble. During the preamble, the MAC sends 32 bits, all '1', on the MDIO line.

ST

The Start field consists of 2 bits and always contains the combination '01'.

OP

The Opcode consists of 2 bits. There are two possible opcodes, read '10' or write '01'.

PA5

5 bits, PHY address.

RA5

The Register Address field indicates the register to be written to or read from. It is 5 bits long.

TA

The turn-around field is 2 bits long. When data is being written to the PHY, the MAC writes '10' to the MDIO line. When data is being read, the MAC releases the MDIO line.

D16

16 bits, data. This can be sent by either the SME or the PHY, depending on the value of the OP field.

Z

Tristate MDIO.

5 Porting

5.1 Uboot porting

NA

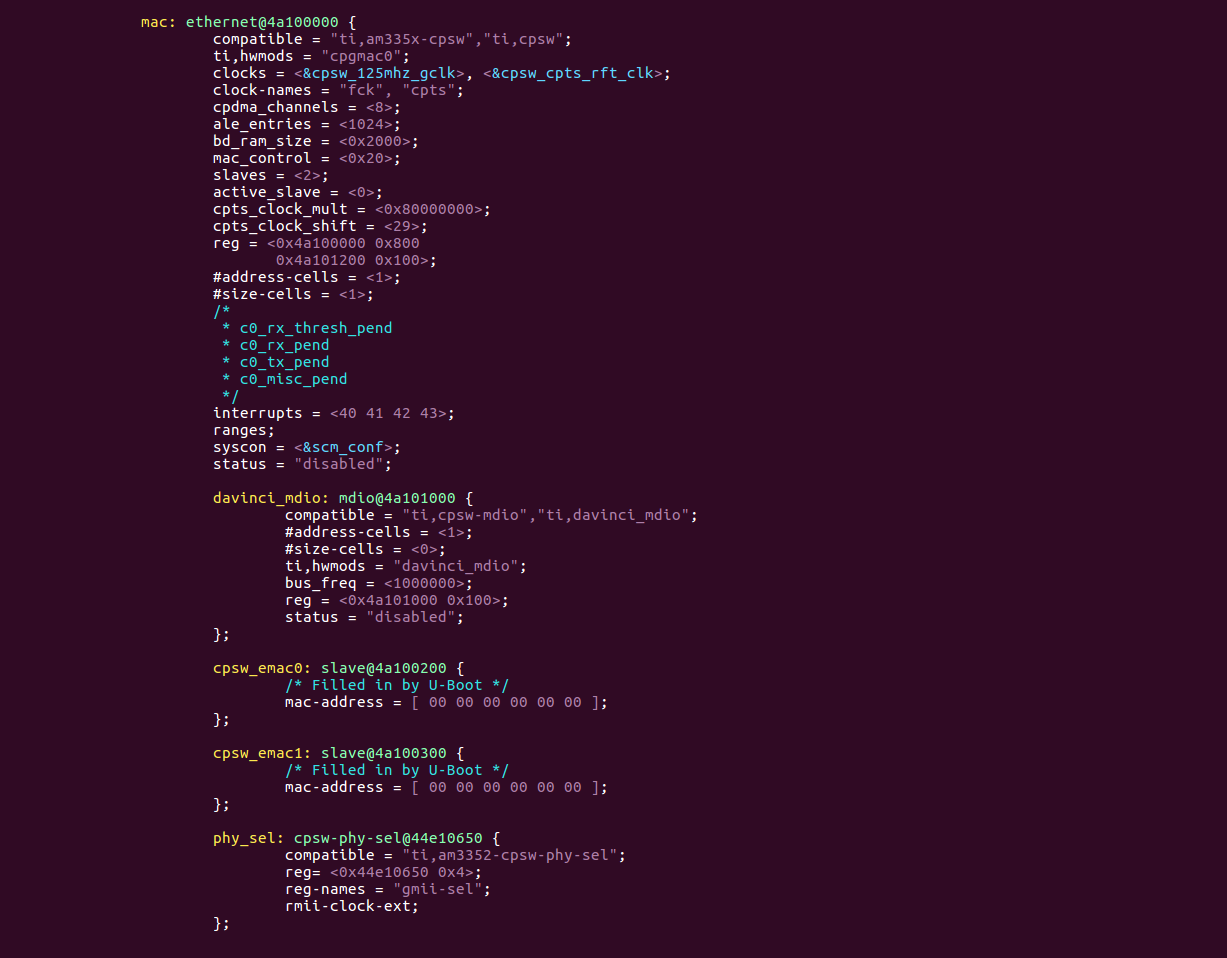

5.2 Kernel porting

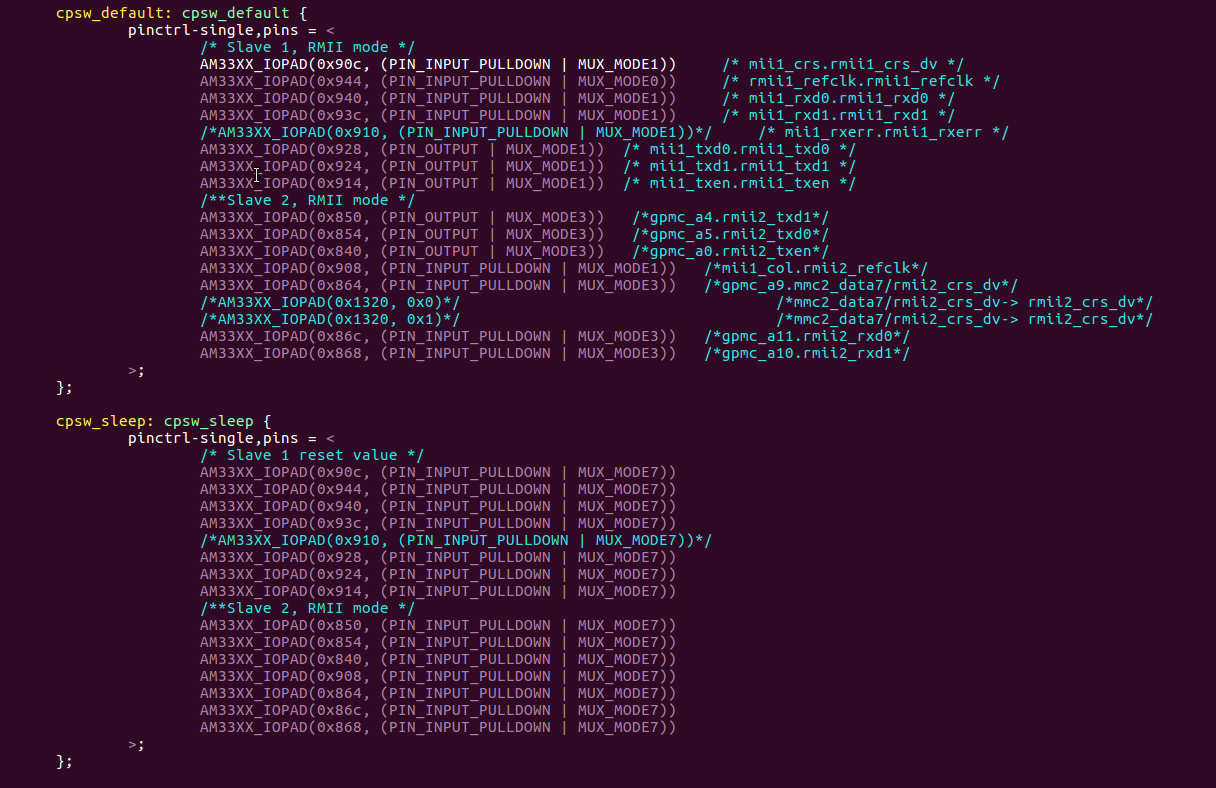

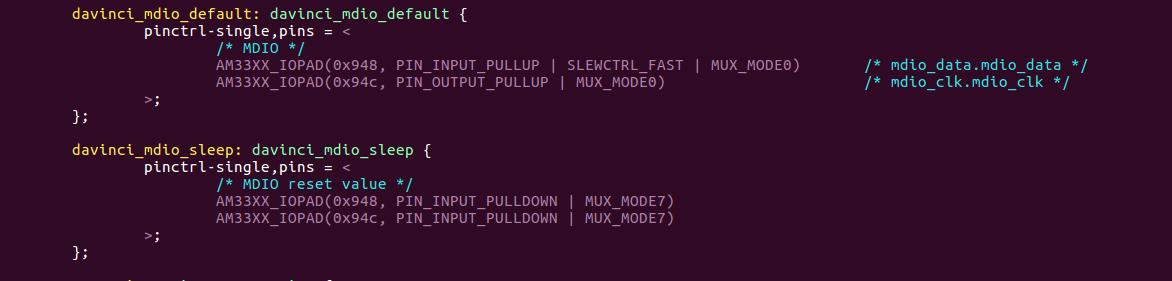

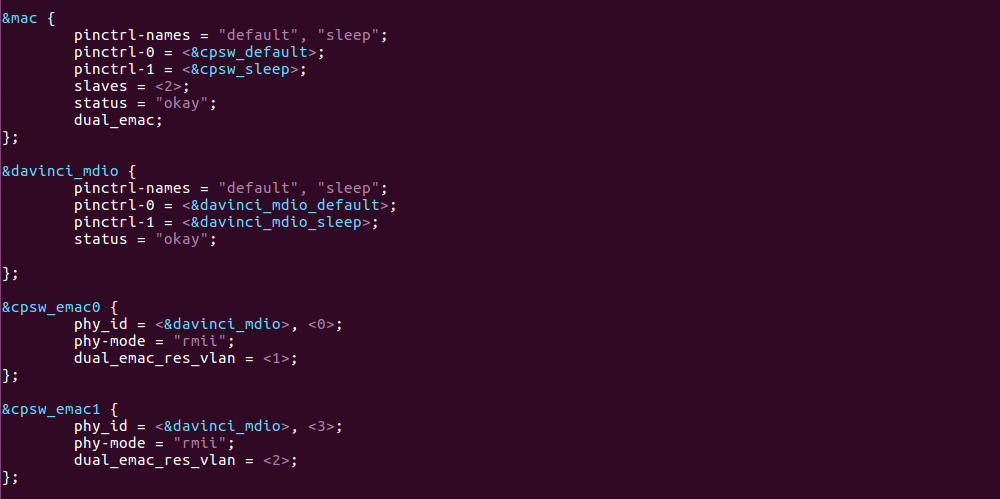

am335x.dtsi

am335x-evm.dts

In the new kernel version,we need to change the dts file, to do the pin mux, register phy id , phy connect mode. Then it will work well.

kernel log:

[ 21.514107] Micrel KSZ8081 or KSZ8091 4a101000.mdio:00: attached PHY driver [Micrel KSZ8081 or KSZ8091] (mii_bus:phy_addr=4a101000.mdio:00, irq=POLL)

[ 21.690932] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

[ 21.816198] net eth1: initializing cpsw version 1.12 (0)

[ 21.994187] Micrel KSZ8081 or KSZ8091 4a101000.mdio:03: attached PHY driver [Micrel KSZ8081 or KSZ8091] (mii_bus:phy_addr=4a101000.mdio:03, irq=POLL)

[ 22.106839] IPv6: ADDRCONF(NETDEV_UP): eth1: link is not ready

5.3 Application Interface

The net device interface eth0 eth1

6 Summary

In the KSZ8081 datasheet we can find 32 registers map, the 32 registers is the standard register.

We can ask ourself some question:

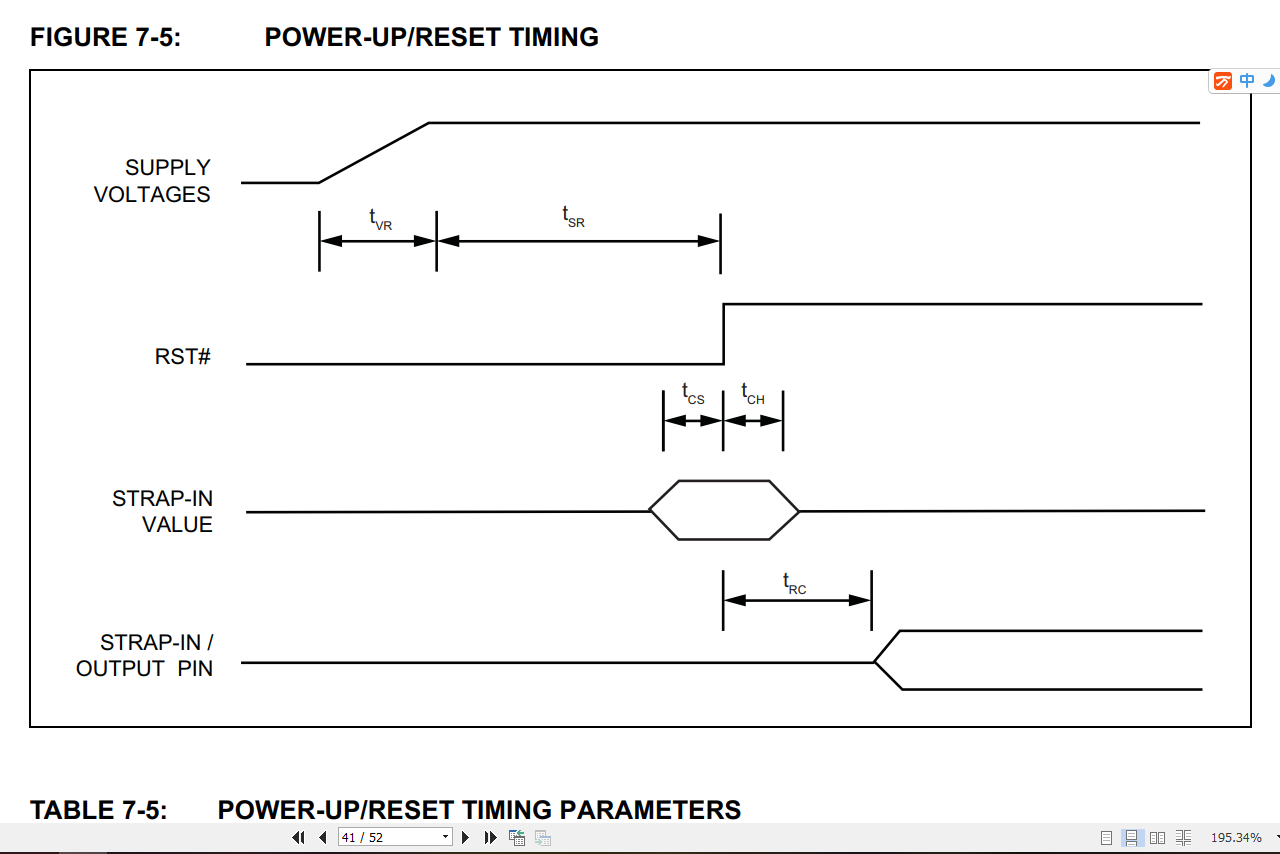

1.How to reset phy?

Reset phy can use gpio base on phy datasheet,such as

2. how to know the phy id?

In phy datasheet we can find our answer.

3. how to cominicate with phy?

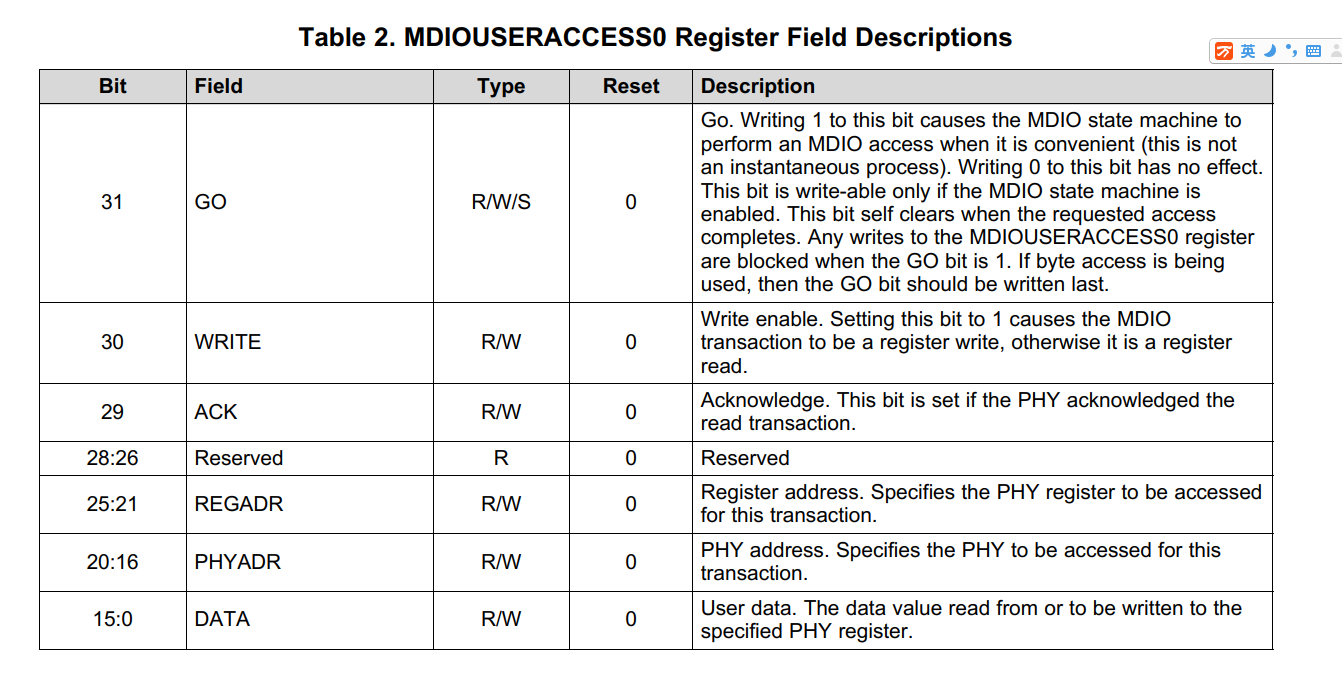

Use rmii interface, in the am335x datasheet we can use USERACCESS0/1 register to control rmi interface.

Reading PHY and writing to PHY through the USERACCESS0/1 register using memory browser or

registers window in Code Composer Studio™ is a

effective field-debug feature to troubleshoot PHY issues

(see Table 2).

Table

2. MDIOUSERACCESS0 Register Field Descriptions

Bit Field Type Reset Description

To read PHY in the memory browser or registers window, follow these steps:

1. Ensure the GO bit in the MDIO user access register (MDIOUSERACCESSn) is

cleared.

2. Write to the GO, REGADR, and PHYADR bits in MDIOUSERACCESSn corresponding to

the PHY and

PHY register to be read.

3. The read data value is available in the DATA bits in MDIOUSERACCESSn after

the module completes

the read operation on the serial bus. Completion of the read operation can be

determined by polling

the GO and ACK bits in MDIOUSERACCESSn. When the GO bit clears, the ACK bit is

set on a

successful read.

To write PHY in the memory browser or registers window, follow these steps:

1. Ensure the GO bit in the MDIO user access register (MDIOUSERACCESSn) is

cleared.

2. Write to the GO, WRITE, REGADR, PHYADR, and DATA bits in MDIOUSERACCESSn

corresponding

to the PHY and PHY register you want to write.

3. The write operation to the PHY is scheduled and completed by the MDIO

module. Completion of the

write operation can be determined by polling the GO bit in MDIOUSERACCESSn for

a 0.

4. how to init phy?

• Connection speed, duplex, and auto-negotiation

•

Auto-MDIX, which determines if a straight or crossover cable is used to connect

to the link partner.

•

Extended full-duplex mode. In extended full-duplex mode, when the PHY is set to

auto-negotiation or

Force

100Base-TX, and the link partner is operated in Force 100Base-TX, the link is

always full

duplex.

When disabled, the decision to work in full-duplex or half-duplex mode follows

IEEE

specification

– half duplex.

•

Detection of transmit error in odd-nibble boundary, which extends TX_EN by one

additional TX_CLK

cycle

and behaves as if TX_ER were asserted during that additional cycle.

•

Additional features like odd nibble insertion and fast link down detection

Most MDIO PHY configuration functions are integrated in the

board library of the Processor SDK

am335x system upgrade kernel ethernet(四)的更多相关文章

- am335x system upgrade kernel can(八)

1 Scope of Document This document describes can bus hardware design and can bus driver developm ...

- am335x system upgrade kernel tf(五)

1 Scope of Document This document describes TF hardware design 2 Requiremen 2.1 Functi ...

- am335x system upgrade kernel ec20 simcom7600ce(十一)

1 Scope of Document This document describes 4G hardware design, support quectel ec20 4G module/ ...

- am335x system upgrade kernel gpio(九)

1 Hardware Overview gpio interface,pin map: AM335X_I2C0_W_C----------------------MCASP0_AXR1 /* ...

- am335x system upgrade kernel uart(七)

1 Scope of Document This document describes UART hardware design, uart driver porting 2 Re ...

- am335x system upgrade kernel i2c rtc eeprom(六)

1 Scope of Document This document describes i2c bus hardware design and support i2c-devices: ee ...

- am335x system upgrade uboot ethernet(二)

系统可以通过SD卡引道之后,为了之后了调试方便 通过查看网卡的硬件设计 正常来说需要注意的有如下几点: 1) 网口 的接线方式: RMII 2) 网口的PHY地址两张网口,这里我们只需先初始化一张网卡 ...

- am335x system upgrade kernel usb stroage(十)

1 Scope of Document This document describes USB hardware design, support stardard usb2.0 port o ...

- am335x system upgrade kernel f-ram fm25l16b(十六)

1 Scope of Document This document describes SPI F-RAM hardware design 2 Requiremen 2.1 ...

随机推荐

- Spring中的ApplicationListener的使用详解案例

本文链接:https://blog.csdn.net/u010963948/article/details/83507185 1.ApplicationContext Spring的核心,Contex ...

- TCP,UDP 通讯的helper类

使用Tcp通讯,首先要启动tcp服务端监听客户端,客户端发送消息,服务端收到消息 1.服务端代码如下 public class TcpServerTest { public async Task Be ...

- MVC运行机制[转]

原:http://www.cnblogs.com/jyan/archive/2012/06/29/2569566.html#3122335 ASP.NET是一种建立动态Web应用程序的技术.它是.NE ...

- Golang slice和map的申明和初始化

1 前言 仅供记录使用. 2 代码 /** * @Author: FB * @Description: * @File: SliceMapInit.go * @Version: 1.0.0 * @Da ...

- 2019 完美世界java面试笔试题 (含面试题解析)

本人3年开发经验.18年年底开始跑路找工作,在互联网寒冬下成功拿到阿里巴巴.今日头条.完美世界等公司offer,岗位是Java后端开发,最终选择去了完美世界. 面试了很多家公司,感觉大部分公司考察的点 ...

- selenium自学笔记---下拉框定位元素select

下拉框1.先定位select 然后在定位option city = driver.find_element_by_id("selCities_0") city.find_eleme ...

- python安装和pycharm安装与笔记

目录 计算机的基础知识 python安装和使用 pycharm安装和使用 [TOC] 计算机的基础知识 计算机是由什么组成的 cpu-----大脑 主板----身体 电源----心脏 内存----临时 ...

- MySQL数据库之互联网常用架构方案

一.数据库架构原则 高可用 高性能 一致性 扩展性 二.常见的架构方案 方案一:主备架构,只有主库提供读写服务,备库冗余作故障转移用 jdbc:mysql://vip:3306/xxdb 高可用分析: ...

- JQuery+Bootstrap 自定义全屏Loading插件

/** * 自定义Loading插件 * @param {Object} config * { * content[加载显示文本], * time[自动关闭等待时间(ms)] * } * @param ...

- Alpha_6

一. 站立式会议照片 二. 工作进展 (1) 昨天已完成的工作 a. 修改设计图的小毛病 b. 补签卡页面 c. 实现我的,我的卡包,卡片细节功能页面,并可预览 d. 已实现“番茄钟_数据统计”页面和 ...