cyc_to_led

Entity: cyc_to_led

- File: cyc_to_led.v

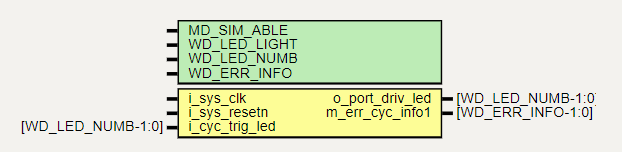

Diagram

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| MD_SIM_ABLE | 0 | sim mode enable | |

| WD_LED_LIGHT | 27 | LED light span wdith | |

| WD_LED_NUMB | 3 | led width to true LED | |

| WD_ERR_INFO | 4 | error info note |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| i_sys_clk | input | system signals | |

| i_sys_resetn | input | ||

| i_cyc_trig_led | input | [WD_LED_NUMB-1:0] | trig signal |

| o_port_driv_led | output | [WD_LED_NUMB-1:0] | led port |

| m_err_cyc_info1 | output | [WD_ERR_INFO-1:0] | error info feedback |

Signals

| Name | Type | Description |

|---|---|---|

| r_cyc_trig_led | reg [WD_LED_NUMB-1:0] | cycle signal temp one clock |

| w_cyc_trig_led_pos | wire [WD_LED_NUMB-1:0] | detect cycle signal pos edge |

| r_led_light_cnt | reg [WD_LED_LIGHT-1:0] | counter for every LED driver |

Processes

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

`timescale 1ns / 1ps

/*

Src Code

*/

// *******************************************************************************

// Company: Fpga Publish

// Engineer: FP

//

// Create Date: 2024/01/09 22:54:18

// Design Name:

// Module Name: cyc_to_led

// Project Name:

// Target Devices: ZYNQ7010 | XCZU2CG | Kintex7

// Tool Versions: 2021.1 || 2022.2

// Description:

// *

// Dependencies:

// *

// Revision: 0.01

// Revision 0.01 - File Created

// Additional Comments:

//

// *******************************************************************************

module cyc_to_led #(

//mode

parameter MD_SIM_ABLE = 0, //!sim mode enable

//number

parameter WD_LED_LIGHT = 27, //!LED light span wdith

parameter WD_LED_NUMB = 3, //!led width to true LED

//width

parameter WD_ERR_INFO = 4 //!error info note

)(

//!system signals

input i_sys_clk ,

input i_sys_resetn,

//!trig signal

input [WD_LED_NUMB-1:0] i_cyc_trig_led,

//!led port

output [WD_LED_NUMB-1:0] o_port_driv_led,

//!error info feedback

output [WD_ERR_INFO-1:0] m_err_cyc_info1

);

//========================================================

//function to math and logic

//========================================================

//localparam to converation and calculate

//========================================================

//register and wire to time sequence and combine

// ----------------------------------------------------------

// src signal solve

reg [WD_LED_NUMB-1:0] r_cyc_trig_led; //!cycle signal temp one clock

wire [WD_LED_NUMB-1:0] w_cyc_trig_led_pos;//!detect cycle signal pos edge

// ----------------------------------------------------------

// led cnt

reg [WD_LED_LIGHT-1:0] r_led_light_cnt [0:WD_LED_NUMB-1]; //!counter for every LED driver

//========================================================

//always and assign to drive logic and connect

// ----------------------------------------------------------

// src signal solve

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_cyc_trig_led <= 1'b0; //

end

else if(1) //

begin

r_cyc_trig_led <= i_cyc_trig_led; //

end

end

assign w_cyc_trig_led_pos = i_cyc_trig_led & (~r_cyc_trig_led);

// ----------------------------------------------------------

// led cnt

generate genvar i;

for(i = 0; i < WD_LED_NUMB; i = i + 1)

begin:FOR_WD_LED_NUMB

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_led_light_cnt[i] <= 1'b0; //

end

else if(w_cyc_trig_led_pos[i]) //every trig will reset counter

begin

r_led_light_cnt[i] <= 1'b0; //

end

else if(r_led_light_cnt[i][WD_LED_LIGHT-1])

begin

r_led_light_cnt[i] <= r_led_light_cnt[i];

end

else

begin

r_led_light_cnt[i] <= r_led_light_cnt[i] + 1'b1;

end

end

assign o_port_driv_led[i] = r_led_light_cnt[i][WD_LED_LIGHT-1];

end

endgenerate

//========================================================

//module and task to build part of system

//========================================================

//expand and plug-in part with version

//========================================================

//ila and vio to debug and monitor

endmodule

/*

补充说明(UTF-8)

- 基于LED监测周期信号

- 主要用于监测周期在ms级别的中断等物理信号

- 本模块暂时进行到源码设计阶段

*/

随机推荐

- 在PL/SQL中使用日期类型

在PL/SQL中使用日期类型 之前的文章介绍了在PL/SQL中使用字符串和数字了下.毫无疑问,字符串和数字很重要,但是可以确定的是没有哪个应用不依赖于日期的. 你需要记录事件的发生事件,人们的出生日期 ...

- fastjson反序列化各版本利用汇总

- win32 - 创建带有标准阴影的无边框窗口

这个框框好像删不掉,就先放这边吧... #define WIN32_LEAN_AND_MEAN #include <unknwn.h> #include <windows.h&g ...

- 【Android 逆向】【攻防世界】easyjava

1. apk 安装到手机,提示输入flag 2. jadx 打开apk看看 private static char a(String str, b bVar, a aVar) { return aVa ...

- 这样优化,0.059s 启动一个SpringBoot项目

https://mp.weixin.qq.com/s/2_tQO7Z6GfmC6y73jc6ITQ

- Qt开发技术:QCharts(四)QChart面积图介绍、Demo以及代码详解

若该文为原创文章,未经允许不得转载原博主博客地址:https://blog.csdn.net/qq21497936原博主博客导航:https://blog.csdn.net/qq21497936/ar ...

- django学习第九天---raw查询原生sql和python脚本中调用django环境和ORM锁和事务

ORM执行原生sql语句 在模型查询api不够用的情况下,我们还可以使用原始的sql语句进行查询 方式1 raw() raw()方法,返回模型的实例django.db.models.query.Raw ...

- 【Java复健指南13】OOP高级04【告一段落】-四大内部类

四大内部类 一个类的内部又完整的嵌套了另一个类结构. class Outer{ //外部类 class lnner{ //内部类 } } class Other{//外部其他类 } 被嵌套的类称为内部 ...

- 【Azure 应用服务】App Service的运行状况检查功能失效,一直提示"实例运行不正常"

问题描述 为App Service配置了健康检查,单独访问Health Check Path的路径,返回代码为200.但为什么在App Service的页面上,一直提示"实例运行不正常&qu ...

- TR069-STUN

原理 1.NAT穿越技术,为了解决NAT设备对P2P网络的通信限制 2.作用:检测网络中是否存在NAT设备,并获取两个通信端点经NAT设备分配的IP地址和端口号,然后建立一条可穿越NAT的P2P链 ...