HDB3 译码器

一、HDB3译码方案一:

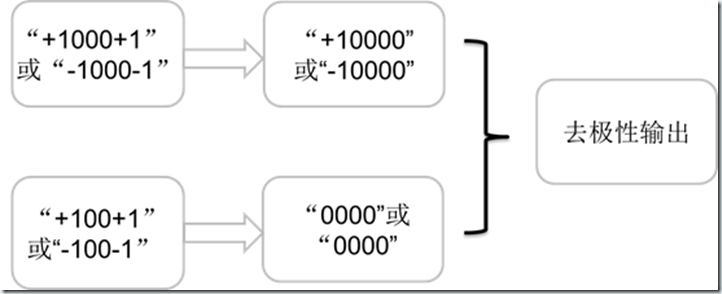

插入V/B的情况是有两种,两个或三个零两端同极性,也就是要把代码二进制表示的“+1 0 0 0 +1”或“-1 0 0 0 -1”变成“1 0 0 0”,把“+1 0 0 +1”或“-1 0 0 -1”变成“0 0 0 0”,最后再把两位二进制表示的+1和-1都变成‘1’,两位二进制表示的0都变成一位二进制表示的‘0’就可以了。

方案一代码:

--hdb3译码

--译码对应的是两位二进制表示的hdb3编码,10表示-;01表示+;00表示0

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY hdb3_decoder IS

PORT( clk : IN STD_LOGIC;

h : INOUT STD_LOGIC_VECTOR( downto ) ;

coderout : out STD_LOGIC

);

END ENTITY hdb3_decoder ; ARCHITECTURE decoder OF hdb3_decoder IS

SIGNAL reg0 : STD_LOGIC_VECTOR( downto ); --两个五位寄存器

SIGNAL reg1 : STD_LOGIC_VECTOR( downto );

BEGIN process (clk,h,reg0,reg1)

BEGIN

if(clk'EVENT AND clk = '') then

reg0 <= h() & reg0( downto ); reg1 <= h() & reg1( downto );

if (h()='' and h()='' and reg0( downto )=""and reg1( downto )="") -- ++ 译码10000

then reg0 <= ""; reg1 <= "";

elsif (h()='' and h()='' and reg0( downto )=""and reg1( downto )="") -- -- 译码10000

then reg0 <= ""; reg1 <= "";

elsif (h()='' and h()='' and reg0( downto )=""and reg1( downto )="") -- -- 译码0000

then reg0 <= "" & reg0(); reg1 <= "" & reg1();

elsif ( h()='' and h()='' and reg0( downto )="" and reg1( downto )="") -- ++ 译码0000

then reg0 <= "" & reg0(); reg1 <= "" & reg1();

end if;

end if;

end process; process(clk)

begin

if (clk'EVENT AND clk = '') then

if reg0()='' or reg1()='' then --把+()、(-)译码成一位

coderout<='';

--elsif reg0()='' and reg1()=''

-- then coderout<='';

else

coderout<=''; -- 译码为

end if;

end if;

end process;

二、HDB3译码方案二:

对输入的H+和H-分别设立一个五级缓存移位寄存器,每一拍都判断是否存在10001,或1001X;若存在分别改成00001,或0000X。再将H+和H-相或输出。

方案二代码:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY hdb3_decoder IS

PORT( clk : inout STD_LOGIC;

--h : in STD_LOGIC_VECTOR( downto );

hp : in STD_LOGIC;

hn : in STD_LOGIC;

clkout :out STD_LOGIC;

outcoder : out STD_LOGIC );

END ENTITY hdb3_decoder ; ARCHITECTURE decoder OF hdb3_decoder IS

SIGNAL reg0 : STD_LOGIC_VECTOR( downto ); --两个五位寄存器

SIGNAL reg1 : STD_LOGIC_VECTOR( downto );

SIGNAL hh : STD_LOGIC_VECTOR( downto ); --两个五位寄存器

SIGNAL hl : STD_LOGIC_VECTOR( downto );

BEGIN

clkout <= clk;

PROCESS (clk,reg0,reg1)

BEGIN

if(clk'EVENT AND clk = '') then --上升沿

reg0 <= hn & reg0( downto ); reg1 <= hp & reg1( downto );

if(reg0 = "") then

reg0 <= "";

elsif (reg0 = "" or reg0 = "") then

reg0 <= "" & hn;

end if; if(reg1 = "") then

reg1 <= "";

elsif (reg1 = "" or reg1 = "") then

reg1 <= "" & hp;

end if;

end if;

hl <= reg0;

hh <= reg1;

end PROCESS;

outcoder <= (hh() or hl());

end decoder;

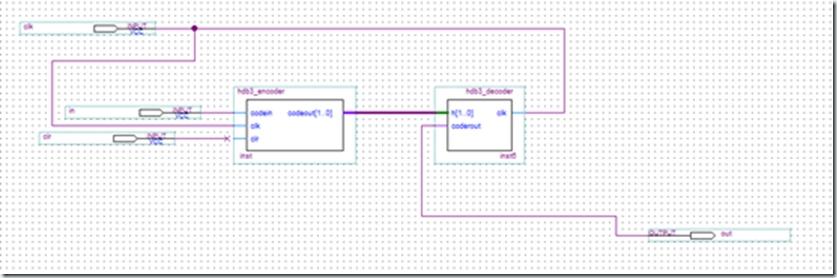

说明:译码因为仿真时需要每个符号需要赋值两位比较麻烦,我在确认HDB3编码没问题的基础之下,把编码和译码在Quartus II 中封装起来,用原理图连接起来,若输入和输出是一样的,则译码没有问题。我已调试过,上面两个程序都可以,在最终时分多路数字电话基带传输系统的设计中译码选用的是方案一。

电路原理连接如下:

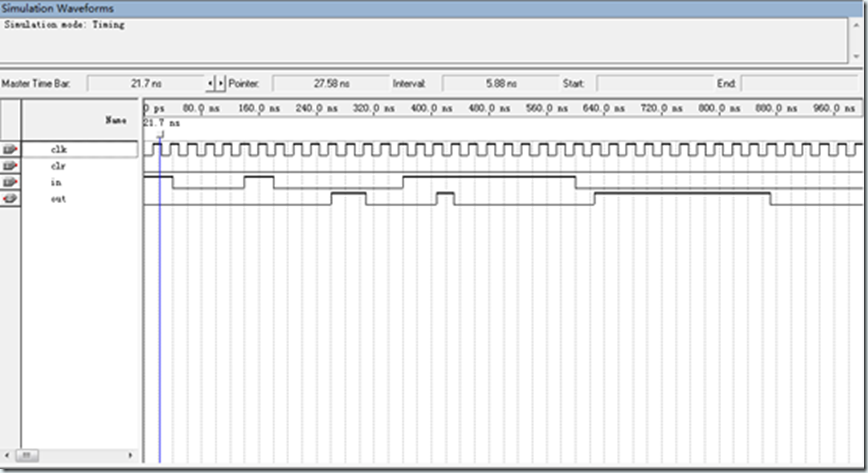

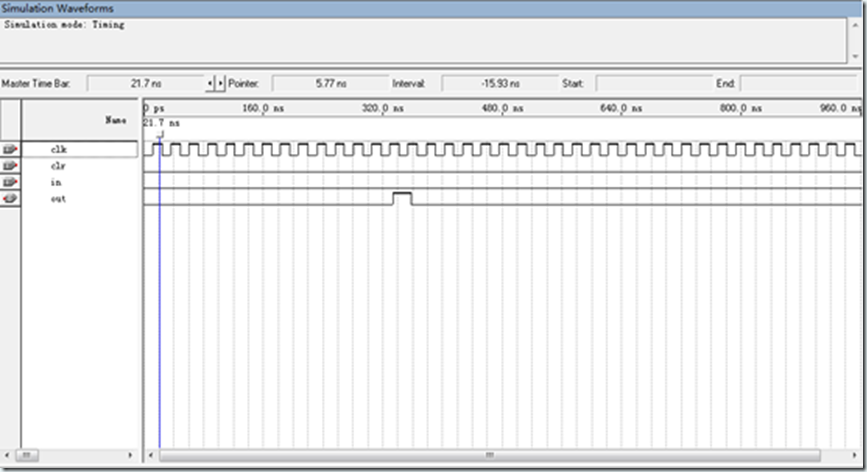

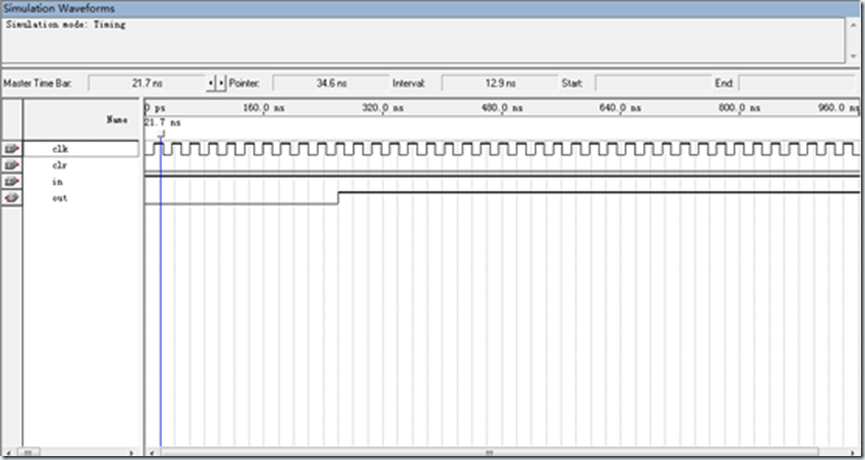

仿真图:

1、输入随机数码

2、 输入全0码

3、输入全1码

感悟:

以前写的大多是顺序语句,这次利用VHDL语言完成课程设计的过程中,进一步熟悉和利用VHDL里的并行语句,例如进程等进件层次的使用。VHDL是一种硬件描述语言,用来描述硬件系统。硬件系统中的电路是由很多元器件构成的,从上电那一时刻起,硬件系统中所有的电路模块(元器件)将会同时开始工作,没有先后顺序,可以用VHDL中的并行语句实现。因此,结构体中的所有语句都须是“并行语句”,每个并行语句描述一个电路模块。并行语句之间没有先后顺序,可按任意顺序书写。这就像画电路图,先画哪个电路模块是没有关系的,只要最终画完的硬件系统电路图是正确的就行。然而,人们描述一个系统的“行为”却是按照“因果”关系来描述的,例如,“因为...所以...”(IF...THEN...)。这种描述方式称之为”行为描述“,描述行为的语句是顺序语句。顺序语句不符合硬件的并行工作状态,因此不能直接置于结构体中。为了遵循结构体中的语句都是并行语句这一语法规则,将一系列顺序语句构成的行为描述看成是一个电路模块,将其包装成一个并行语句“PROCESS BEGIN....END PROCESS;”,相当于在c语言中给这段行为描述加了一对括号,左括号是PROCESS BEGIN,右括号是END PROCESS。任意两个PROCESS语句之间也是并行关系,书写的先后顺序可以任意,与其他并行语句的书写顺序也可以任意。如果用顺序语句来描述硬件,就要给顺序语句加上“外包装“——”PROCESS BEGIN....END PROCESS;”。

HDB3 译码器的更多相关文章

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- 03-组合逻辑电路设计之译码器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为例学会简单组合逻辑电路设计 实验平台:无 实验原理: 组合逻辑, ...

- 2.计算机组成-数字逻辑电路 门电路与半加器 异或运算半加器 全加器组成 全加器结构 反馈电路 振荡器 存储 D T 触发器 循环移位 计数器 寄存器 传输门电路 译码器 晶体管 sram rom 微处理 计算机

现代计算机的各个部件到底是如何通过逻辑电路构成的呢 半加器 我们说过了门电路 看似简单的三种门电路却是组成了整个逻辑电路的根基 真值表--其实就是根据输入输出状态枚举罗列出来的所有可能 比如有一台 ...

- HDB3编码器

一.HDB3 码介绍 三阶高密度双极性码(英语:High Density Bipolar of Order 3 code,简称:HDB3码)是一种适用于基带传输的编码方式.它是一种 AMI 码的改进型 ...

- 利用Xilinx HLS实现LDPC译码器

1. 概述 采用Xilinx HLS快速实现的部分并行,全流水的LDPC译码器. 环境:Vivado HLS 2018.2 码字:IEEE 802.16e 2/3A 算法:Min-Sum Algori ...

- LDPC译码器的FPGA实现

应用笔记 V0.0 2015/3/17 LDPC译码器的FPGA实现 概述 本文将介绍LDPC译码器的FPGA实现,译码器设计对应CCSDS131x1o1s文档中提到的适用于深空通信任务的LD ...

- STC15控制数码管 38译码器

共阳极数码管举例 #define MAIN_Fosc 27000000L //定义主时钟 #include "STC15Fxxxx.H" #define uchar unsigne ...

- 8-3编码器,3-8译码器的verilog实现

在数字系统中,由于采用二进制运算处理数据,因此通常将信息变成若干位二进制代码.在逻辑电路中,信号都是以高,低电平的形式输出.编码器:实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码 ...

- c++实验8 哈夫曼编码-译码器

哈夫曼编码-译码器 此次实验的注释解析多加不少---若对小伙伴们有帮助 希望各位麻烦点个关注 多谢 1.哈夫曼树构造算法为: (1)由给定的n个权值{w1,w2,…,wn}构造n棵只有根结点的二叉树, ...

随机推荐

- Apache rewrite地址重写

Apache-rewrite+13个经典案例Apache 重写规则的常见应用(rewrite)一:目的 如何用Apache重写规则来解决一些常见的URL重写方法的问题,通过常见的 实例给用户一些使用重 ...

- luogu3263/bzoj4002 有意义的字符串 (数学+矩阵快速幂)

首先我们发现$\frac{b+\sqrt{d}}{2}$这个形式好像一元二次方程的求根公式啊(???反正我发现不了) 然后我们又想到虽然这个东西不好求但是$(\frac{b-\sqrt{d}}{2}) ...

- centos7搭建ELK Cluster集群日志分析平台(四):Fliebeat-简单测试

续之前安装好的ELK集群 各主机:es-1 ~ es-3 :192.168.1.21/22/23 logstash: 192.168.1.24 kibana: 192.168.1.25 测试机:cli ...

- Codeforces 1051E. Vasya and Big Integers

题意:给你N个点M条边,M-N<=20,有1e5个询问,询问两点的最短距离.保证没有自环和重边. 题解:连题目都在提示你这个20很有用,所以如果是颗树的话那任意两点的最短距离就是求一下lca搞一 ...

- python安装tesseract

一.最近在学习python爬虫的时候需要用到tesseract,但书上的给的教程对我并不适用,坑了好久天,才终于成功. 二.方法: 1.由于我看的是静谧博主的那本书.他给的教程在python3安装有问 ...

- height、clientHeight、offsetHeight、scrollHeight、height()、 innerHeight()、outerHeight()等的区别

1.height height是css属性,这个属性定义元素内容区的高度,在内容区外面可以增加内边距.边框和外边距. 当 box-sizing: content-box 时,高度应用到元素的内容框. ...

- C++ 容器操作

typedef struct point { int x; int y; }Point; 在声明变量的时候就可以:Point p1; 如果没有typedef, 如: struct point { in ...

- 软件在 win7 上运行时显示乱码

一个用户反应后,我当时就蒙圈了,因为之前从未遇到过: 百度一下后,发现用户的这种情况比较特殊,从表面上看,[控制面板]和[注册表]相关项设置都正常,为什么还显示乱码呢? 到最后一步如果已经是(简体,中 ...

- 在Java中调用与系统有关的剪切板Clipboard

java从1.5版开始已经能与系统的剪切板很好的交互了. 如果可以在程序中直接调用系统的剪切板来保存“复制”的对象内容,那可以说的比之前的想法好很多. 下面是一个对java.io.File对象进行co ...

- macs 学习

点击 首先andriomianfest主配文件(主要配置文件),来启动主要的activity对象,然后通过该对象调用create方法来加载布局文件xml active通过布局文件的控件生成相应的对象. ...