Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core。通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core的源码,这也是Xilinx为了保护作者知识产权,对IP Core进行加密。对我们开发者而言,我们也可以自定义封装自己的IP Core,需要用的这部分功能的时候,只需要直接添加IP Core进来就行了,来一起搭起你的数字积木吧!

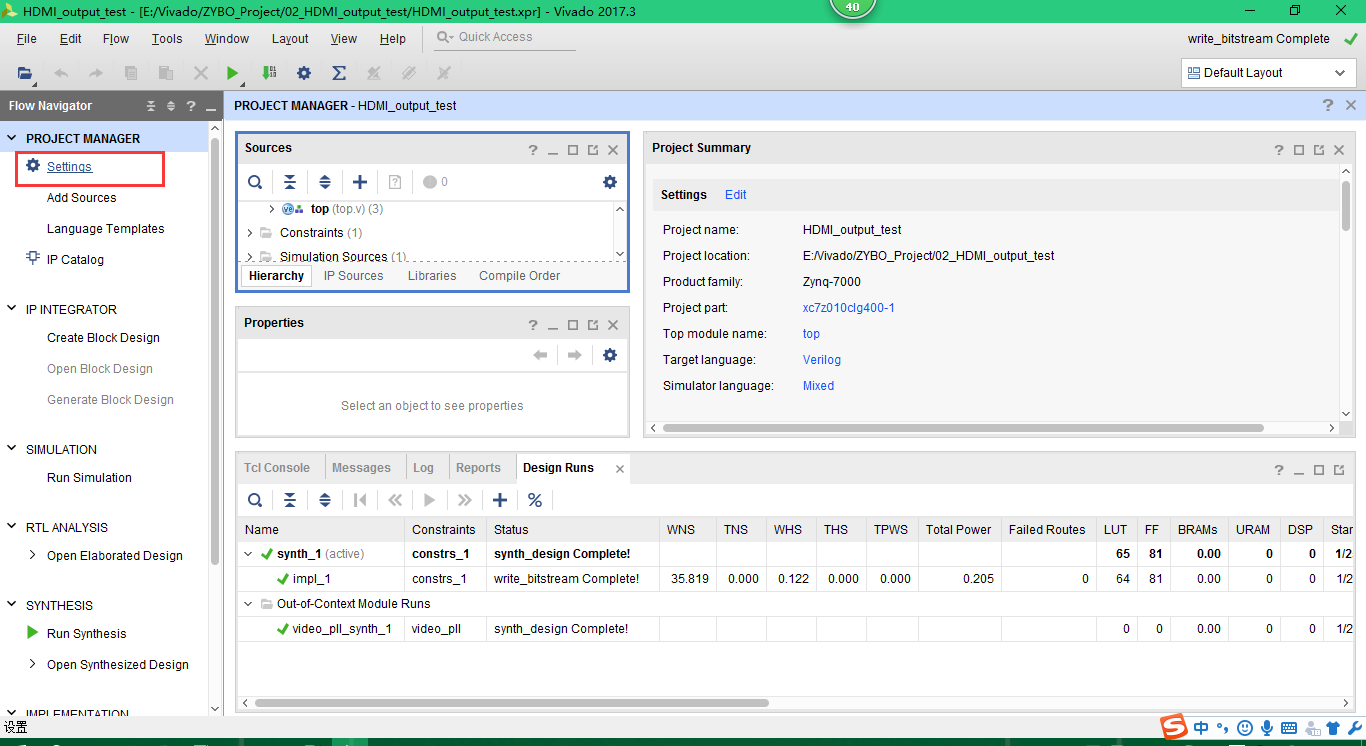

将你要封装的代码建立成一个工程,然后点击如图所示setting。

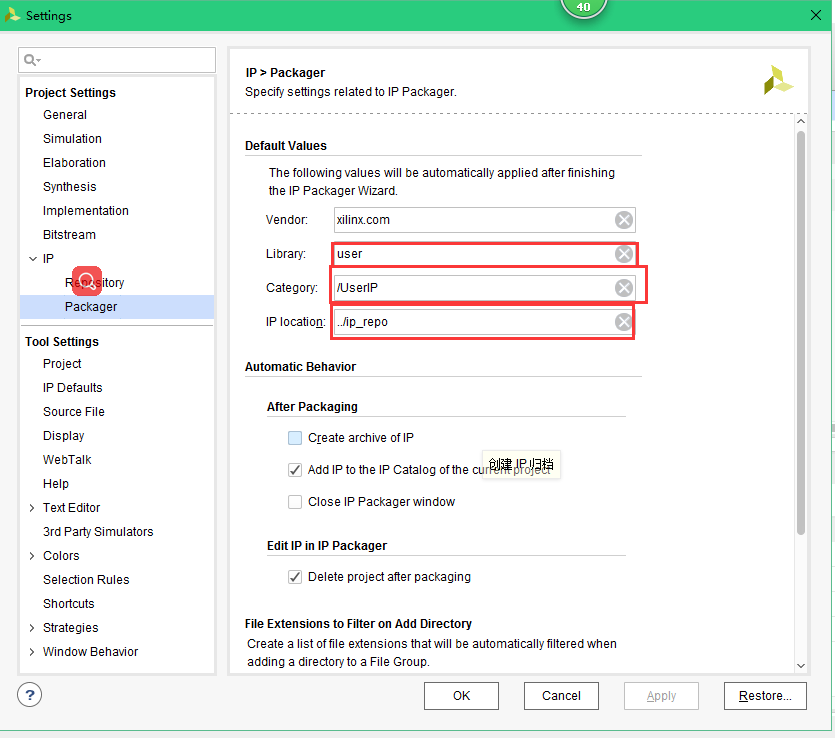

点击IP——Package,图中所标注的都是可以编辑的,这里可以自定义库名等,默认也可。

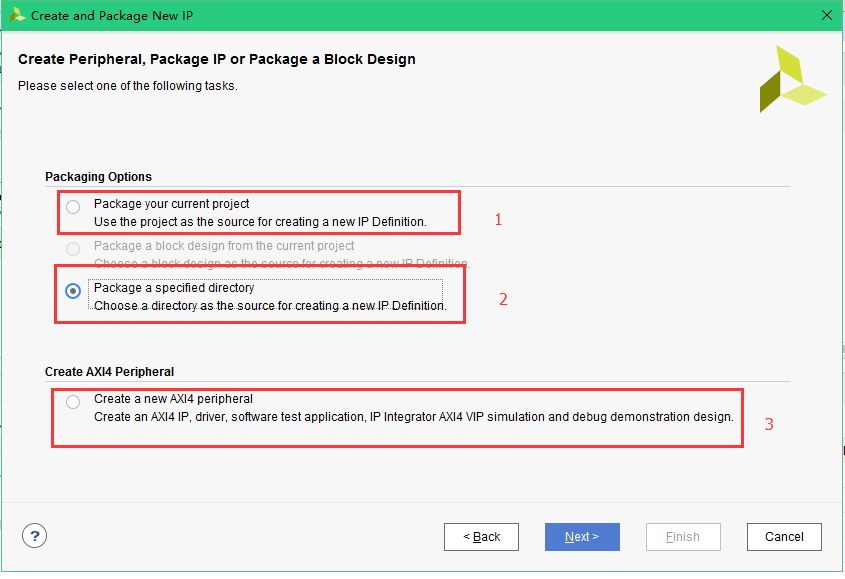

设置完成后,回到主界面,在主菜单上方点击tools——Create and Package New IP

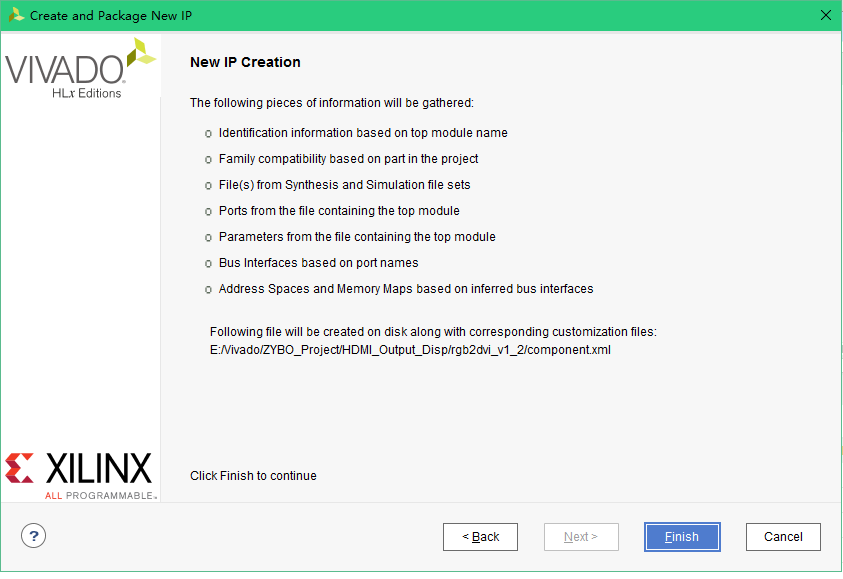

根据提示一步步走下去。

第一个是将当前工程创建成IP

第二个是将指定目录下的工程创建成IP

第三个是封装成SOC部分的IP

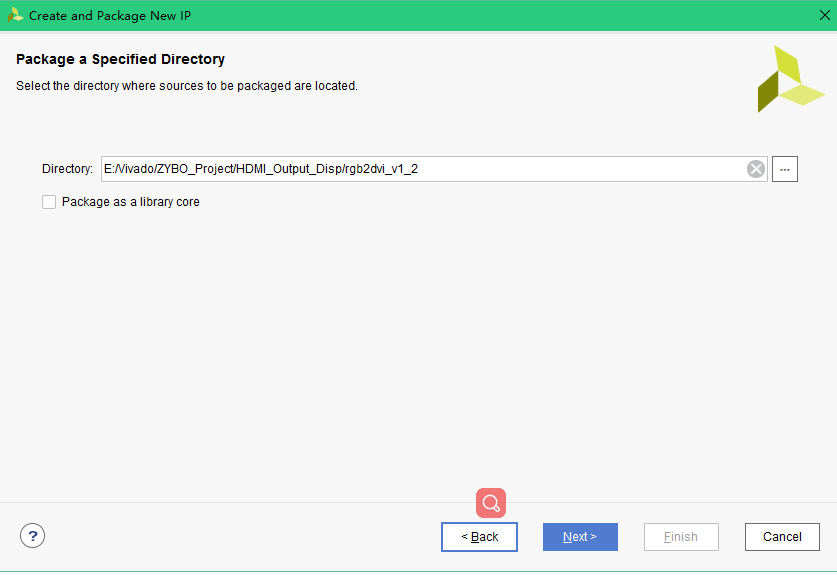

这里因为我选择的是第二个,因为的我是封装其他工程中的代码,一般情况下选择第一个。按照流程走就可以了。

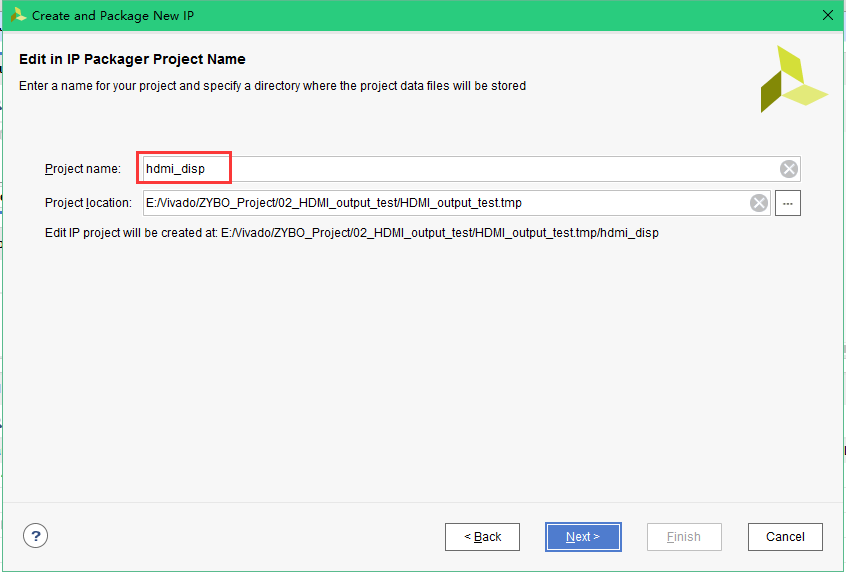

设置路径,工程名,

最后点击finish,创建工程。

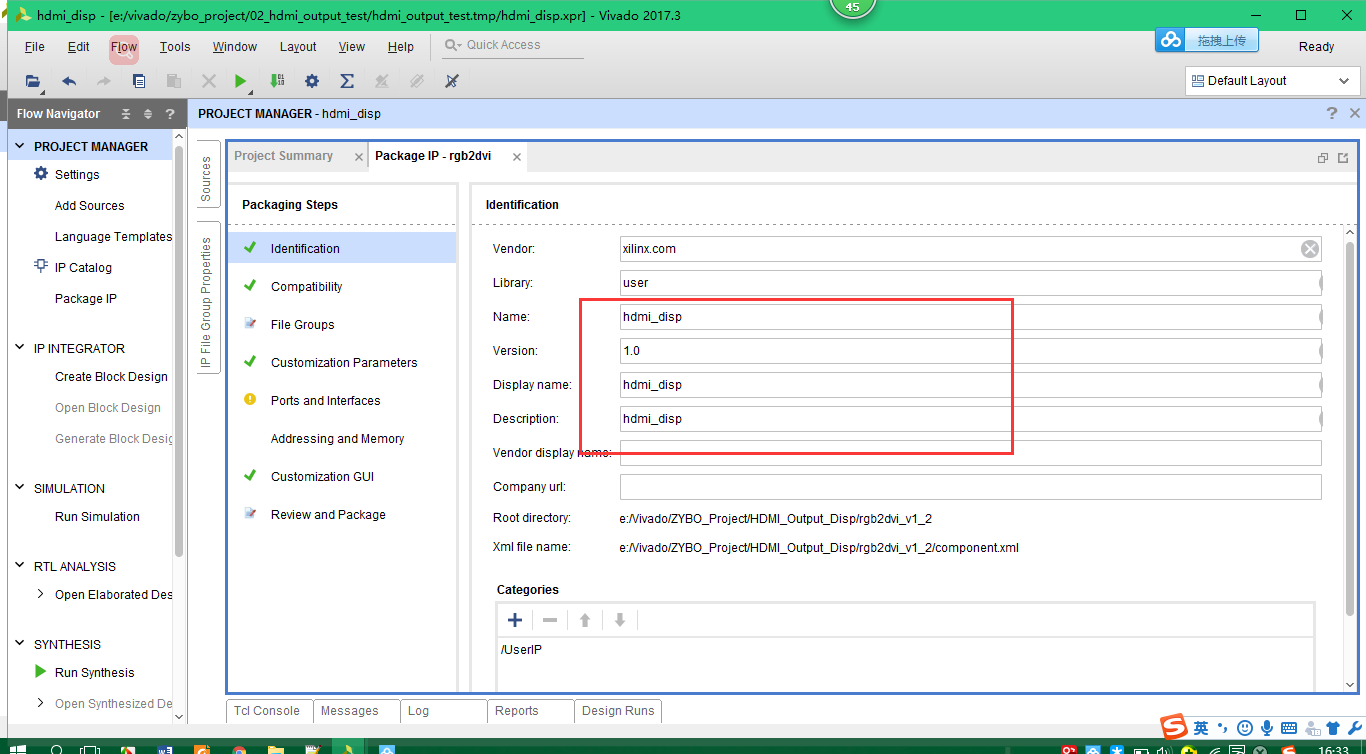

在工程主界面,点击Identification中可以设计IP Core名称和版本描述。

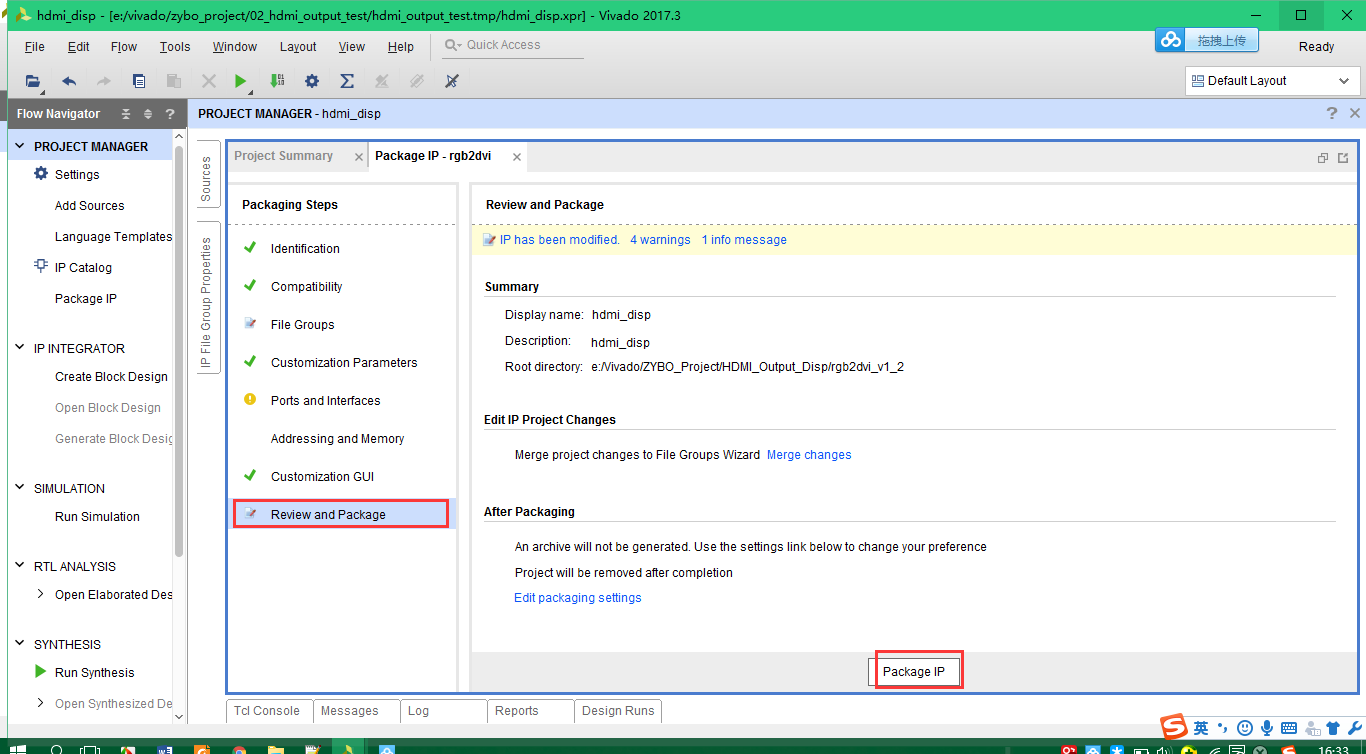

这里直接跳到最后一步,点击Package IP,然后就封装成功了。

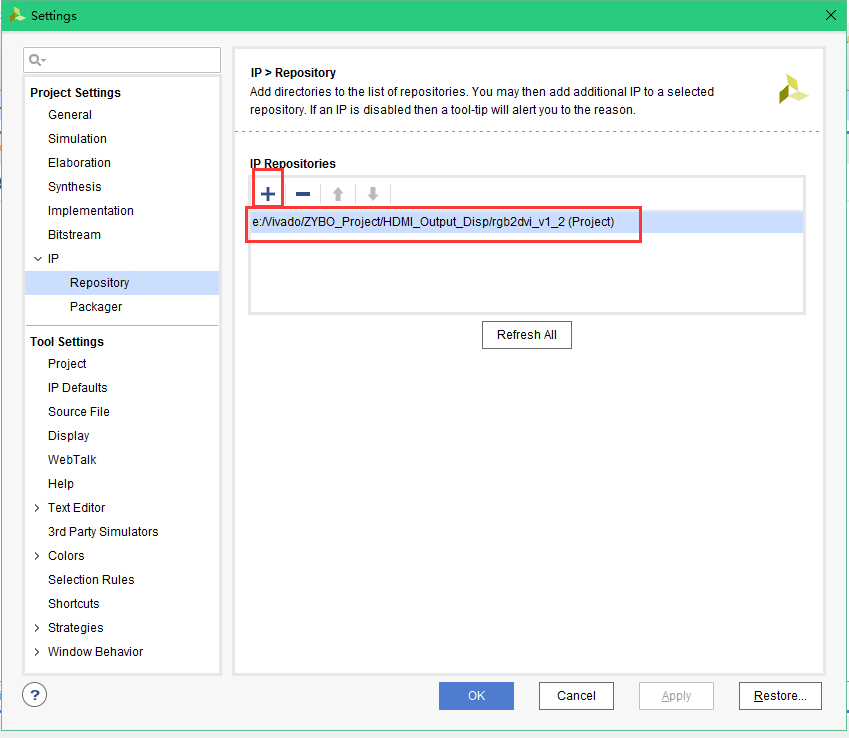

需要你封装的IP时,主界面setting——IP——Repository中添加你封装好的文件夹路径。

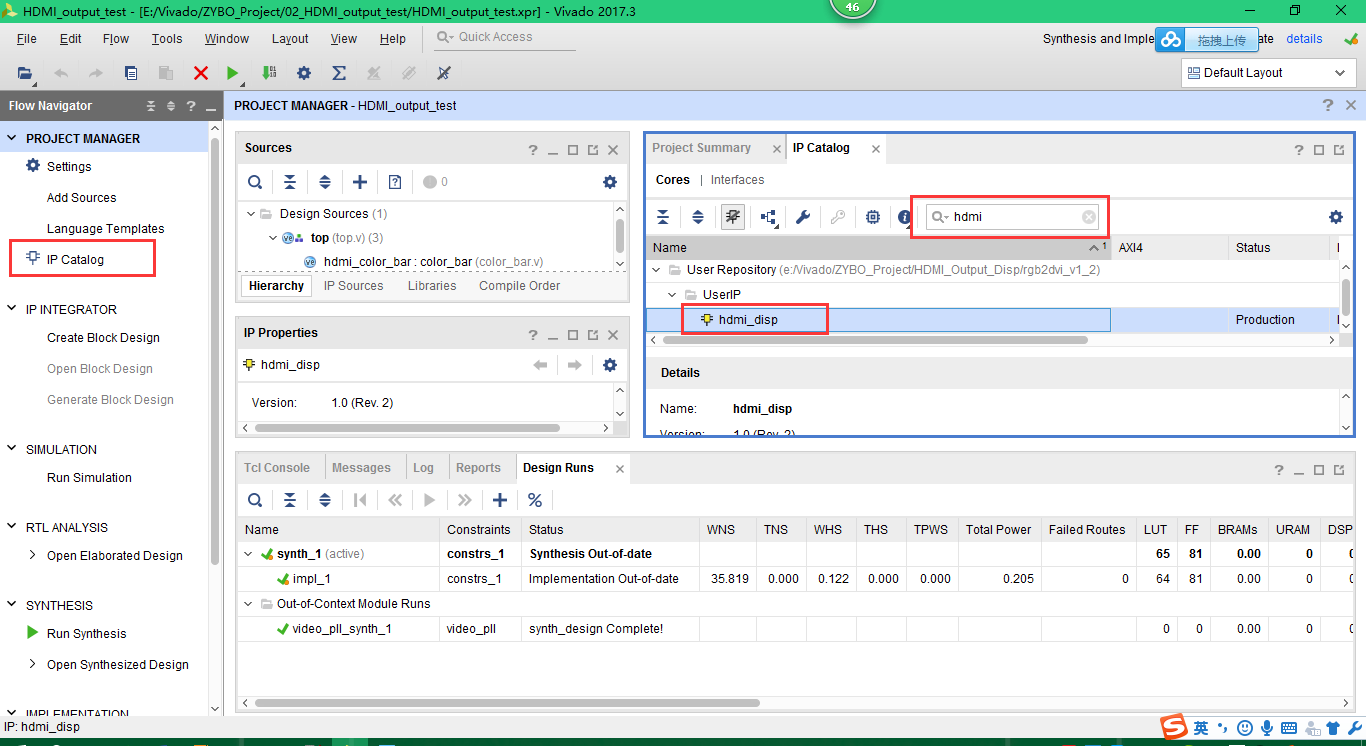

添加完成后,点击IP Catalog,搜索你的IP Core,双击就可以直接调用了。

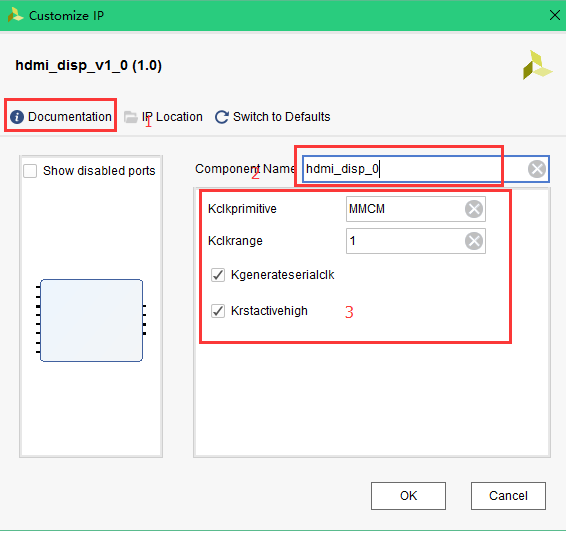

接下来的流程就和调用其他IP时候使用的相似的。我这里封装的是一个HDMI的代码,因为代码比较多,而且使用VHDL语言写的,但是在Verilog HDL的工程中也可以调用,所以为了便捷,把它封装成一个IP Core。

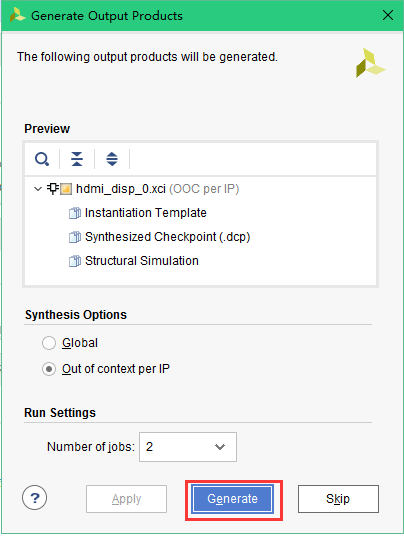

点击Generate就生成,可以直接使用了。

最后欢迎关注一亿人都想要关注的微信订阅号【开源FPGA】,总结、记录自己的学习过程,一个FPGA工程师的养成之路。欢迎加入开源FPGA-交流群-I进行讨论,群号码:677163633。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8370843.html

Vivado 2017封装自定义IP Core的更多相关文章

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- 强大的Vivado IP工具——自定义IP的使用

首先,要指出,本文不描述任何IP的功能与使用. 在开发一个大型FPGA项目时,多人协作是必不可少的.这个时候,如何提交设计给负责集成的人,是项目开发中最关键的问题之一. 常用的一个方法是,提交网表 ...

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断.PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势. 一.PL 侧定时 ...

- Xilinx Vivado的使用详细介绍(5):调用用户自定义封装的IP核

Zedboard OLED Display Controller IP v1 介绍 Author:zhangxianhe 本文档提供了快速添加,连接和使用ZedboardOLED v1.0 IP内核的 ...

- 第三章 VIVADO 自定义IP 流水灯实验

第二章里面已经说过了,MIZ701 PL部分没有输入时钟,因此驱动PL资源必须是通过PS来提供时钟,所以这个流水灯实验也得建立一个最小系统了,然后再添加一个流水灯的自定义IP. 3.0本章难度系数★★ ...

随机推荐

- mysql中去重 distinct 用法

在使用MySQL时,有时需要查询出某个字段不重复的记录,这时可以使用mysql提供的distinct这个关键字来过滤重复的记录,但是实际中我们往往用distinct来返回不重复字段的条数(count( ...

- erlang单独配置文件

一种是erl启动的时候加参数 doudizhu.config [ {doudizhu,[ {listen_port, }, {node_caller_prefix,"ruby"}, ...

- java 方法(函数)

所谓方法,就是用来解决一类问题的代码的有序组合,是一个功能模块. 一般情况下,定义一个方法的语法是: 其中: 1. 访问修饰符:方法允许被访问的权限范围, 可以是 public.protected.p ...

- 关于filter web api mvc 权限验证 这里说的够详细了。。。

参考:http://www.cnblogs.com/willick/p/3331520.html Filter(筛选器)是基于AOP(面向方面编程)的设计,它的作用是对MVC框架处理客户端请求注入额外 ...

- Bootstrap-CL:Well

ylbtech-Bootstrap-CL:Well 1.返回顶部 1. Bootstrap Well Well 是一种会引起内容凹陷显示或插图效果的容器 <div>.为了创建 Well,只 ...

- 华为5573+联通4G上网SIM+ROS hap ac-RB962UiGS-5HacT2HnT 上网

华为5573+联通4G上网SIM+ROS hap ac-RB962UiGS-5HacT2HnT 上网 原理其实是这样的,ROS的USB口连接华为5573: 华为5573看成是一个路由器,他的外网网卡走 ...

- python 多态、多继承、函数重写、迭代器

用于类的函数 issubclass(cls,class_or_tuple) 判断一个类是否继承自其他的类,如果此类cls是class或tuole中的一个派生(子类)则返回True,否则返回False ...

- Clearsigned file isn't valid, got 'NOSPLIT' (does the network require authentication?)

ubuntu16在运行sudo apt-get update 命令后,报出错误: Clearsigned file isn't valid, got 'NOSPLIT' (does the netwo ...

- 关于微信小程序的一些看法和理解

最近做了几个小时的调研,微信小程序 微信小程序是可以理解成在微信中的APP,他的目标是APP的替代者,由于目前的APP主要区分安卓和IOS,或者其他平台, 那么微信小程序的平台在微信,在任何一个手机系 ...

- Java——poi读取Excel文件

1.创建文件流,打开EXCEL文件 FileInputStream excelFile = new FileInputStream(excelPath); XSSFWorkbook workbook ...