设计简单算法体验Vivado HLS的使用

前言

本文主要讲解了使用Vivado HLS设计简单C语言的二选一选择器算法的硬件HLS开发的全流程,包括工程创建-算法验证和仿真-算法综合-RTL仿真-IP封装等步骤。

参考网站:

http://blog.chinaaet.com/cuter521/p/36069

http://blog.chinaaet.com/cuter521/p/36119

公司想要将立体匹配的算法进行硬件实现,无奈本人硬件小白一枚,看了基于verilog硬件实现的相关文档之后还是找不到感觉,其实FPGA进行硬件实现功能也挺强大的,手边有zedboard开发板,正好看到可以使用Vivado可以将c/c++转换为FPGA实现,最让人惊喜的是还有HLS图像库,和opencv比较相似,果断选择了Vivado,只是还需要从头开始!加油!

内容:

1. 熟悉Vivado HLS的使用以及开发流程;

2.使用Vivado HLS进行C/C++算法的仿真验证;

3.对C语言的算法进行综合,查看RTL方则很难结果,并将设计进行IP封装;

操作步骤:

1.新建工程

2.添加设计资源文件

3.C代码仿真验证

4.算法综合-自动生成verilog等其他文件

5.RTL仿真以及查看波形

6.IP封装

操作过程:

1.新建工程

双击Vivado HLS打开HLS;

单击“Create New Project”,打开新建工程向导,第一个界面如下图所示。

谨慎起见,将工程名和设计的模块名保持一致,设置完毕后,点击Next,进入下面的界面。

建立空工程,先不添加,进入工程之后再自行添加设计文件,点击Next,进入如下图所示的测试文件添加界面。

直接跳过点击Next,进入下一界面,如下图所示。

这一步需要进行设置,否则Finish按钮一直是灰化的,不能生成工程。红色方框内的提示可以看出,这里是选择所用芯片的型号的。点击绿色椭圆内的按钮,进入芯片选择对话框,如下图所示。

这里不用多说,两种方式,一种好似逐一选择Family, Package, Speed Grade等参数,直到定位到你想要的芯片,如下图所示。

另一种方法是直接选择开发板,如下图所示。

选择完成后点击OK,返回发现part部分已经选中Zedboard开发板,Finish按钮可用。点击Finish按钮完成向导,进入HLS主界面,如下图所示。

2.添加设计资源文件

2.1添加设计文件

选中左侧Explorer子窗体下的Source目录,邮件,弹出Add/New Files菜单,点击添加资源文件,如下图所示(注:有些图因为当时没有保存,直接借用原作者的图)。

Top Function:mux21

mux21源码如下:

#include "mux21.h" int1 mux21(int1 sig_a, int1 sig_b, int1 select)

{

if(==select)

return sig_a;

else

return sig_b;

}

mux21.h的内容是:

#include <ap_cint.h>

ap_cint.h这个头文件的包含,是为了使用int1类型,int1表示1位整型数。

注意:.h文件是不用添加的,HLS会自动包含相应的头文件,但是路径要正确。

2.2添加测试文件和数据

单击Test Bench目录,添加测试文件和数据,添加文件夹时,需要选择“Add Folder…”选项。如果把测试文件添加到Source目录中,编译会产生问题。

testbench mux21_tb.c源码为:

#include <stdio.h>

#include "mux21.h" int main(void)

{

int1 res1 = ;

int1 res2 = ; res1=mux21(,,);

res2=mux21(,,); if(res1 && res2)

printf("test passed, well done!\n"); return ;

}

2.3设置工程属性

选中mux21文件夹,右击,弹出如下图所示的菜单。

点击Project Setting,进入设置界面,如下图所示。

点击Synthesis,进入下图所示的界面。

3.C代码仿真验证

在菜单栏中找到Project > Run C Simulation命令,或者直接单击工具栏中的按钮(如下图所示),编译和执行C程序。

编译过程以及执行结果会在主界面下方的Console自选项卡中打印显示,如下图所示。

注意:编写代码时,没有正确包含 .h文件,不能进行C代码的仿真和验证。发现错误,修改了之后,IDE可能不会自动检测,这里可以尝试使用Index功能,IDE会检测改动,消除错误提示。

使用了int1类型,但是没有包含ap_cint.h文件,显示效果如下图所示。

这时,就算修改代码,包含了ap_cint.h文件,错误提示依旧存在。需要手动Index C source,提示才会消除。操作如下图所示:Project > Index C Source,或者点击工具栏中的快捷按钮,下图所示红色方框内的图标。

4.算法综合-自动生成verilog等其他文件

如下图所示,在菜单中寻找命令:Solution > Run C Synthesis > Active Solution,点击Active Solution菜单,HLS会自动完成综合工作。

此外,还可以直接点击工具栏中的快捷按钮(下图红色方框内),在下拉菜单中选择“Active Solution”命令,也能够启动综合进程。

接下来就可以进入工程文件夹,找到综合文件夹,查看所综合出的HDL代码,文件结构如下图所示。

rpt文件显示“General Information(基本信息)”、“Performance Estimates(性能估算)”、“Utilization Estimates(资源利用估算)”、“(Interface接口)”等信息。

verilog文件夹下是综合出来的.v文件,vhdl文件夹下综合出来的是.vhd文件,打开mux21.v,代码为:

`timescale ns / ps

(* CORE_GENERATION_INFO="mux21,hls_ip_2014_2,{HLS_INPUT_TYPE=c,HLS_INPUT_FLOAT=0,HLS_INPUT_FIXED=1,HLS_INPUT_PART=xc7z020clg484-1,HLS_INPUT_CLOCK=10.000000,HLS_INPUT_ARCH=others,HLS_SYN_CLOCK=1.370000,HLS_SYN_LAT=0,HLS_SYN_TPT=none,HLS_SYN_MEM=0,HLS_SYN_DSP=0,HLS_SYN_FF=0,HLS_SYN_LUT=0}" *)

module mux21 (

ap_start,

ap_done,

ap_idle,

ap_ready,

sig_a,

sig_b,

select_r,

ap_return

);

parameter ap_const_logic_1 = 'b1;

parameter ap_const_logic_0 = 'b0;

input ap_start;

output ap_done;

output ap_idle;

output ap_ready;

input [:] sig_a;

input [:] sig_b;

input [:] select_r;

output [:] ap_return;

assign ap_done = ap_start;

assign ap_idle = ap_const_logic_1;

assign ap_ready = ap_start;

assign ap_return = ((select_r)? sig_b: sig_a);

endmodule //mux21

主要功能语句:

assign ap_return = ((select_r) ? sig_b : sig_a);

由于这个设计过于简单,ap_start、ap_ready、ap_done、ap_idle以及ap_return信号的作用不太能体现出来,从命名来看,主要是用于控制模块工作的信号。

5.RTL仿真以及查看波形

Solution > Run C/RTL Cosimulation,仿真完成后,需要在Vivado下查看仿真结果。

注意:Dump Trace选项要选择all,否则不会产生波形数据,位置如下图所示。

cd E:/hls/mux21/solution1/sim/verilog/

current_fileset

open_wave_database mux21.wdb

open_wave_config mux21.wcfg

注释:

更改路径

加载工程

加载仿真数据

打开波形窗口

生成的波形如下图所示:

6.IP封装

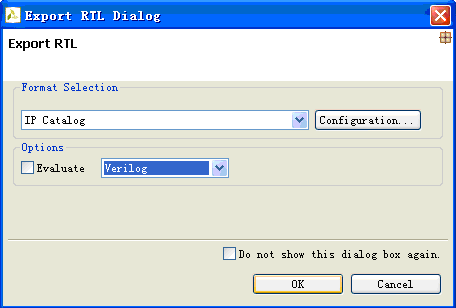

Solution > Export RTL,或者点击工具栏快捷按钮 ,打开Export RTL对话框,如下图所示。

,打开Export RTL对话框,如下图所示。

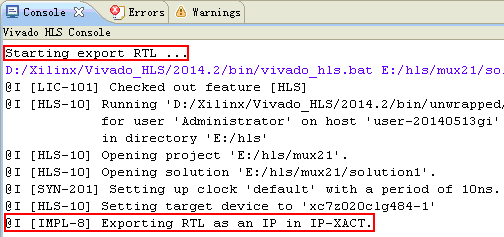

命令行会打印提示整个IP封装过程,如下图所示。

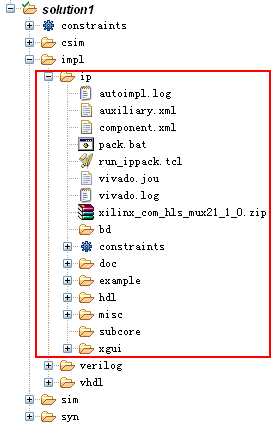

IP封装完成后,mux21文件夹下会出现impl文件夹,该文件夹下包含ip、verilog、vdhl三个子文件夹,在这些文件夹中,我们可以找到封装过程中生成的文件。

7.结论

本渣只是根据cuter的博客练习使用Vivado,其实还没有使用到HLS,所以本博客的大部分内容是重复的,只是本渣自己实现了整个过程,当然在这个过程中也遇到了一些其他的问题,所以总结一下,留作以后的参考。

做的过程中很多图没有截下来,直接拿过来使用了,望勿喷!可交流!

当然,这离HLS的实现还有好远!

完

设计简单算法体验Vivado HLS的使用的更多相关文章

- 基于Vivado HLS在zedboard中的Sobel滤波算法实现

基于Vivado HLS在zedboard中的Sobel滤波算法实现 平台:zedboard + Webcam 工具:g++4.6 + VIVADO HLS + XILINX EDK + ...

- Vivado HLS与System Generator:联系与区别

在很多年以前的ISE套件里面,有个功能强大的AccelDSP,它可以可自动地进行浮点到定点转换,并把算法生成可综合的HDL,还可以创建用于验证的测试平台,但是在4年前左右的时候销声匿迹了,当时的说法是 ...

- ZED-Board从入门到精通系列(八)——Vivado HLS实现FIR滤波器

http://www.tuicool.com/articles/eQ7nEn 最终到了HLS部分.HLS是High Level Synthesis的缩写,是一种能够将高级程序设计语言C,C++.Sys ...

- vivado hls(1)

笔记 1.vivado hls是fpga高级综合工具,可以将C语言转换成verilog代码,适合编写算法,但是要有硬件思想. 2.软核就是只要资源足够,就可以用逻辑打一个CPU出来,与硬核不一样,硬 ...

- Vivado HLS 工具

干什么的 Vivado HLS工具可以将C语言高级综合为硬件. 为什么要使用HLS 可以在更高的抽象层次描述功能,而不是在传统的RTL级别 一个潜在的用处是,系统设计划分成硬件部分和软件部分之后,软件 ...

- 设单链表中存放n个字符,试设计一个算法,使用栈推断该字符串是否中心对称

转载请注明出处:http://blog.csdn.net/u012860063 问题:设单链表中存放n个字符.试设计一个算法,使用栈推断该字符串是否中心对称,如xyzzyx即为中心对称字符串. 代码例 ...

- python学习:设计一个算法将缺失的数字找出来。

算法题 已知整型数值 a[99], 包含的所有99个元素都是从1-100中随机取值,并且这99个数两两互不相等,也就是说从1到100这100个数字有99个在数值内,有一个缺失.请设计一个算法将缺失 ...

- springmvc 项目完整示例01 需求与数据库表设计 简单的springmvc应用实例 web项目

一个简单的用户登录系统 用户有账号密码,登录ip,登录时间 打开登录页面,输入用户名密码 登录日志,可以记录登陆的时间,登陆的ip 成功登陆了的话,就更新用户的最后登入时间和ip,同时记录一条登录记录 ...

- 给定一个数组,它的第 i 个元素是一支给定股票第 i 天的价格。 如果你最多只允许完成一笔交易(即买入和卖出一支股票),设计一个算法来计算你所能获取的最大利润。

给定一个数组,它的第 i 个元素是一支给定股票第 i 天的价格. 如果你最多只允许完成一笔交易(即买入和卖出一支股票),设计一个算法来计算你所能获取的最大利润. 注意你不能在买入股票前卖出股票. 示例 ...

随机推荐

- 小Z的袜子(hose)

小Z的袜子(hose) 作为一个生活散漫的人,小Z每天早上都要耗费很久从一堆五颜六色的袜子中找出一双来穿.终于有一天,小Z再也无法忍受这恼人的找袜子过程,于是他决定听天由命……具体来说,小Z把这N只袜 ...

- cogs448

☆ 输入文件:1.in 输出文件:1.out 简单对比时间限制:1 s 内存限制:128 MB [题目描述] 在某次膜拜大会上,一些神牛被要求集体膜拜.这些神牛被奖励每人吃一些神牛果. ...

- Microsoft SQL Server Trace Flags

Complete list of Microsoft SQL Server trace flags (585 trace flags) REMEMBER: Be extremely careful w ...

- java 中多播、广播编程

在 IP 协议层,有多播.广播的概念.IP 地址分为网络地址和主机地址,主机地址全部为1,就是广播地址.多播使用 D 类地址,从 224.0.0.0 到 239.255.255.255.IP 多播需要 ...

- Linux查看用户属于哪些组/查看用户组下有哪些用户

一.关于/etc/group格式的讨论 在说/etc/group格式的时候,网上很多文章都会说是“组名:组密码:组ID:组下用户列表”,这说法对了解/etc/group格式是没问题的,但如果碰到“查看 ...

- js代码之编程习惯

编程习惯: 异常处理 如果你没有使用异常处理的习惯,这可能是因为你并未真正的理解它的作用.当你正确使用异常处理之后,你会发现你的代码最显著的变化就是:少了很多的 if-else 语句 . 虽然在 JS ...

- shell 通配符

Bash中的通配符 '?' 匹配一个任意字符 '*' 匹配0个或任意多个字符,也就是可以匹配任何内容 '[]' 匹配括号中任意一个字符.例如[abc]代表一定匹配一个字符,或者是a,或者是b,或者是c ...

- 【MVC】快速构建一个图片浏览网站

当抄完MusicStore时,你应该对MVC有一个比较清晰的认识了.接下来就需要做个网站来继续增加自己的知识了.那么,该做个什么网站呢.做个图片浏览网站吧,简单而实用. 简单设计 1.首先,页面中间是 ...

- java⑿

1.插入: 插入算法: 前提是数组中的数据必须是有序的 public static void main(String[] args) { // 先定义一个int类型的数组 int[] nums = n ...

- asp.net MVC之AuthorizeAttribute浅析

AuthorizeAttribute是asp.net MVC的几大过滤器之一,俗称认证和授权过滤器,也就是判断登录与否,授权与否.当为某一个Controller或Action附加该特性时,没有登录或授 ...