多路选择器,加法器原理及verilog实现

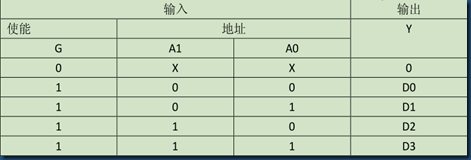

1.数据选择器是指经过选择,把多个通道的数据传到唯一的公共数据通道上。实现数据选择功能的逻辑电路称为数据选择器,它的作用相当于多个输入的单刀多掷开关。本例程以四选一数据选择器(电平触发)为例。 四选一数据选择器书堆 4 个数据源进行选择, 使用量为地址 A1A0 产生 4 个地址信号,由 A1A0 等于“00” 、 “01” 、 “10” 、 “11”来选择输出,真值表如下:

对应的verilog代码为

module mux4(d0,d1,d2,d3,y,a,g);

input d0,d1,d2,d3; // 输入的四个数据

input g; // 输入使能端

input[1:0] a; // 输入的选择端

output y; // 输出数据

reg y; // 输出数据寄存器

always@(d0 or d1 or d2 or d3 or g or a) // 电平触发,当 d0,d1,d2,d3,a 有变化时

候、// 触发

begin

if(g==1'b0) //当 当 g 为 为 0 时候

y=1'b0; //y 置 置 0

else

case(a) // 判断 a 的取值,并作出相应的赋值

2'b00:y=d0;

2'b01:y=d1;

2'b10:y=d2;

2'b11:y=d3;

default:y=1'b0; //a 为其他值得条件下,y 赋予 0

endcase

end

endmodule

时序仿真结果:

2.加法器是一种较为常见的算术运算电路,包括半加器(对两个输入数据相加,输出一个结果位和进位,没有进位输入的电路),全加器(有进位输入)。

如题,实现一个四位全加器:

module add4(a,b,ci,s,co);

input [3:0] a,b; // 输入四位数据 a ,b

input ci; // 输入进位 ci

output [3:0] s; // 输出四位数据 s

output co; // 输出进位 co

assign {co,s}=a+b+ci; //把 把 a 、b 、ci 相加后的结果赋予 co 、s ,其中 co

// 放最高位,s 放低三位

endmodule

多路选择器,加法器原理及verilog实现的更多相关文章

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- 多路选择器实现总线结构——Verilog

////////////////////////////////////////////////////////////////////////////////// //该程序完成通过多路选择器MUX ...

- 格雷码原理与Verilog实现

格雷码原理 格雷码是一个叫弗兰克*格雷的人在1953年发明的,最初用于通信.格雷码是一种循环二进制码或者叫作反射二进制码.格雷码的特点是从一个数变为相邻的一个数时,只有一个数据位发生跳变,由于这种特点 ...

- 多路选择器(multiplexer)简介

1.多路器简介 简称:多路器 功能:多输入 单输出 组合逻辑电路 2.verilog代码实现: module Mux_8(addr,in1,in2,in3,in4,in5,in6,in7,in8 ...

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 【接口时序】3、UART串口收发的原理与Verilog实现

一.软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45- ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

随机推荐

- wireshark抓包新手教程(win10空包问题)

首先下载官网的wireshark,下载地址https://www.wireshark.org/ 下载完按照提示一步步安装 安装完打开wireshark,安装中文包 安装之前首先讲一下win10截图工具 ...

- MongoDB 增删改查 Shell使用及操作

下载链接:https://robomongo.org/download 安装步骤省略,下一步下一步... 图形界面,连接默认,取个名字就行. 连接成功,可以愉快的使用了,不用总是敲命令了,简洁方便,多 ...

- java之struts2之文件下载

1.在实际应用开发中,文件下载功能也非常常见. 2.最简单的文件下载方式是通过超链接来进行文件下载: <body> <a href="download/s.txt" ...

- Matlab图形绘制

图形绘制 离散函数图形: 例:离散数据和离散函数可视化(离散数据作图方式) X1=[,,,,,,,,,,,,,,,,,,,]; Y1=[,,,,,,,,,,,,,,,,,,,]; figure() p ...

- NEST 根据id查询

想要在NEST里根据id查询 GET /employee/employee/1 可使用Get方法 public IGetResponse<employee> GetDoc() { var ...

- Install Gnome desktop

Install Gnome desktop http://www.dinggd.com/index.php/freebsd-8-0-rc1-gnome%E6%A1%8C%E9%9D%A2%E5%AE% ...

- React Native 开发豆瓣评分(二)路由配置

路由管理使用官方推荐的 React Navigation; 配置环境 安装相关依赖 yarn add react-navigation react-native-gesture-handler Lin ...

- CSS两列布局

方法1:左边设置绝对定位,右边设置左外边距,大小和左边的宽度相等 //CSS部分: .contain{ position :relative; height: 300px; } .left{ posi ...

- mysql 安装与基本管理

目录 mysql 安装与基本管理 MySQL介绍 下载安装 登录设置密码 破解密码 统一字符编码 mysql参数配置 mysql 常用指令 mysql 安装与基本管理 MySQL介绍 MySQL是一个 ...

- SQL SERVER-Exclusive access could not be obtained because the database is in use. (Microsoft.SqlServer.SmoExtended)

Q:先在一个实例中恢复一个数据A,然后又想在恢复一次,取别名为A2,这是报异常SQL SERVER-Exclusive access could not be obtained because the ...