Scan Synthesis Review

Review

- scan replacement - 将normal DFF替换为mux gate DFF

- scan stitching - 将DFF连接起来

- scan的作用:将测试困难的时序逻辑转变为易于测试的组合逻辑

- scanc测试过程:包含对于组合逻辑测试和时序逻辑测试两个过程,对于时序逻辑进行测试就是对于scan chain进行测试

时序逻辑测试

1.切换到scan mode(scan enable拉高)

2.scan input输入固定的pattern,一拍一拍进行输入

3.scan output接收pattern,一拍一拍接收

组合逻辑测试

1.切换到scan mode

2.输入test pattern(PPIs)

3.切换到function mode,输入(PIs)

4.测试POs

5.捕获组合逻辑的响应进行锁存

6.切换到scan mode

7.scan out

How to design scan clock structure

- 设计多为同步设计,同步设计都是通过时钟进行驱动的

- function design - 对于不同的clock domain进行单独的check,不同clock domain之间的关系是不check的

- 不同时钟域的DFF,在插入scan chain的时候如何考虑?

- 如果Design只有一个clock,做scan的时候可以使用function mode下的clock

- 一般在一个芯片中会有几十个或者是上百个clock domain,对于function clk,保证各个clk之间相互没有关系即可

- 对于scan clk而言,io数量是非常有限的(几百个或者几十个),例如一个芯片中有50个clk domain,其中一种方法可以将50个function clk拉出来进行测试,但是实际上在进行scan的时候是不会给那么多clk port,剩下的进行scan channel的数量就很少

- 在考虑scan clk的时候,为了节约IO数量,进行clk merge或者clk group

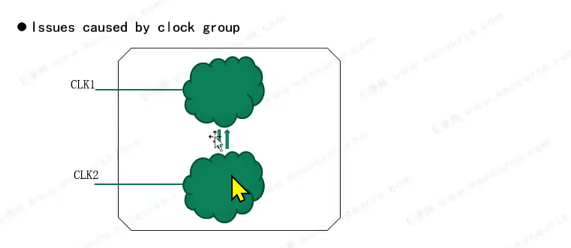

- 进行时序分析的时候认为clk1和clk2是异步的,进行timing check的时候都是分开考虑的

- 两个逻辑之间的数据交互通过设计方面进行解决:比如使用异步FiFo,实现两个时钟域进行信息交互或者使用两级或者三级同步器进行保证跨时钟域方式进行处理,通过同步设计的方法进行解决不是通过STA的方式进行解决

- 如果将这两个时钟进行merge,在timing check的时候,在进行STA的时候,不同的mode都需要进行check,但是不同的mode,使用的clk是不同的,如果时钟进行时钟的merge之后,就容易出现问题

- clk merge可能会增加额外的STA timing check和PR fixed timing violation

- 将没有交互的clk可以合并到一个clk,将交互比较少的clk进行merge,相近的频率的时钟可以merge在一起

Scan Synthesis Review的更多相关文章

- scan design flow(二)

在scan stitch之后,scan synthesis就已经完成, Scan extraction主要用来从scan design中extracing所有的instance,来保证scan cha ...

- scan design flow(一)

一个典型的scan实现的flow: clock mux和一些rst,在Scan中都被bypass掉,是不能测到的.所以DFT的test coverage一般就在97%或98%. scan design ...

- Logic and Fault simulation

fault simulation是指对fault circuit的simulation,来locate manufacturing defects并且进行fault diagnosis. logic ...

- Security Testing Basics

Security Testing BasicsSoftware security testing is the process of assessing and testing a system to ...

- (转)Deep Learning Research Review Week 1: Generative Adversarial Nets

Adit Deshpande CS Undergrad at UCLA ('19) Blog About Resume Deep Learning Research Review Week 1: Ge ...

- The 10 Best Choices On The Market Review 2018

Looking to buy a scan tool or considering one of Autel Scanner impressive product line?. The company ...

- 【云迁移论文笔记】Cloud Migration Research:A Systematic Review

Cloud Migration Research:A Systematic Review Author Info: Pooyan Jamshidi PhD Postdoctoral Researche ...

- 由学习《软件设计重构》所想到的代码review(一)

前言 对于一个程序猿来讲怎样来最直接的来衡量他的技术能力和产出呢?我想最直观的作法是看他的代码编写能力,就拿我常常接触的一些程序猿来看,他们买了非常多技术重构类书籍.可是看完后代码编写能力并没有显著提 ...

- How to transform the day time images to night time ? A series of paper review and some thinkings about this point.

How to transform the day time images to night time ? A series of paper review and some thinkings ab ...

- Paper Review: Epigenetic Landscape, Cell Differentiation 01

Today, I'll share a review papers about Epigenetic Landscape, the Epigenetic Landscape is related to ...

随机推荐

- C++ 核心指南 —— 性能

C++ 核心指南 -- 性能 阅读建议:先阅读 <性能优化的一般策略及方法> 截至目前,C++ Core Guidelines 中关于性能优化的建议共有 18 条,而其中很大一部分是告诫你 ...

- 数字孪生结合GIS能给物流行业带来怎样的改变

随着科技的不断发展和创新,数字孪生技术和地理信息系统(GIS)正日益在各个行业中发挥重要作用.其中,物流行业作为一个复杂而庞大的系统,也能从数字孪生和GIS的结合中获得许多益处和改变. 数字孪生是指通 ...

- ImportError: No module named pypinyin

import platform, subprocess, os, zipfile, xml, re, pypinyin ImportError: No module named pypinyin pi ...

- 从零玩转设计模式之简单工厂设计模式-jiandangonchangmoshi

title: 从零玩转设计模式之简单工厂设计模式 date: 2022-12-08 11:31:19.472 updated: 2022-12-11 23:03:34.805 url: https:/ ...

- hwclock详解

linux下hwclock命令详解 hwclock(hardware clock) 功能说明:显示与设定硬件时钟. 语 法:hwclock [--adjust][--debug][--directis ...

- Spring表达式语言(SPEL)学习(03)

rootObject 在表达式中直接写name和getName(),这时候Expression是无法解析的,因为其不知道name和getName()对应什么意思 @Test public void t ...

- Linux系统快速入门(完整版)

LINUX基础知识 I.Linux概述 linux是啥? 一套免费使用和自由传播的类Unix操作系统,是一个基于POSIX和Unix的多用户.多任务.支持多线程和多CPU的操作系统.它能运行主要的Un ...

- 4种方法帮你解决IntelliJ IDEA控制台中文乱码问题

摘要:在本文中总结了4 种方法完美解决 IntelliJ IDEA 控制台中文乱码问题. 前言 IntelliJ IDEA 如果不进行配置的话,运行程序时控制台中文乱码问题会非常严重,严重影响我们对信 ...

- 鸿蒙轻内核源码分析:MMU协处理器

摘要:本系列首先了解下ARM CP15协处理器的知识,接着介绍下协处理器相关的汇编指令,最后分析下MMU相关汇编代码. 本文分享自华为云社区<鸿蒙轻内核A核源码分析系列六 MMU协处理器> ...

- 从java到JavaScript(1),看Dart:对比Java/Go/Swift/Rust

关于 JIT与AOT,之前整理过<JIT-动态编译与AOT-静态编译:java/ java/ JavaScript/Dart乱谈>,一文不足以概括dart. 从编程语言生态看Dart 大多 ...