【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

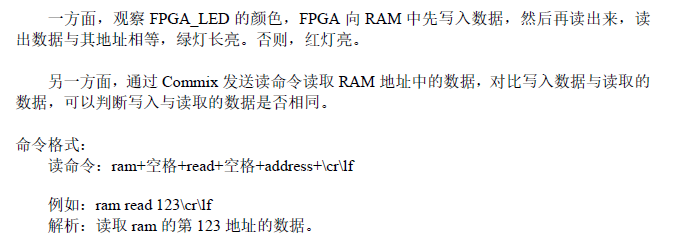

实验现象:

核心代码:

module DUAL_PORT_RAM(

input CLK_12M,

inout WR,

input RD,

input CS0,

input [:]A,

inout [:]DB,

output FPGA_LEDR,

output FPGA_LEDG,

output FPGA_LEDB

);

//-------------------------------rst_n---------------------------------//

reg rst_n;

reg [:]cnt_rst; always@(posedge CLK_12M)

begin

if(cnt_rst=='d10)

begin

rst_n <= 'd1;

cnt_rst <= 'd10;

end

else cnt_rst <= cnt_rst + 'd1;

end //---------------------------------PLL--------------------------------//

//实例化PLL

my_pll u1(

.inclk0(CLK_12M),

.c0(PLL_48M)

); //--------------------------------RAM---------------------------------//

//实例化双口ram

wire [:]a_dataout;

wire [:]b_dataout; my_ram u2(

.address_a(a_addr),

.address_b(A),

.data_a(a_datain),

.data_b(DB),

.clock_a(!a_clk),

.clock_b(b_clk),

.wren_a(a_wren),

.wren_b('d0),

.rden_a(a_rden),

.rden_b(!rd),

.q_a(a_dataout),

.q_b(b_dataout)

); //-------------------------------delay-------------------------------//

//对CLK_12M做延时处理

reg clk1,clk2; always@(posedge PLL_48M or negedge rst_n)

begin

if(!rst_n)

begin

clk1 <= 'd0;

clk2 <= 'd0;

end

else

begin

{clk2,clk1} <= {clk1,CLK_12M};

end

end wire a_clk = (CLK_12M & clk2); //---------------------------------ram_cnt----------------------------//

//ram地址数据计数器

reg [:]cnt_addr; always@(posedge CLK_12M or negedge rst_n)

begin

if(!rst_n)

begin

cnt_addr <= 'd0;

end

else if(cnt_addr=='d511)

begin

cnt_addr <= 'd0;

end

else cnt_addr <= cnt_addr + 'd1;

end //------------------------------ram_a wr&rd----------------------------//

reg a_wren,a_rden;

reg [:]a_datain;

reg [:]a_addr; always@(posedge a_clk or negedge rst_n)

begin

if(!rst_n)

begin

a_wren <= 'd0;

a_rden <= 'd0;

a_datain <= 'd0;

a_addr <= 'd0;

end

else if(cnt_addr >= 'd0 && cnt_addr <= 10'd255)

begin

a_wren <= 'd1;

a_datain <= cnt_addr;

a_addr <= cnt_addr;

a_rden <= 'd0;

end

else if(cnt_addr>='d256 && cnt_addr <= 1'd511)

begin

a_rden <= 'd1;

a_addr <= cnt_addr - 'd256;

a_wren <= 'd0;

end

end //------------------------------a_ram_error---------------------------//

//判断读取地址与输出数据是否相等。相等,绿灯亮;不相等,红灯亮。

reg error;

reg [:]led; always@(negedge clk1 or negedge rst_n)

begin

if(!rst_n)

begin

error <= 'd0;

end

else if(a_wren || a_dataout == a_addr)

begin

error <= 'd0;

led <= 'b101;

end

else

begin

error <= 'd1;

led <= 'b011;

end

end assign {FPGA_LEDR,FPGA_LEDG,FPGA_LEDB} = led; //-------------------------------b_ram_rd-----------------------------//

//控制ram_b的读取功能,当读信号来临时,读取数据发送到FSMC总线上

wire wr = (CS0 | WR );

wire rd = (CS0 | RD);

reg wr_clk1,wr_clk2; always@(posedge PLL_48M or negedge rst_n)

begin

if(!rst_n)

begin

wr_clk1 <= 'd1;

wr_clk2 <= 'd1;

end

else

begin

{wr_clk2,wr_clk1} <= {wr_clk1,wr};

end

end

wire b_clk = (!wr_clk2 | !rd);

assign DB = !rd ? b_dataout : 'hzzzz; //------------------------------endmodule-----------------------------//

endmodule

实验方法及指导书:

链接:http://pan.baidu.com/s/1hsEeYxe 密码:004h

【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

- 【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf 读RAM命令格式:read:地址(0-255)\cr\lf 核心代码: int main(void) ...

- 【iCore3 双核心板_FPGA】实验十八:基于单口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1i58Ssvz iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore4 双核心板_FPGA】例程十七:基于FIFO的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int fsmc_read_data; ; ]; ]; char *p; /* ...

- 【iCore3 双核心板】例程十七:USB_MSC实验——读/写U盘(大容量存储器)

实验指导书及代码包下载: http://pan.baidu.com/s/1qXt1L0o iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板_FPGA】实验二十:基于FIFO的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1cmisnO iCore3 购买链接: https://item.taobao.com/item.htm?id=5242294 ...

- 【iCore1S 双核心板_FPGA】例程二:GPIO输入实验——识别按键输入

实验现象: iCore1s 双核心板上与FPGA相连的三色LED(PCB上标示为FPGA·LED),按键按下红灯点亮,松开按键红灯熄灭. 核心源代码: module KEY( input CLK_12 ...

随机推荐

- Android应用源码 概览

之前我讲过关于Android应用源码的使用,不要走弯路,没有用的源码不要深究. 记住目录就好. 这里还有很多源码, Javaapk这个网站里的.还有很多. 这些源码 有可能有用. 但是不必故意用它. ...

- c#取数据库数据 ---两种方法

通常有以下两种方式 SqlDataReader 和SqlDataAdapter|DataSet方式 SqlDataReader 方式使用方式如下: using System; using System ...

- LOJ.6073.[2017山东一轮集训Day5]距离(可持久化线段树 树链剖分)

题目链接 就是恶心人的,简单写写了...(似乎就是[HNOI2015]开店?) 拆式子,记\(dis_i\)为\(i\)到根节点的路径权值和,\(Ans=\sum dis_{p_i}+\sum dis ...

- Java并发编程(四)-- Java内存模型

Java内存模型 前面讲到了Java线程之间的通信采用的是共享内存模型,这里提到的共享内存模型指的就是Java内存模型(简称JMM),JMM决定一个线程对共享变量的写入何时对另一个线程可见.从抽象的角 ...

- Scrapy基础(十一)————导出数据到json文件中

之前介绍过将数据写入mysql数据库中,但是对于那些没有数据库的,可以通过写入json文件中或者是写入到csv或者xls:这里只介绍写入json文件中,也为再练习一下自定义的pipeline 思路: ...

- CY7C68013 USB接口相机开发记录 - 第一天:资料下载

一直觉得从头开发一套东西出来会极大的提升自己的自信心,能够最大化的开发自己的潜能.所以在犹豫很久之后决定学习下CY7C68013 USB接口相机的开发. 通过在网上查找多份资料后,觉得工欲善其事必先利 ...

- 小甲鱼Python第十讲课后题---

0. 下边的列表分片操作会打印什么内容? >>> list1 = [1, 3, 2, 9, 7, 8]>>> list1[2:5] [2,9,7] 1.请问 lis ...

- web 和 java 资源

1.自己按照上面的网址和密码自己去下载都那些视频都是vip的视频现在下载免费 7-17JAVA开发搜索引擎自动提示[优效学院向天] 链接:http://pan.baidu.com/s/1bpEkfR ...

- Codeforces909C Python Indentation(动态规划)

http://codeforces.com/problemset/problem/909/C dp[i][j]表示第i行缩进j的方案数. 当第i-1行为f时,无论当前行是f或s都必须缩进,即dp[i] ...

- 邮轮ERP系统

近两年一直做邮轮旅游方面的系统开发,最近有点时间,就花了两三个月,开发了一套邮轮ERP. 感兴趣的同学可以给我留言(904308112@qq.com),一起交流学习.