串口接收端verilog代码分析

串口接收端verilog代码分析

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/05/23 16:14:30

// Design Name:

// Module Name: uart_rx

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module uart_rx( input wire clk,

input wire rxd,

output reg [:]data_i,

output wire receive_ack ); reg [:] data_i = ; localparam IDLE = ,

RECEIVE = ,

RECEIVE_END = ; reg [:]cur_st = ;

reg [:]nxt_st = ;

always @(posedge clk)

begin

cur_st <= nxt_st;

end always @(*)

begin

nxt_st = cur_st; case(cur_st) IDLE:

begin

if(!rxd) //当从接收端口上进来的数据开始为0时,即启动接收

nxt_st = RECEIVE;

end RECEIVE:

begin

if(count == )

nxt_st = RECEIVE_END;

end RECEIVE_END:

begin

nxt_st = IDLE;

end default:

begin

nxt_st = IDLE;

end endcase end reg [:]count = ;

always @(posedge clk)

begin

if(cur_st == RECEIVE)

count <= count + ;

else if(cur_st == IDLE || cur_st == RECEIVE_END)

count <= ;

end //当前状态为接收状态时,rxd 信号线上的数据存储在data_i的最高位

//同时data_i 的数据总体右移一位

always @(posedge clk)

begin

if(cur_st == RECEIVE)

begin

data_i[:] <= data_i[:];

data_i[] <= rxd; // rxd 传过来什么数据, data_i上立马显示什么数据,因为是从端口采集到的数据

end end assign receive_ack = (cur_st == RECEIVE_END) ? : ; endmodule /* add_force {/uart_rx/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/uart_rx/rxd} -radix hex {1 0ns} {0 300ns} {1 400ns} {0 500ns} {1 600ns} {0 700ns} {1 800ns} {0 900ns} {1 1000ns} */

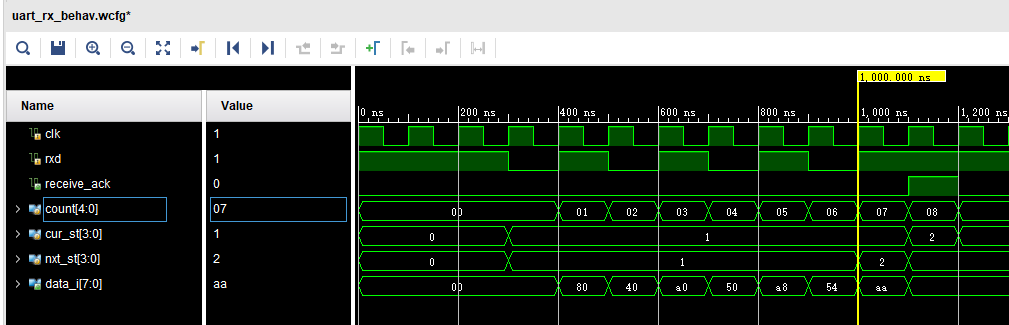

仿真结果:

注意:

分析寄存器的更新一定要结合时钟沿,然后寄存器在时钟沿前后的变化状态。

串口接收端verilog代码分析的更多相关文章

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- Linux内核中的GPIO系统之(3):pin controller driver代码分析

一.前言 对于一个嵌入式软件工程师,我们的软件模块经常和硬件打交道,pin control subsystem也不例外,被它驱动的硬件叫做pin controller(一般ARM soc的datash ...

- Bluez SPP实现代码分析(转)

源:http://blog.csdn.net/walkingman321/article/details/7218705 本文分析蓝牙协议栈中蓝牙转串口(SPP)部分的实现. 1. 基本概念 Blu ...

- ISD9160学习笔记05_ISD9160语音识别代码分析

前言 语音识别是特别酷的功能,ISD9160的核心卖点就是这个语音识别,使用了Cybron VR 算法. 很好奇这颗10块钱以内的IC是如何实现人家百来块钱的方案.且听如下分析. 本文作者twowin ...

- 2017-2018-2 《网络对抗技术》 20155322 Exp4 恶意代码分析

[-= 博客目录 =-] 1-实践目标 1.1-实践介绍 1.2-实践内容 1.3-实践要求 2-实践过程 2.1-Mac下网络监控 2.2-Windows下网络监控 2.3-Mac下恶意软件分析 2 ...

- STM32F103片外运行代码分析

STM32F103片外运行代码分析 STM32F103有三种启动方式: 1.从片内Flash启动: 2.从片内RAM启动: 3.从片内系统存储器启动,内嵌的自举程序,用于串口IAP. 无法直接在片外N ...

- Linux内核中的GPIO系统之(3):pin controller driver代码分析--devm_kzalloc使用【转】

转自:http://www.wowotech.net/linux_kenrel/pin-controller-driver.html 一.前言 对于一个嵌入式软件工程师,我们的软件模块经常和硬件打交道 ...

随机推荐

- opencv的resize和matlab的imresize函数的计算

在用c++代码复现matlab代码时,遇到两者resize函数的结果不相同的问题. opencv: resize(image1, reTmp, Size(, ), , , cv::INTER_LINE ...

- VXLAN, 一种叠加在L3网络上的L2网络

这几天看了下RFC7348,顺便翻译了一下,根据自己理解做了注解 虚拟化及租户隔离 服务器虚拟化增加了对物理网络基础设施的需求,服务器有多个虚机,要求交换机支持更大的MAC地址表. 在数据中心场景下, ...

- Bilinear CNN与 Randomly Wired Neural Network

最近主要学习了两篇论文以及相关的代码. 1.Bilinear CNN 这篇论文主要是在细粒度分类上应用的,在全连接层之前,在所有的卷积计算完成之后,进行的Bilinear计算,关键的代码如下: def ...

- dedecms 在模版页面获取当前栏目id

在模版中单独调用当前栏目id {dede:type}[field:ID /]{/dede:type} 在{dede:sql}中调用当前栏目id {dede:sql sql='Select * from ...

- Lua 语言变量

Lua 变量 变量在使用前,必须在代码中进行声明,即创建该变量.编译程序执行代码之前编译器需要知道如何给语句变量开辟存储区,用于存储变量的值. Lua 变量有三种类型:全局变量.局部变量.表中的域. ...

- JAVA中经过nginx反向代理获取客户端ip并获取相关坐标等信息

关于搜狐新浪ip库查询接口的使用 直接输出访客ip及所在城市: <script src="http://pv.sohu.com/cityjson?ie=utf-8" > ...

- zzw_rsync命令中的/的作用

[root@sv0379 rsync]# rsync -vzrtopg --password-file=/usr/local/rsync/rsync.passwd /opt/aspire/prod ...

- Module(模块)

1.每个Angular至少有一个根Module 2.Module时一个带有@NgModule装饰符的类 3.最简单的Module import { NgModule } from '@angular/ ...

- UVa LA 4254 - Processor 二分,贪心 难度: 1

题目 https://icpcarchive.ecs.baylor.edu/index.php?option=com_onlinejudge&Itemid=8&page=show_pr ...

- [Java] [Lock] [Synchronized VS ReentrantLock]

Overview java编写多线程程序时,为了保证线程安全,需要对数据进行同步,经常用到的两种同步方式就是synchronized和重入锁ReentrantLock. 相似点 都是加锁方式 都是阻塞 ...