verilog 硬件描述语言

第一章 绪论

verilog--数字电路设计技术--ASIC/SOC芯片设计--协议pcie SATA USB--系统知识(个人计算机,芯片组,网络连接,嵌入式系统,硬件和软件的互操作)

第二章 寄存器传输语言 RTL(Register Transfer Language)

第三章 可综合的verilog--用于电路设计

3.3 verilog的结构

块(block)--子块(sub-block)--模块(module)

触发器:D,RS,JK,

3.7 组合逻辑 always变量为reg类型,assign变量为wire类型3.7 组合逻辑 always变量为reg类型,assign变量为wire类型

3.7.1 always块语句

- 使用(*)代表敏感信号,包括reset_center和center1.always块语句 使用(*)代表敏感信号,有reset_center和center

- 阻塞赋值符号“=”

- 内部第一句描述了cnter_nxt的默认值(大多数情况下cnter_nxt的取值),敏感信号变化时always块执行并重新计算cnter_nxt的值

- 开始为变量分配默认值,确保不会生成锁存器,之后用if-else语句获得cnter_nxt值

- 如果有一个以上语句需要在一定条件下执行放在begin-end结构中

- 只有一条语句就不需要begin-end

3.7.2 case和if-else语句

- case语句只能有1比特为1

3.8 操作符

- 一个是按位,两个就是逻辑

&&逻辑与 &按位与

||或

!逻辑非 ~按位非 ^按位异或 ~^按位异或非

缩位 &与 |或 ^异或 ~&与非 ~|或非 ~^异或非

==相等 !=不等于 > >= < <= + - * / {}并位 <<向左位移 >> ?条件运算符 %求模 **指数 - 执行顺序 尽量使用括号,括号优先执行

- 注释 //单行注释 或者 多行/**/

3.9 可重用模块化设计

- 可重用模块化设计:同一个电路单元可在不同的芯片中使用,常用的包括parameter,function,generate,`ifdef等

parameter使用方法:参数在使用前需要被提前定义,可以在模块中被定义也可以在include头文件中定义,如chiptop_parameter.vh,模块例化时可以将不同值传递到模块内部。FIFO(First in first out,先入先出) - 参数文件扩展名是.vh,包含芯片的全局参数,顶层参数文件中建议采用较长参数名。不同层次上有多个不同参数,需要确定参数是否唯一。

- Verilog函数 用来生成可综合的组合逻辑 函数有多个输入信号和一个输出信号,综合后得到组合逻辑,其内部不能出现时间控制相关语句,如wait,@或#

- generate结构 编译在综合和仿真之前,

- `ifdef结构用于模块设计 先创建一个chiptop_defines.vh的文件,将定义的字符串放在文件里面,使用include插入字符串语句之前。 ifdef-else if-else-endif,mux语句综合后会出现多个分支,ifdef只有一个

3.9.5 数组

定义一个深度128,位宽32的存储器

reg [31:0] memory[0:127];

Verilog supports multi-dimensional structures.

wire [7:0] ascii_char,

wire [7:0] abc [0:31] [0:15];

assign ascii_char=abc[10][2][7:0];

第四章 用于验证的Verilog的语法

4.1 测试平台 testbench

- DUT(Design Under Test,被测电路),Verilog中还有一些语法结构但不可综合。

4.2 initial语句

- 初始化变量,触 一句开始执行到最后一句,此后不再执行。

4.3 系统任务

- 电路仿真时,遇到$finish完成仿真并退出,一般放在testbench的顶层文件中,如果testbench_top.v是顶层仿真文件那么应在仿真结束时刻。

- $stop 停止仿真但不退出,提供一个命令提示符,在后面输入“.”继续进行

- $display 不可综合不能直接放在DUT的RTL代码中,将$display语句嵌入translate on与translate off之间,建议放在testbench中通过“.”指出信号在DUT中路径,显示需要观察的信号数值

- $monitor与display相似 仅当信号数值变化才显示

- $time返回当前仿真时间,tb中用timescale指出仿真时间单位(通常为1ns),当前时间是一个64位整数乘以timescale中的单位后取整得到的整数,不包括小数。realtime返回实数包括小数

- $random 返回一个32位带符号的随机整数。放入{}内可以得到非负整数。random(seed)中的seed是一个整数用于指出随机数的取值范围。被用于随机测试中。还可以描述不确定行为,比较器中输入值小于参考值输出0,大于输出1,相等都有可能。

- save("file name") 保存当前仿真信息

- readmemh从一个文本中读取数据,tb产生测试激励的一种方式先将要使用的数据存在文件中,仿真时使用readmemh读取并产生激励波形。

- writememh 将数据写入文本,好分析仿真过程。

- fopen("file name");打开文件 fclose(file1);关闭文件

4.4 任务

任务和函数很相似。可以将一段代码定义为一个任务,然后在不同地方多次调用该任务。任务可以自定义自己的输入输出端口,可以定时控制,如@posedge clk、non-zero timings和#10等时间控制语句。任务按顺序执行,仿真器会等到定时条件满足才执行后续的语句。如当遇到@posedge clk时,程序只在出现时钟上升沿时才执行,任务更多用于tb而不是DUT

4.5 存储器建模

通过定义二维寄存器数组的方式定义存储器,SRAM(Static Random Access Memory,静态随机存取存储器),定义一个深度为1k,位宽为8字节的存储器:

reg [7:0] OneKByte [1023:0];

wire [7:0] byte_9;

4.6 while循环

- while建议加入定时控制语句如@posedge clk或#5,以避免形成定时环路。

- for循环语句可用于tb或可综合的RTL代码中

- repeat(5)

- force将一个固定值(1,0)强制赋予一个变量。release执行前无论变量怎么被驱动,值都不变,执行后由具体驱动决定

- fork/join 是并行的,先执行内部再后面

4.7 一个简单的tb文件

//生成clk_tb

initial begin

clk_tb=1'b0;

forever begin

#CLKTB_HALF_PERIOD clk_tb=~clk_tb;

end

end

//生成resetb

resetb =1'b0;

#100 resetb=1'b1;

第五章 数字电路设计

5.1 组合逻辑门

组合逻辑门和触发器的存储元件组成数字电路

5.1.1 逻辑 1 和逻辑 0 模拟电压,低于某个门限的电压值代表0,高于一定门限的代表1,各自门限之差称为噪声容限。

5.1.2 真值表

5.1.3 晶体管 n型和p型

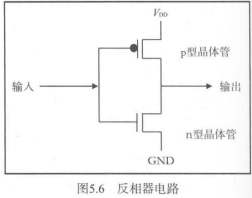

5.1.4 反相器

一个输入一个输出端,由一个p型和一个n型晶体管串联而成

对于CMOS逻辑门来说,只有当逻辑值发生变化时才有电流流过晶体管。

5.1.5

- 与门,一般最多五个输入,可以级联用 O=AB

- 或门 0=A+B

- 与非门 O=(AB)'

- 或非门 O=(A+B)'

- 异或XOR 不同输出1 异或非XNOR 相同输出1

verilog 硬件描述语言的更多相关文章

- 我的 FPGA 学习历程(04)—— 练习 verilog 硬件描述语言

这篇讲的是使用 verilog 硬件描述语言编写一个 3 - 8 译码器. 3 - 8 译码器是一个简单的组合逻辑,用于实现并转串,其输入输出关系如下: | 输入 | 输出 | -------- ...

- 硬件描述语言Verilog设计经验总结

一.硬件描述语言Verilog 粗略地看Verilog与C语言有许多相似之处.分号用于结束每个语句,注释符也是相同的(/* ... */和// 都是熟悉的),运算符"=="也用来测 ...

- 上一步是硬件描述语言,下一步是FPGA

上一步是硬件描述语言,下一步是FPGA. 学习了硬件描述语言(Verilog或者VHDL)之后,FPGA该如何继续. 世上没有捷径,每一步都得踏踏实实的走.学习FPGA也是这样,在有了硬件描述语言的基 ...

- WSDL(Web服务描述语言)详细解析(全文转载学习用)

WSDL (Web Services Description Language,Web服务描述语言)是一种XML Application,他将Web服务描述定义为一组服务访问点,客户端可以通过这些服务 ...

- WSDL(WebService描述语言)文件介绍

一.WSDL 1.WSDL 文档的组成部分 <portType>:web service 执行的操作 <message>:web service 使用的消息 <types ...

- API的描述语言--Swagger

Swagger是一种Rest API的表示方式. 有时也可以作为Rest API的交互式文档,描述形式化的接口描述,生成客户端和服务端的代码. 一,描述语言:Spec Swagger API Spec ...

- Blazor 002 : 一种开历史倒车的UI描述语言 -- Razor

Razor是一门相当怪异丑陋的标记语言,但在实际使用中却十分高效灵活.本文主要介绍了Razor是什么,以及Razor引擎的一些浅薄的背后机理. 写文章前我本想一口气把Razor的基本语法,以及Blaz ...

- TCAM CAM 说明 原理 结构 Verilog 硬件实现

TCAM 三态内容地址查找存储器,CAM内容地址查找存储器.区别在于TCAM多了一级掩码功能,也就是说可以指定某几位是dont care.匹配的时候0,1都行的意思. 广泛应用于数据流处理领域,本文简 ...

- 从硬件到语言,详解C++的内存对齐(memory alignment)

转载请保留以下声明 作者:赵宗晟 出处:https://www.cnblogs.com/zhao-zongsheng/p/9099603.html 很多写C/C++的人都知道“内存对齐”的概念以及规则 ...

- 用verilog来描述组合逻辑电路

1,什么是组合逻辑电路? 逻辑电路在任何时刻产生的稳定的输出信号仅仅取决于该时刻的输入信号,而与过去的输入信号无关,即与输入信号作用前的状态无关,这样的电路称为组合逻辑电路. 上图给出了一个典型的数字 ...

随机推荐

- http 1.0、2.0、3.0 之间的区别

首先是HTTP协议: HTTP 是 HyperText Transfer Protocol(超文本传输协议)的缩写,它是互联网上应用最为广泛的一种网络协议,所有 WWW 文件都必须遵守这个标准.其他的 ...

- oralce sql 缓存查询及删除

--缓存查询语句 V$SQLAREA 视图记录sql 执行情况(加载次数/用时/Id....) 常用字段 ADDRESS:SQL语句在SGA中的地址. 这两列被用于鉴别SQL语句,有时,两条不同的语句 ...

- Wordpress 漏洞利用与后渗透

[作业]ColddBox 靶场 Wordpress 漏洞利用与后渗透. 突破口 渗透这类 CMS 网站时,不要上来就狂扫,它大部分目录都是固定的,开源去看对应版本,商业的找几篇文章.特别 注意的是一定 ...

- 富文本 HTML String 转化为 nodes 数组

https://github.com/ant-mini-program/mini-html-parser?spm=ding_open_doc.document.0.0.4ef9722fXz27PV

- NetBeans的一些快捷键

Alt + Insert getter 覆盖toString方法 Shift+ F6 运行当前文件 F6 运行当前项目 Tab 完成代码片段 ctrl+\ 代码补全 Alt + Shift + F格式 ...

- 【小记】copy 与 copy_backward

copy 与 copy_backward copy 从前往后复制,result 参数指向目标容器的 begin 位置 copy*backward 从后往前复制,··· end 位置 Possible ...

- go语言web框架-如何使用gin教程+react实现web项目

go-web+ react实践项目 前端使用react 搭建,从webpack搭建开始写,后端是学习go语言过程中的实践,由于之前没有实际的后端web经验,所以是自己一点一点摸索出来的.有错漏还望指正 ...

- redis的持久化方案RDB和AOF

RDB:快照形式,定期把内存中当前时刻的数据保存到磁盘.Redis默认支持的持久化方案.速度快但是服务器断电的时候会丢失部分数据 AOF形式:append only file.把所有对redis数据库 ...

- ComPiler200003:Story-Oriented Programming

Story-Oriented Programming MAY 25TH, 2018 http://www.brandonkeown.com/2018/05/story-oriented-program ...

- Python切换中英文输入法

要实现中英文切换,首先Windows系统必须要有中文语言和英文语言,才能实现输入法(语言)切换. import win32api import win32gui from win32con impor ...