Clock Gating Design

GPU max power distribution

- internal power and switch power - 动态功耗(时钟翻转)

- Leakage power - 漏电功耗(静态功耗,mos管导通的特性)

- clock_network - 时钟树的功耗,系统中有很多寄存器,但是时钟到达寄存器的时间是不同的,需要插入一些buffer,形成时钟网络,会有功耗

- combination - 组合逻辑功耗

- sequential - 时许逻辑

- memory - 存储功耗,系统中的memory比较多,功耗比较高

时钟树上的功耗是不能被忽略的,需要优化时钟树上的功耗

Clock Gating for Conventional RTL

- 在写寄存器的时候,需要设置使能信号,在使能信号的作用下,才能将D段的数据同步到Q端

- 添加CG就是一个与的逻辑,将clock与enable信号进行与操作,enable = 0,时钟不反转;enable = 1,输入就是时钟,时钟翻转

- ICG - 综合工具会自动进行插入,不需要手动进行例化,但是代码风格需要注意,给寄存器添加使能型信号

Clock Gating across - Module Boundartes

Clock Gating for Implicit Enable

- 工具会尽可能添加ICG,最好写代码的时候添加enable信号

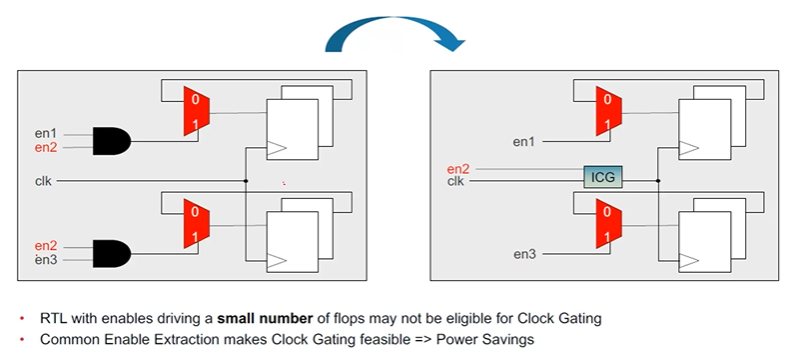

Automated Common Enable Extraction

always @ (posedge clk)begin

if(en0 && en1)

a_r <= a_nxt;

end

reg [1:0] b_r;

always @ (posedge clk)begin

if(en1 && en2)

b_r <= b_nxt;

end

- 寄存器数据位宽小于4bit,工具是不会插入ICG的,因为插入ICG会有一些面积的产生

- a_r和b_r有共同的使能en1,工具会提取公共的使能端,生成ICG

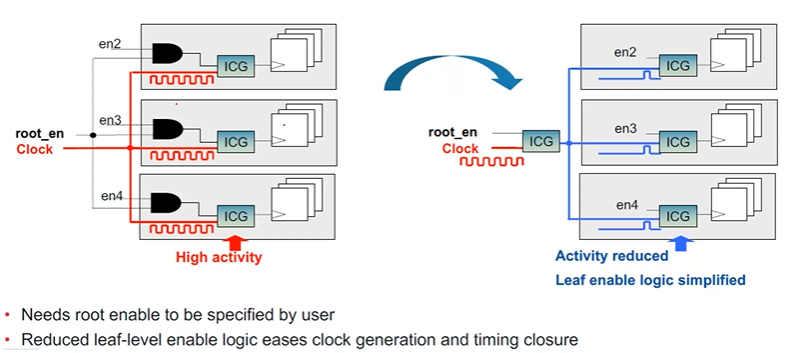

Multi-Stage Clock-Gating When CE is Specified

- ICG生成的时钟可以驱动其他的寄存器

- 时钟路径比较长,导线和buffer上时钟翻转也会产生功耗,几个寄存器前一级有公共的使能端,可以在前一级设置一个ICG,能供降低导线和buffer上的时钟翻转,降低功耗

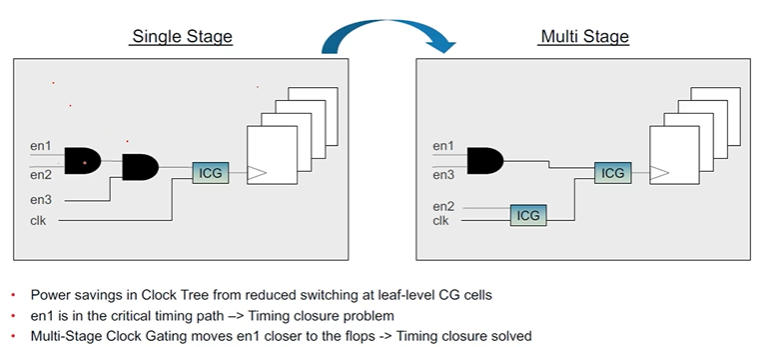

Multi-Stage Clock—Gating

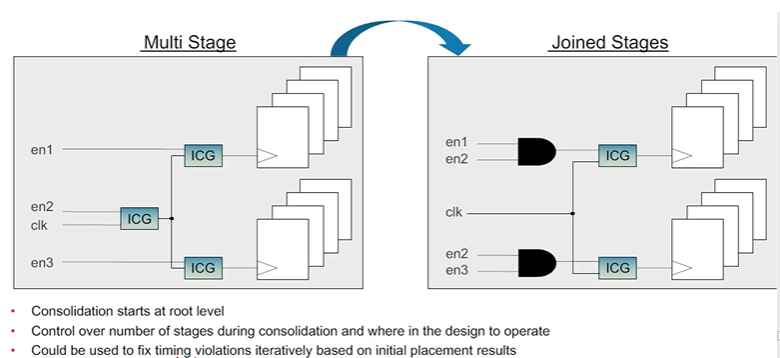

Consolidating Multi-Stage Clock Gating

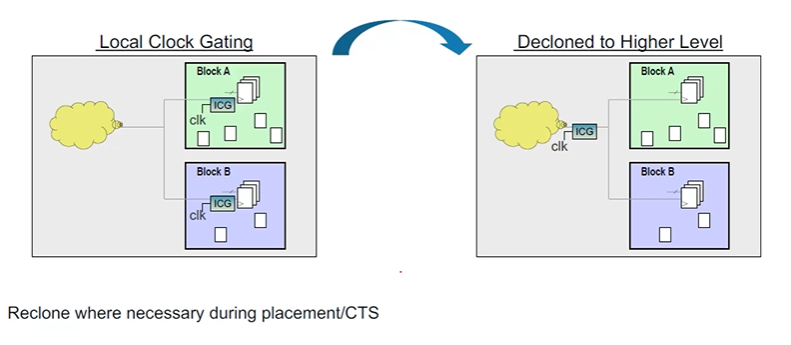

"Decloning" Local Clock Gating

Clock Gating Design的更多相关文章

- clock gating and PLL

一个gating的clock是指:clock network除了包含inverter和buffer外,还有其他logic. PrimeTime会自动的对gating input进行setup和hold ...

- clock gating check

在 sta 分析时,经常会碰到 clock gating cell (一般是 ICG cell 或者 latch)引起的 violation,这种 violation 很常见,而且往往很难修. 为什么 ...

- clock时钟

①时钟的偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(cloc ...

- [ZZ] GTX 280 GPU architecture

http://anandtech.com/show/2549 Now that NVIDIA’s has announced its newest GPU architecture (the GeFo ...

- lower power的IP设计

在IP的实现过程中,考虑lower power部分进行设计: 1)Partition the design来满足lower power的一些strategies,尤其是power gating和clo ...

- 数字IC设计入门书单

首发于观芯志 写文章 数字IC设计入门书单 Forever snow 1 年前 作者:Forever snow链接:你所在领域的入门书单? - 知乎用户的回答来源:知乎著作权归作者所有,转 ...

- 推荐 的FPGA设计经验(2)-时钟策略优化

Optimizing Clocking Schemes Avoid using internally generated clocks (other than PLLs) wherever possi ...

- NVIDIA---CUDA

http://en.wikipedia.org/wiki/CUDA CUDA From Wikipedia, the free encyclopedia CUDA Developer(s) N ...

- 最新内核3.4)Linux 设备树加载I2C client adapter 的流程(内核3.4 高通)【转】

转自:https://blog.csdn.net/lsn946803746/article/details/52515225 版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转 ...

- DFT测试-OCC电路介绍

https://www.jianshu.com/p/f7a2bcaefb2e SCAN技术,也就是ATPG技术-- 测试std-logic, 主要实现工具是: 产生ATPG使用Mentor的 Test ...

随机推荐

- int和String的相互转换

- CSS语法检查利器之csslint

本文于2015年底完成,发布在个人博客网站上. 考虑个人博客因某种原因无法修复,于是在博客园安家,之前发布的文章逐步搬迁过来. 背景 前段时间研究使用YUI Compressor压缩项目里的js和cs ...

- el-table 设置合并行或列时,显示错乱问题

1. 需求效果图: 2. 接口数据格式: 点击查看代码 const list = [ { contractNo: "CAI-20220801001", contractItem: ...

- SQL注入上传文件获取shell

SQL注入写文件的三个必要条件 Web目录有读写权限: 当目标网站的Web目录具有读写权限时,攻击者可以通过注入恶意SQL语句将恶意文件写入服务器上的Web目录. 知道文件的绝对路径: 攻击者需要知道 ...

- IPv6实现内网穿透,极低成本保姆级教程

摘要 一直想实现内网穿透从而达到随时随地可以连接到自己电脑的目的.尝试过使用一些付费的现成方案,但是价格偏高,而流量少得可怜,只能开放几个固定端口. 实现内网穿透的最大难点就在于拥有一个公网IP,但是 ...

- OCR性能优化:从认识BiLSTM网络结构开始

摘要: 想要对OCR进行性能优化,首先要了解清楚待优化的OCR网络的结构,本文从动机的角度来推演下基于Seq2Seq结构的OCR网络是如何一步步搭建起来的. 本文分享自华为云社区<OCR性能优化 ...

- Linux如何进行GPIO读写操作的?

摘要:本文介绍GPIO的读写,介绍基本原理,以及不同读写方式的性能. 本文分享自华为云社区<Linux 基于sysfs的GPIO读写操作>,作者:一颗小树x . 前言 最近接触到Linux ...

- 华为云GaussDB(for MySQL)2.0全新升级,三大技术大揭秘

摘要:9月23日,在华为全联接2021主会场,华为高级副总裁.华为云CEO.消费者云服务总裁张平安发表"深耕数字化,一切皆服务"主题演讲,并发布了GaussDB(for MySQL ...

- 云计算的三种模式IaaS/PaaS/SaaS/BaaS对比:SaaS架构设计分析

SaaS--软件即服务(Software as a Service)的出现改变了传统使用软件转变为使用服务. SaaS与传统软件的最大区别是,前者按年付费租用服务,后者一次买断.这貌似只是" ...

- vue2.x老项目typescript改造过程经验总结

前言: 关于Vue2.x 的TS改造,其实没有啥好说的. 对于vue-cli项目来说,从新跑一遍 vue create xxx-project ,选择Manually select features ...