【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

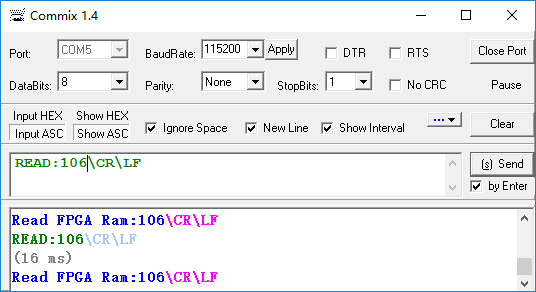

实验现象:

核心代码:

int main(void)

{ /* USER CODE BEGIN 1 */

int i;

int address,data;

char error_flag = ;

char receive_data[];

char buffer[];

char *p;

/* USER CODE END 1 */ /* MCU Configuration----------------------------------------------------------*/ /* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init(); /* USER CODE BEGIN Init */ /* USER CODE END Init */ /* Configure the system clock */

SystemClock_Config(); /* USER CODE BEGIN SysInit */ /* USER CODE END SysInit */ /* Initialize all configured peripherals */

MX_GPIO_Init();

MX_USART6_UART_Init();

MX_FMC_Init(); /* USER CODE BEGIN 2 */

usart6.initialize();

usart6.printf("Hello, I am iCore4!\r\n");

LED_GREEN_ON;

/* USER CODE END 2 */ /* Infinite loop */

/* USER CODE BEGIN WHILE */

while ()

{

/* USER CODE END WHILE */ /* USER CODE BEGIN 3 */

if(usart6.receive_ok_flag == ){

usart6.receive_ok_flag = ;

memset(receive_data,,sizeof(receive_data));

memset(buffer,,sizeof(buffer));

for(i = ;i < ;i ++){

receive_data[i] = usart6.receive_buffer[i];

}

p = receive_data;

i = ;

while(*p != ':'){ //»ñÈ¡²Ù×÷ÃüÁwrite or read£©

buffer[i++] = *p++;

if(i > sizeof(buffer))i = ;

}

for(i = ;i < sizeof(buffer);i++){//½«ÃüÁîת»¯ÎªÐ¡Ð´×Ö·û

buffer[i] = tolower(buffer[i]);

} if(memcmp(buffer,"read",strlen("read")) == ){//Ö´ÐжÁ²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

if(strchr(p,','))error_flag = ;

if(!error_flag){

data = fpga_read(address);

usart6.printf("Read FPGA Ram:%d\r\n",data);

}

}else{

error_flag = ;

} if(error_flag){

LED_RED_ON;

LED_GREEN_OFF;

usart6.printf("Bad Command!\r\n");

}else{

LED_RED_OFF;

LED_GREEN_ON;

}

}

}

/* USER CODE END 3 */ }

module dual_port_ram_ctrl(

input clk_25m,

input rst_n,

input wrn,

input rdn,

input cs0,

inout [:]db,

input [:]ab,

output led_red,

output led_green,

output led_blue

); //-----------------------------ram-----------------------------//

wire [:]dataout_a;

wire [:]dataout_b; ram u1(

.data_a(data_a),

.address_a(address_a),

.wren_a(wren_a),

.rden_a(rden_a),

.clock_a(!clk_a),

.q_a(dataout_a), .data_b(db),

.address_b(ab),

.wren_b('d0),

.rden_b(!rd),

.clock_b(clk_b),

.q_b(dataout_b)

); //-----------------------------clk_100m-----------------------------// pll u2(

.inclk0(clk_25m),

.c0(clk_100m)

); //-------------------------------clk_a-----------------------------//

reg clk1,clk2;

always@(posedge clk_100m or negedge rst_n)

if(!rst_n)

begin

clk1 <= 'd0;

clk2 <= 'd0;

end

else

{clk2,clk1} <= {clk1,clk_25m}; wire clk_a = (clk_25m & clk1); //-------------------------------data-----------------------------//

reg [:]data;

always@(posedge clk_25m or negedge rst_n)

if(!rst_n)

data <= 'd0;

else if(data == 'd511)

data <= 'd0;

else

data <= data + 'd1; //-------------------------write & read port a-------------------//

reg wren_a;

reg rden_a;

reg [:]data_a;

reg [:]address_a; always@(posedge clk_a or negedge rst_n)

if(!rst_n)

begin

wren_a <= 'd0;

rden_a <= 'd0;

data_a <= 'd0;

address_a <= 'd0;

end

else if(data >= 'd0 && data <= 10'd255)

begin

wren_a <= 'd1;

rden_a <= 'd0;

data_a <= data;

address_a <= data;

end

else if(data >= 'd256 && data <= 10'd511)

begin

wren_a <= 'd0;

rden_a <= 'd1;

address_a <= data - 'd256;

end //-----------------------------ram a---------------------------//

reg error; always@(negedge clk1 or negedge rst_n)

if(!rst_n)

error <= 'd0;

else

begin

if(wren_a || dataout_a == address_a)

error <= 'd0;

else

error <= 'd1;

end //--------------------------ram_a_led---------------------------//

reg ledr,ledg,ledb;

always@(posedge error or negedge rst_n)

if(!rst_n)

begin

ledr <= 'd1;

ledg <= 'd0;

ledb <= 'd1;

end

else

begin

ledr <= 'd0;

ledg <= 'd1;

ledb <= 'd1;

end

assign {led_red,led_green,led_blue} = {ledr,ledg,ledb}; //--------------------------ram_b_rd----------------------------//

wire rd = (cs0 | rdn);

wire wr = (cs0 | wrn); reg wr_clk1,wr_clk2;

always@(posedge clk_100m or negedge rst_n)

if(!rst_n)

begin

wr_clk1 <= 'd1;

wr_clk2 <= 'd1;

end

else

{wr_clk2,wr_clk1} <= {wr_clk1,wr}; wire clk_b = (!wr_clk2 | !rd);

assign db = !rd ? dataout_b : 'hzzzz; endmodule

源代码下载链接:

链接:http://pan.baidu.com/s/1qYqNlwg 密码:9il4

iCore4链接:

【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验的更多相关文章

- 【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf 读RAM命令格式:read:地址(0-255)\cr\lf 核心代码: int main(void) ...

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

- 【iCore3 双核心板_FPGA】实验十八:基于单口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1i58Ssvz iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板】例程十六:USB_HID实验——双向数据传输

实验指导书及代码包下载: http://pan.baidu.com/s/1bojcVoV iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore4 双核心板_FPGA】例程十七:基于FIFO的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int fsmc_read_data; ; ]; ]; char *p; /* ...

- 【iCore3 双核心板】例程十:RTC实时时钟实验——显示日期和时间

实验指导书及代码包下载: http://pan.baidu.com/s/1jHuZcnc iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板】例程十二:通用定时器实验——定时点亮LED

实验指导书及代码包下载: http://pan.baidu.com/s/1kTWAAJ9 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

随机推荐

- webpack的版本进化史

一.概述2015,webpack1支持CMD和AMD,同时拥有丰富的plugin和loader,webpack逐渐得到广泛应用. 2016.12,webpack2相对于webpack1最大的改进就是支 ...

- 模拟页面获取的php数据(四)

<?php $tqzf = [ "aData" => [//通勤方式 "trafficType" => [ 0 => [ "t ...

- 洛谷P1395 会议(CODEVS.3029.设置位置)(求树的重心)

To 洛谷.1395 会议 To CODEVS.3029 设置位置 题目描述 有一个村庄居住着n个村民,有n-1条路径使得这n个村民的家联通,每条路径的长度都为1.现在村长希望在某个村民家中召开一场会 ...

- swoole深入学习 4. process

swoole-1.7.2增加了一个进程管理模块,用来替代PHP的pcntl扩展.pcntl是php新增的一个多进程扩展,用来实现多进程,但是有很多不完善的地方,swoole 就完善了这些地方,而且使得 ...

- JVM加载class文件的原理机制(转)

JVM加载class文件的原理机制 1.Java中的所有类,必须被装载到jvm中才能运行,这个装载工作是由jvm中的类装载器完成的,类装载器所做的工作实质是把类文件从硬盘读取到内存中 2.java中的 ...

- exce中42093和日期之间的关系

在EXECEL中数字0 代表日期 1900-1-0 ,即这个日期为起始日期,算是第0天数字1 代表日期 1900-1-1 ,即第一天数字2 代表日期 1900-1-2 ,即第二天......数字415 ...

- Spring 3.1 M1: Unified Property Management(转)

In the first two posts of this series, I described the bean definition profiles feature, and how it ...

- ios 类别(category)

定义 类别(category)是Objective-C语言的新特性,为现有的类添加新方法的方式.局限性:1.无法添加新的实例变量.2.与类本身的方法名称冲突.当名称冲突时,类别具有更高的优先级.作用: ...

- 2016年Godaddy最新域名转出教程

2016年Godaddy最新域名转出教程 http://godaddy.idcspy.com/godaddy-newest-domain-zhuanchu HostEase注册的域名转入和转出 htt ...

- 修改Unity中Lua文件的默认打开程序

项目中引用了XLua,而Lua文件又是以txt文件结尾的,当修改系统的扩展脚本编辑器为vs后双击lua文件(xx.txt)默认也使用vs打开了,无提示的黑白文本编辑 昨办? -. 后来看到网上有写Un ...