【iCore1S 双核心板_FPGA】例程十六:基于SPI的ARM与FPGA通信实验

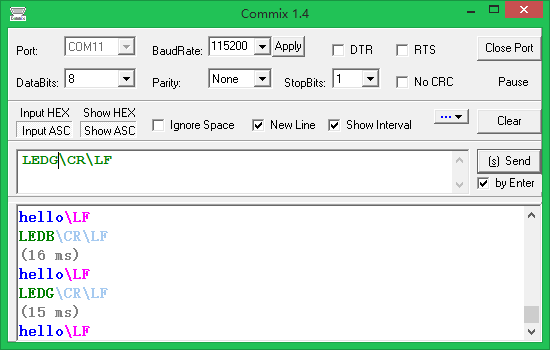

实验现象:

核心代码:

int main(void)

{

int i,n;

char buffer[];

char spi_buffer[]; HAL_Init();

system_clock.initialize(); led.initialize();

usart1.initialize();

spi.initialize(); usart1.printf("Hello! I am iCore1S!\r\n");

while()

{

if(usart1.receive_ok_flag)

{

usart1.receive_ok_flag = ;

for(i = ;i < ;i++)

{

buffer[i] = tolower(usart1.receive_buffer[i]);

}

n = strlen(buffer); if(memcmp(buffer,"ledr",strlen("ledr")) == )

{ LED_RED_ON;

LED_GREEN_OFF;

LED_BLUE_OFF;

}

if(memcmp(buffer,"ledg",strlen("ledg")) == )

{ LED_RED_OFF;

LED_GREEN_ON;

LED_BLUE_OFF;

}

if(memcmp(buffer,"ledb",strlen("ledb")) == )

{ LED_RED_OFF;

LED_GREEN_OFF;

LED_BLUE_ON;

}

buffer[]=;

n=strlen(buffer);

spi.write_nbyte(n,buffer);

for(i=;i<;i++)

{

spi_buffer[i] = spi.write_byte(0x00);

} usart1.printf("%s\n",spi_buffer);

}

}

}

module SPI(

input CLK_12M,

input spi_clk,

input spi_mosi,

input spi_cs,

output spi_miso, output FPGA_LEDR,

output FPGA_LEDG,

output FPGA_LEDB

); //-------------------------rst_n---------------------------//

/*复位信号*/

reg [:]rst_cnt = 'd0;

reg rst_n = 'd0; always @(posedge CLK_12M)

if(rst_cnt == 'd50)

begin

rst_n <= 'd1;

rst_cnt <= rst_cnt;

end

else rst_cnt <= rst_cnt + 'd1; //-------------------------parameter---------------------------//

parameter ledr = {'d108,8'd101,'d100,8'd114},

ledg = {'d108,8'd101,'d100,8'd103},

ledb = {'d108,8'd101,'d100,8'd98},

hello = {'d104,8'd101,'d108,8'd108,'d111}; //--------------------------spi_mosi---------------------------//

/*接收模块*/

reg [:]i;

reg [:]data_in;

reg [:]temp_data,data; always@(posedge spi_clk or negedge rst_n)

if(!rst_n)

begin

i <= 'd0;

temp_data <= 'd0;

data <= 'd0;

data_in <= 'd0;

end

else case(i) //从高位开始接收数据,每8个spi_clk时钟接收一个Byte

'd0:

begin

i <= i + 'd1;

data_in <= {data_in[:],spi_mosi};

temp_data <= {temp_data[:],data_in};

if(data_in == 'd13)

begin

data <= temp_data;

end

else

begin

data <= data;

end

end

'd1,4'd2,'d3,4'd4,'d5,4'd6:

begin

i <= i + 'd1;

data_in <= {data_in[:],spi_mosi};

end

'd7:begin

i <= 'd0;

data_in <= {data_in[:],spi_mosi};

end

default: i <= 'd0;

endcase //--------------------------data----------------------------//

/*对比接收数据*/

reg [:]led; always@(posedge CLK_12M or negedge rst_n)

if(!rst_n)

begin

led <= 'b111;

end

else if (data == ledr)

led <= 'b011; //红灯亮

else if (data == ledg)

led <= 'b101; //绿灯亮

else if (data == ledb)

led <= 'b110; //蓝灯亮 assign {FPGA_LEDR,FPGA_LEDG,FPGA_LEDB} = led; //--------------------------spi_miso----------------------------//

/*发送模块*/

reg [:]data_out;

reg [:]j;

reg MISO; always@(negedge spi_clk or negedge rst_n)

if(!rst_n)

begin

data_out <= hello;

j <= 'd0;

end

else case(j) //连续40个spi_clk_r时钟发送“hello”字符串

'd0:

begin

{MISO,data_out[:]} <= data_out;

j <= j + 'd1;

end

'd39:

begin

{MISO,data_out[:]} <= data_out;

data_out <= hello;

j <= 'd0;

end

default:

begin

{MISO,data_out[:]} <= data_out;

j <= j + 'd1;

end

endcase assign spi_miso = MISO; //--------------------------endmodule----------------------------//

endmodule

实验方法及指导书:

链接:http://pan.baidu.com/s/1jImpPRo 密码:c4s0

【iCore1S 双核心板_FPGA】例程十六:基于SPI的ARM与FPGA通信实验的更多相关文章

- 【iCore4 双核心板_FPGA】例程十三:基于SPI的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符HELLO. 3.通过串口精灵发送命令可以控制ARM·LE ...

- 【iCore3 双核心板】例程十六:USB_HID实验——双向数据传输

实验指导书及代码包下载: http://pan.baidu.com/s/1bojcVoV iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore1S 双核心板_FPGA】例程二:GPIO输入实验——识别按键输入

实验现象: iCore1s 双核心板上与FPGA相连的三色LED(PCB上标示为FPGA·LED),按键按下红灯点亮,松开按键红灯熄灭. 核心源代码: module KEY( input CLK_12 ...

- 【iCore1S 双核心板_FPGA】例程十五:基于I2C的ARM与FPGA通信实验

实验现象: 核心代码: int main(void) { int i,n; ]; ]; HAL_Init(); system_clock.initialize(); led.initialize(); ...

- 【iCore1S 双核心板_FPGA】例程六:状态机实验——状态机使用

核心代码: module FSM( input CLK_12M, input FPGA_KEY, output FPGA_LEDR, output FPGA_LEDG, output FPGA_LED ...

- 【iCore1S 双核心板_FPGA】例程十:乘法器实验——乘法器的使用

实验现象: 通过FPGA 的一个I/O 口连接LED:设定I/O 为输出模式.内部乘法器完成乘法计算后改变输出LED 的状态(红色LED 闪烁). 核心代码: module MULT( input C ...

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

- 【iCore1S 双核心板_FPGA】例程十四:FSMC总线通信实验——独立地址模式

实验原理: STM32F103上自带FMC控制器,本实验将通过FMC总线的地址独立模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

随机推荐

- Cube Stack

Cube Stack 有一点lazy思想,设三个数组cnt代表它以下的有多少个元素(直到栈底),top[x]代表x所在栈的栈顶元素,dad[x]代表x所在栈的栈底元素,先寻找父亲,然后递归更新累加cn ...

- 李宏毅机器学习笔记1:Regression、Error

李宏毅老师的机器学习课程和吴恩达老师的机器学习课程都是都是ML和DL非常好的入门资料,在YouTube.网易云课堂.B站都能观看到相应的课程视频,接下来这一系列的博客我都将记录老师上课的笔记以及自己对 ...

- java 三目运算符

三目运算符 可以内嵌使用. level=(input>90)?"Class A":(input>60)?"Class B":"Class ...

- idea颜色主题

作者:韩梦飞沙 Author:han_meng_fei_sha 邮箱:313134555@qq.com E-mail: 313134555 @qq.com IDEA 主题样式 === 这个垂直线的 颜 ...

- BZOJ.1022.[SHOI2008]小约翰的游戏John(博弈论 Anti-Nim)

题目链接 Anti-Nim游戏: 先手必胜当且仅当: 1.所有堆的石子数为1,且异或和为0 2.至少有一堆石子数>1,且异或和不为0 简要证明: 对于1:若异或和为1,则有奇数堆:异或和为0,则 ...

- 潭州课堂25班:Ph201805201 第十三课 文件 (课堂笔记)

对文件的操作, open('h:\\asa.txt') r 以只读方式打开 w 以写入方式打开,会覆盖已文件 X 如果已存在,会异常 a 如果文件存在,则在 ...

- SpringMVC页面传值

public ModelAndView query(){ ModelAndView modelAndView = new ModelAndView(); List list = new ArrayLi ...

- World final 2017 题解

链接:https://pan.baidu.com/s/1kVQc9d9 Problem A: #include <cstdio> #include <algorithm> #i ...

- AngularJS中介者模式实例

在任何应用程序中,中介者模式随处可见. → 有一个事件源,触发事件,传递参数→ 中介者记下这个事件,向外界广播,并带上参赛→ 有一个地方侦听中介者事件,一旦事件源触发事件,就从中介者手里获取事件相关参 ...

- 混沌的艺术--- YChaos通过数学公式生成混沌图像

艺术真得很难吗?也许如同编程一样容易.我写了一套软件,其功能是通过输入数学方程式,生成艺术图像.一提到数学有人可能会发怵,这里请不要担心,生成混沌的数学公式大都很是简单,基本上只用加.减.乘.除.余. ...