ARM FPGA Extended Memory Interface

Connect a ARM Microcontroller to a FPGA using its Extended Memory Interface (EMI)

http://elinux.org/Connect_a_ARM_Microcontroller_to_a_FPGA_using_its_Extended_Memory_Interface_(EMI)

http://www.makestuff.eu/wordpress/software/fpgalink/

http://www.techonlineindia.com/techonline/design_centers/170438/interface-fpgas-microcontrollers

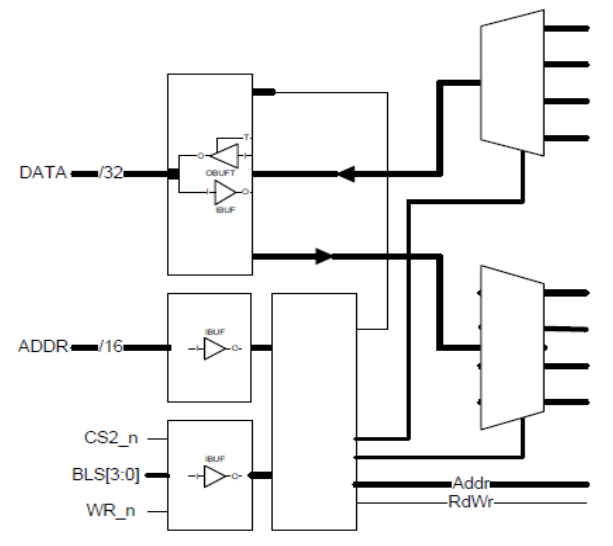

For a transfer of data to the FPGA, the direction of the bidirectional buffers in the PIO must be set to output. The software algorithm that transfers data to the FPGA is as follows:

PIO_DATA = ADDRESS; // Pass the address to write

PIO_CTROL = START | WR; // Send start of address cycle

PIO_CTROL = CLEAR; // Clear PIO ctrl, this ends the address cycle

PIO_DATA = DATA; // Set data to transfer

PIO_CTROL = START; // Data is ready in PIO

PIO_CTROL = CLEAR; // This ends the data cycle

Reading from the FPGA is similar. Again, the direction of the buffer on the PIO must first be set to output and then change directions to input to read the data from the FPGA, the following code is executed:

PIO_DATA = ADDRESS; // Set the address to read

PIO_CTROL = START | RD; // Send start of address cycle

PIO_CTROL = CLEAR; // Clear PIO ctrl, this ends the address cycle

PIO_DATA_DIR = INPUT; // Set PIO-Data direction as input to receive the data

DELAY(WAIT_FOR_FPGA); // wait for the FPGA to send the data

DATA_FROM_FPGA = PIO_DATA; // Read data from FPGA

ARM FPGA Extended Memory Interface的更多相关文章

- 【新产品发布】【iCore2 ARM / FPGA 双核心板】

iCore2是一款包含ARM / FPGA两大利器的双核心板.ARM方面,采用意法半导体高性能的32位Cortex-M3内核STM32F103VE微处理器,主频达72MHz,并包含丰富外设接口.FPG ...

- 【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf 读RAM命令格式:read:地址(0-255)\cr\lf 核心代码: int main(void) ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore4 双核心板_FPGA】例程十七:基于FIFO的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int fsmc_read_data; ; ]; ]; char *p; /* ...

- 【iCore3 双核心板_FPGA】实验十八:基于单口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1i58Ssvz iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板_FPGA】实验二十:基于FIFO的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1cmisnO iCore3 购买链接: https://item.taobao.com/item.htm?id=5242294 ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

随机推荐

- python基础--os模块和sys模块

os模块提供对操作系统进行调用的接口 # -*- coding:utf-8 -*-__author__ = 'shisanjun' import os print(os.getcwd())#获取当前工 ...

- 安装pywin32模块

1.先下载pywin32对于的版本 下载地址:python for windows extensions 2.选择自己对应的版本,我的是python3.5版本 注意注意注意:此处一定要看清楚自己的py ...

- [USACO16OPEN]262144

传送门啦 其实大家可以先看一下这个题 [USACO16OPEN]248 分析: 数据范围很奇特:n特别,a[i]特别——如果O(N^3)能接受就直接区间DP水过了,但是不行,于是考虑设计一个状态囊括a ...

- WiFi无线连接真机进行Appium自动化测试方法

有时需要测试APP 产品的耗电问题,但用自动化又面临了一个USB接电脑供电的问题,从而导致计算出来的功耗与手动跑,存在有很大的误差,因此可使用wifi无线连接到手机进行自动化测试,解决功耗问题. 前提 ...

- HDU 4632 Palindrome subsequence(区间DP求回文子序列数)

题目链接:http://acm.hdu.edu.cn/showproblem.php?pid=4632 题目大意:给你若干个字符串,回答每个字符串有多少个回文子序列(可以不连续的子串).解题思路: 设 ...

- Effective STL 学习笔记 Item 16:vector, string & C API

有时需要支持 C 的接口,但这并不复杂. 对于 vector 来讲, \(v[0]\) 的地址 \(\&v[0]\) 即可作为数组指针传递给 C API: 1: // Legacy C API ...

- CVE-2013-3893

前方高能!!!这篇博文比较长,因为我把完整的调试过程都记录下来了,感兴趣的童鞋可以看下.没有耐心的童鞋可以直接跳到最后看总结:) Microsoft Internet Explorer 远程代码执行漏 ...

- 1391: [Ceoi2008]order

有N个工作,M种机器,每种机器你可以租或者买过来. 每个工作包括若干道工序,每道工序需要某种机器来完成,你可以通过购买或租用机器来完成. 现在给出这些参数,求最大利润 Input 第一行给出 N,M( ...

- jquery选择里存在特殊字符,需要加双转义字符

//元素为:<input type="checkbox" value="abc/index" /> //处理选择器转义问题 //去除值 $val = ...

- linux删除特殊字符命名的文件

今天在服务器上不小心创建了一个!命名的文件还有一个\命名的文件,本来想用转义字符进行删除,又担心误删了项目文件....最后找到最好的解决办法 如下: ls -i 查看文件inum值 执行删除inum ...