intel FPGA CLKn pin 是否能直接进PLL?

原创 by DeeZeng

FPGA的时钟需要从专用的时钟管脚输入,那CLKn 作为Single-End时钟pin时是否能直接进 PLL呢?

通过查看对应FPGA型号的手册,得出以下结论

1. Cyclone V, Stratix V 的 CLKn 不能直接进PLL,需要走GCLK,RCLK之后才行

2. MAX10 ,Arria 10 的 PLL ,CLKn 可以直接进PLL。 (Arria10 的 fPLL CLKn不能直接走,但 XCVR bank 的一般是 差分时钟输入)

如下以部分FPGA 系列举例

1. Cyclone V,Stratix V FPGA

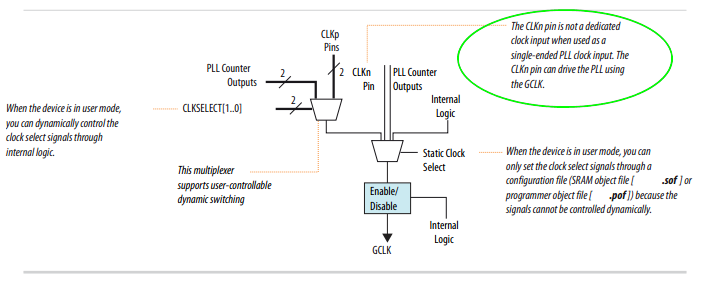

如下 Cyclone V, Stratix V手册:

The CLKn pin is not a dedicated clock input when used as a single-ended PLL clock input.

The CLKn pin can drive the PLL using the GCLK.

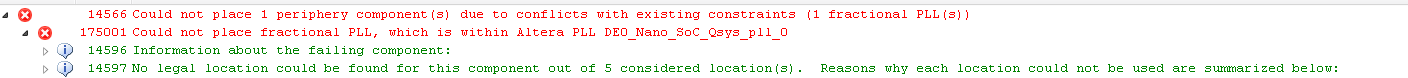

那会出现如下报错:

(如果实际硬件已经必须用CLKn进 PLL了,可以先用 CLK_CTRL ip 让 CLKn 走GCLK)

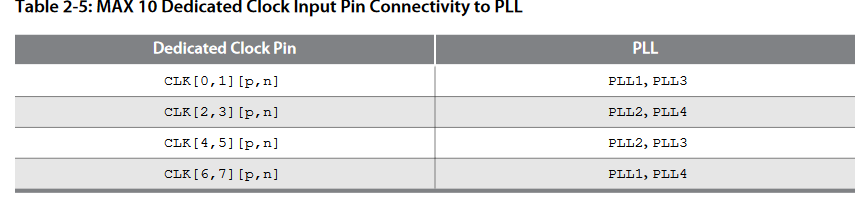

2. MAX10 ,Arria10 FPGA

MAX10 的 CLKp,CLKn 都可以drive PLL

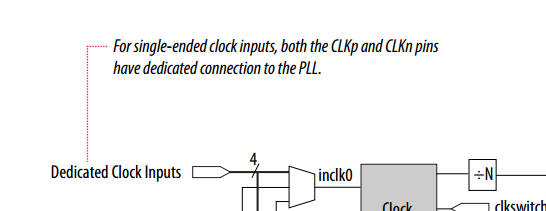

Arria 10 的IOPLL 的 CLKn可以直接进 IOPLL (both the CLKp and CLKn pins hav dedicated ...)

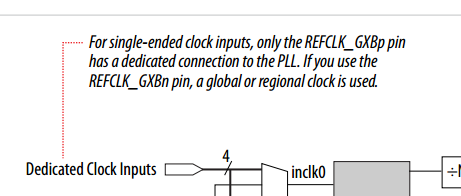

Arria 10 的fPLL 的 REFCLK_GXBn 不能直接进 fPLL (不过 XCVR bank 一般也都是 差分时钟输入,影响不大)

所以我们在设计FPGA 或 做工程的时候需要注意下当前 FPGA系列的 CLK属性。能用专用pin 的就用专用pin

专用pin GCLK 等的好处, low slew rate , high fan out 等等。 timing 更容易满足

intel FPGA CLKn pin 是否能直接进PLL?的更多相关文章

- 关于INTEL FPGA设计工具DSP Builder

一段时间以来,MathWorks一直主张使用Matlab和Simulink开发工具进行基于模型的设计,因为好的设计技术使您能够在更短的时间内开发更高质量的复杂软件.基于模块的设计采用了数学和可视化的方 ...

- 基于INTEL FPGA硬浮点DSP实现卷积运算

概述 卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波.而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络.本参考设计主要介绍如何基于INTEL 硬浮点的DS ...

- Intel FPGA Clock Region概念以及用法

目录 Intel FPGA 的Clock Region概念 Intel 不同系列FPGA 的Clock Region 1. Clock Region Assignments in Intel Stra ...

- OpenCL设计优化(基于Intel FPGA SDK for OpenCL)

1.首先了解Intel FPGA SDK for OpenCL实现OpenCL的设计组件,包括: kernels, global memory interconnect, local memory, ...

- Intel FPGA 专用时钟引脚是否可以用作普通输入,输出或双向IO使用?

原创 by DeeZeng FPGA 的 CLK pin 是否可以用作普通输入 ,输出或双向IO 使用? 这些专用Clock input pin 是否可以当作 inout用,需要看FPGA是否支 ...

- intel FPGA使用

https://www.altera.com/documentation/swn1503506366945.html https://files.cnblogs.com/files/shaohef/o ...

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 在使用FPGA来控制DDR3/DDR2 IP 的时候两个错误的解决办法

对于熟悉Intel FPGA的老(gong)司(cheng)机(shi)来说,外部存储器的控制早已是轻车熟路,但是对于新手,DDR3/DDR2 的IP使用也许并没有那么简单,不过没关系,骏龙的培训网站 ...

- 在MAX10上使用DDR3 IP的一个关于DQS/DQSn pin的错误解决办法

MAX10 是Intel FPGA的CPLD中的一个特殊的芯片,因为它内部有CPLD的Flash结构,也有FPGA的Ram结构.具体的可以参考MAX10 Handbook文档. Max10 在外部存储 ...

随机推荐

- WPF值转换器的使用

<Window x:Class="CollectionBinding.MainWindow" xmlns="http://schemas.micros ...

- 【Python】Camera拍照休眠唤醒测试

#!/usr/bin/python # -*- coding: UTF-8 -*- import os import sys import time rebootCount = int(input(& ...

- 《芒果TV》UWP版利用Windows10通用平台特性,率先支持Xbox One平台

在Windows开发者中心开放提交Xbox平台应用之后,<芒果TV>UWP版迅速更新v3.1.2版,通过升级兼容目标,利用Windows10通用平台特性,率先覆盖Xbox平台用户. 芒果T ...

- Win10商店芒果TV UWP版更新,新增后台视频下载

湖南卫视旗下唯一官方视频平台<芒果TV>近日向Win10商店提交了芒果TV UWP V3.0.0版,这次为广大Win10平台用户带来了期待已久的重大功能和更新,可谓是良心厂商,值得鼓励和支 ...

- uwp开发————换背景图片

原文:uwp开发----换背景图片 用后台代码来实现对容器背景的切换,用本地图片作为背景. 把需要的图片素材放到Assets文件夹下 前台xaml代码如下: <Grid x:Name=" ...

- ef 查询总结

1.Linq 查询两张表:a表和b表,要得到的数据是a表数据b表没有 例如:a表有5条数据1,2,3,4,5:b表有2条数据1,3:那么就用dataGridView1输出2,4,5:link语句要怎么 ...

- 利用BLCR加速android的启动(zygote加入checkpoint支持)

目前基于android4.2.2基线代码的blcr扩展,编译和启动是没有问题了,但是一重启就挂了. 弄这个有段时间了,很纠结,没有个可靠的结果,但是研究到现在,又舍不得放弃. 我想除了shuaiwen ...

- Using 3D engines with Qt(可以整合到Qt里,不影响)

A number of popular 3D engines can be integrated with Qt: Contents [hide] 1 Ogre 2 Irrlicht 3 OpenS ...

- Qt项目里的源代码默认都是Unicode,原因大概是因为qmake.conf里的定义

MAKEFILE_GENERATOR = MINGWQMAKE_PLATFORM = win32 mingwCONFIG += debug_and_release debug_and_release_ ...

- jquery事件和动画操作集锦

一,事件 1,加载事件 1 2 3 4 5 6 $(document).ready(function(){ //todo }); //dom准备就绪后执行ready里面的函数,此时dom对应的相关 ...