理解FPGA内部的同步信号、异步信号和亚稳态

FPGA(Field-Programmable Gate Array),即现场可编程门阵列。主要是利用内部的可编程逻辑实现设计者想要的功能。FPGA属于数字逻辑芯片,其中也有可能会集成一部分模拟电路的功能,大多数模拟电路都是当做asic进行工作的,可编程的部分大多数都是数字逻辑部分。

数字逻辑电路是由组合逻辑和时序逻辑器件构成,在时序逻辑器件中,常用就是时钟触发的寄存器。

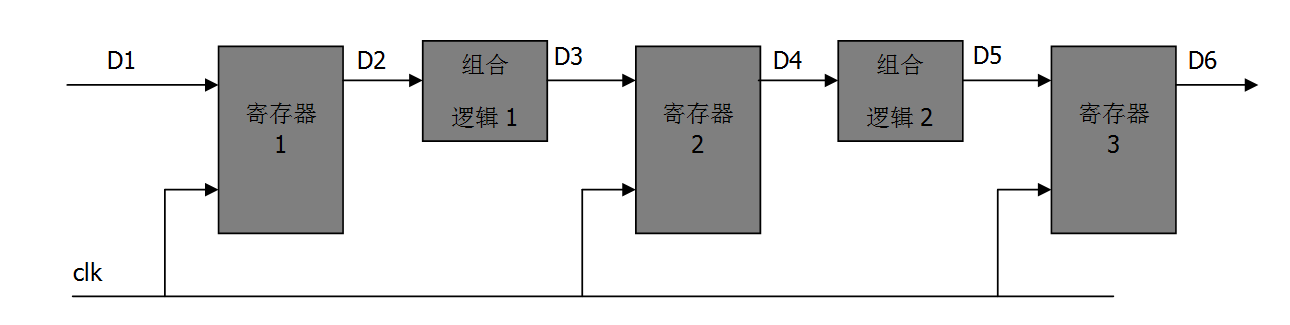

如果在设计中,所有的寄存器的时钟端都是连接的同一个时钟,那么称之为同步电路设计。所为同步也就是所有的寄存器的输出端都是由同一个时钟端驱动出来的,所有的寄存器在同一个步调上进行更新。

同步电路中的信号,我们称之为同步信号。

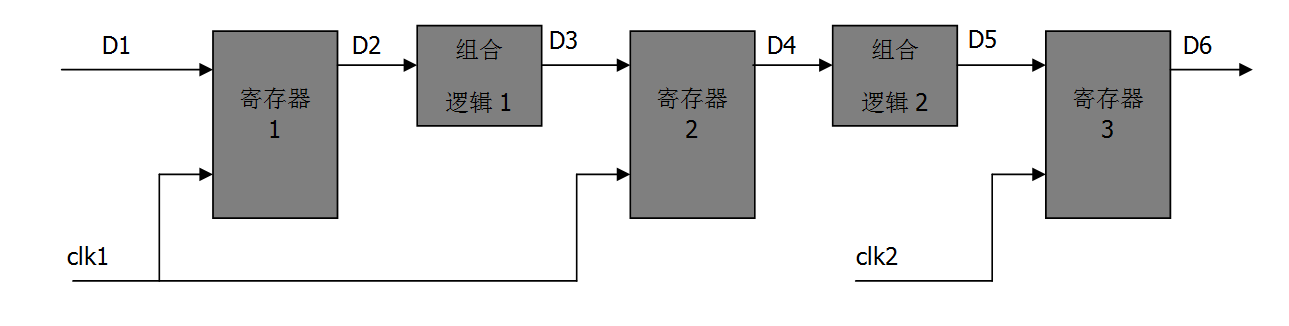

如果在设计中,寄存器的时钟端连接在不同的时钟上,那么称之为异步电路设计。

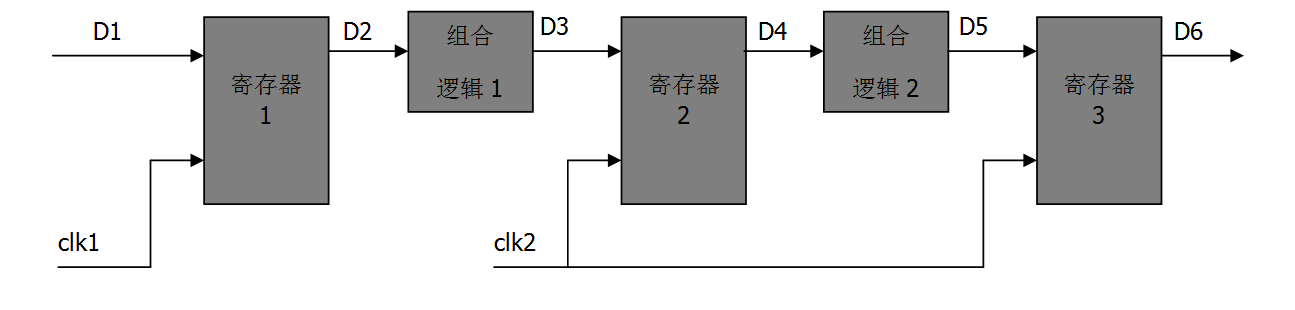

在异步电路中,被clk1驱动的寄存器和组合逻辑电路构成时钟域clk1的电路,被clk2驱动的寄存器和组合逻辑电路构成时钟域clk2的电路。信号从clk1的时钟域到clk2的时钟域,被称为跨时钟域。而对于信号D5来说,我们认为它是clk1时钟域的信号,那么对于clk2时钟域来说,就是异步信号,因为它不与clk2的驱动沿对齐。

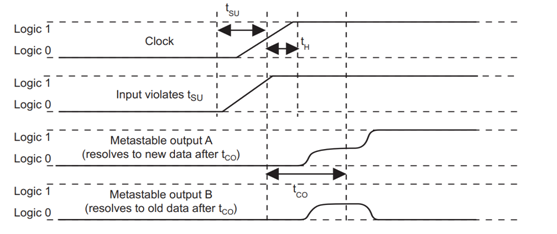

寄存器有一种特性,在clk的有效边沿时,采样数据D,输出到Q,此过程如果想要稳定进行,那么要求,数据D在clk有效边沿之前一段时间保持稳定(建立时间),在clk有效边沿之后一段时间保持稳定(保持时间),如果任何一个不满足,就会导致此过程失败,结果就是clk的有效边沿过去后,Q的值可能就不会出现预想值。那么是什么呢?先不着急,后面慢慢谈。

在真实的电路中,各部分元器件都是由延迟的。对于同步电路来说,Q的更新都是在clk上上升沿之后的一段时间(Tco:输出延迟),输出的数据经过组合逻辑或者线路也会有延迟(delay:线路延迟),到达下一个寄存器。此时,信号早就偏离了clk的上升沿。所以对于下级寄存器来说,这个信号也是“异步信号”。所以说真实电路中,全部的信号都是“异步信号”。

那么为什么在同步电路中,我们都称为同步信号呢?

因为在电路中,所有的延迟都是已知的(TCO、delay等等),我们可以通过扩大clk的周期,确保clk的周期大于TCO等等之类延迟之和,那么就可以保证下级寄存器采样到数据。所以这种电路中的信号,我们依然把他称之为同步信号。

在跨时钟域时,由于两个时钟之间没有任何关系,无论怎么调整周期,都不一定能满足下级寄存器采样到数据,肯定不能调成一致周期,那就变成了同步设计。例:用寄存器采样外部按键的输入,那么此时外部按键的信号对于寄存器来说就是异步信号,因为外部信号是随时都有可能有效,所以无论怎么调整,都不一定能够保证信号满足寄存器的建立保持时间。

那么既然在很多情况下,无论如何也避免不了异步信号带的坏处,那么能不能全部采用同步设计?显然是不太现实,不同接口或者存储器等都有自己频率,全部采用同步电路设计的方式将失去很多功能。例如:千兆以太网的GMII接口,采用125M接口,1080P的HDMI接口采用148.5MHz的接口。

既然无法避免,那就勇敢面对。

当信号不满足建立和保持时间时,寄存器会输出什么值呢?

在上图中,输入信号在clock的上升沿左右有了一个从高到低的变化,即不满足建立和保持时间。那么寄存器的输出端就会输出一个既不是高电平也是低电平的一个电平。

在数字电路中,高电平和低电平是两个稳定的电平值,能够一直维持不变化。如果不满足建立或者保持时间的话,输出的电平值不高也不低,但是此电平不稳定,称为亚稳态(类似于健康和亚健康)。亚稳定是不稳定的,终究要向高或者低电平进行变化。

那么有人说,亚稳态终究会走向稳态,那么岂不是没有影响了。答案是错误的。可以想象,亚稳态走向稳态是必然趋势,可是需要一定的时间,如果在这一段时间内,被其他电路所引用,那么就会造成亚稳态的传播,进而导致整个电路的瘫痪(因为整个电路都会变成非高非低的信号在运行)。

那么应该如何处理呢?

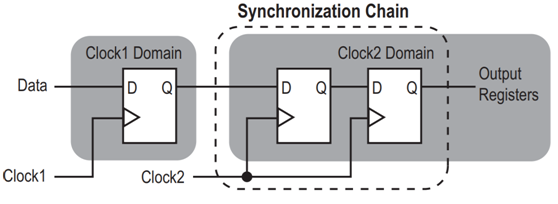

对于单bit信号,我们一般采用同步寄存器链来进行处理。

对于同步寄存器链的要求有三点:

第一:在同步寄存器链中,所有的寄存器都必须用同一个或者相关(例如:一个时钟是另外一个时钟的相位延迟180度)时钟驱动。

第二:第一个寄存器的输入为外部的异步信号。

第三:在同步寄存器链中,所有的输出只能给下一级使用。只有最后一级寄存器可以给其他的电路使用。

对于第一点和第二点,不在解释。下面解释一下第三点。

D3信号为clk2时钟域的异步信号,那么D4信号就有可能出现亚稳态。假设D4信号出现亚稳态后,恢复至稳态的时间为T1,组合逻辑2的延迟为T2,那么D5信号得到稳态的时间为T1+T2。如果没有组合逻辑2时,D5信号得到稳态的时间为T1。如果clk2的周期大于T1+T2,那么有无组合逻辑2,将不受影响;如果clk2的周期大于T1且小于T1+T2,那么有组合逻辑2,就会造成亚稳态的传播。如果clk2的周期小于T1,也会亚稳态的传播。

综上所述,组合逻辑2,还是不要有的好,能够大大增加D5得到稳态的几率。

在上述叙述中,我们只是提高了得到稳态的几率,但是还是有亚稳态传播的几率。

在实际电路中,一般同步寄存器链会有两级甚至多级。那么多级的同步寄存器链会有什么作用呢?

在上述叙述中得知,亚稳态是一种不稳定的状态,会向稳定状态过渡。如果第一级寄存器输出亚稳态,恢复时间为T1,如果clk的周期小于T1,那么亚稳态将会在第二级寄存器输出,由于第一级亚稳态已经经过clk一个周期的恢复,所以在第二级寄存器输出时,亚稳态恢复至稳态的时间T2将会缩短。T2< T1。

再多级的寄存器,也无法避免亚稳态,只是级数越多,最后一级输出亚稳态的几率将会越低。

在实际电路中,一般采用两级或者三级即可。

设计者:郝旭帅 QQ:746833924 QQ交流群: 173560979

理解FPGA内部的同步信号、异步信号和亚稳态的更多相关文章

- 让你高效的理解JavaScript中的同步、异步和事件循环

"同步请求","异步请求"相信这两词在程序猿的世界中频频出现,到底是词性的妖娆,还是撸代码的基础要求,下面直接分享本人学习的好东西,保证让你深入浅出,爽得不要不 ...

- 如何理解javascript中的同步和异步

javascript语言是一门“单线程”的语言,不像java语言,类继承Thread再来个thread.start就可以开辟一个线程,所以,javascript就像一条流水线,仅仅是一条流水线而已,要 ...

- 关于Web开发里并发、同步、异步以及事件驱动编程的相关技术

一.开篇语 我的上篇文章<关于如何提供Web服务端并发效率的异步编程技术>又成为了博客园里“编辑推荐”的文章,这是对我写博客很大的鼓励,也许是被推荐的原因很多童鞋在这篇文章里发表了评论,有 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- 【C/C++】对于可重入、线程安全、异步信号安全几个概念的理解

由于前段时间,程序偶尔异常挂起不工作,检查后发现时死锁了,原因就是:在信号处理函数里面调用了fprintf. printf等io函数是需要对输出缓冲区加锁,这类函数对本身是线程安全的,但是对信号处理函 ...

- FPGA内部信号避免高阻态

RT,否则警告Warning: Tri-state node(s) do not directly drive top-level pin(s),会利用或门代替中间的扇出fan-out. 原因:在进行 ...

- linux 异步信号的同步处理方式

关于代码的可重入性,设计开发人员一般只考虑到线程安全,异步信号处理函数的安全却往往被忽略.本文首先介绍如何编写安全的异步信号处理函数:然后举例说明在多线程应用中如何构建模型让异步信号在指定的线程中以同 ...

- 7.FPGA中的同步复位与异步复位

1.异步复位 always @ ( posedge sclk or negedge s_rst_n ) if ( !s_rst_n ) d_out <= 1'b0; else d_out < ...

- PHP-Socket-阻塞与非阻塞,同步与异步概念的理解

1. 概念理解 在进行网络编程时,我们常常见到同步(Sync)/异步(Async),阻塞(Block)/非阻塞(Unblock)四种调用方式:同步: 所谓同步,就是在发出一个功能调用时,在没 ...

- linux可重入、异步信号安全和线程安全

一 可重入函数 当一个被捕获的信号被一个进程处理时,进程执行的普通的指令序列会被一个信号处理器暂时地中断.它首先执行该信号处理程序中的指令.如果从信号处理程序返回(例如没有调用exit或longjmp ...

随机推荐

- 美团一面:说一说Java中的四种引用类型?

引言 在JDK1.2之前Java并没有提供软引用.弱引用和虚引用这些高级的引用类型.而是提供了一种基本的引用类型,称为Reference.并且当时Java中的对象只有两种状态:被引用和未被引用.当一个 ...

- Android Graphics 多屏同显/异显

" 亏功一篑,未成丘山.凿井九阶,不次水泽.行百里者半九十,小狐汔济濡其尾.故曰时乎,时不再来.终终始始,是谓君子." 01 前言 随着Android智能驾舱系统的普及各种信息交互 ...

- 阿里二面:Java中锁的分类有哪些?你能说全吗?

引言 在多线程并发编程场景中,锁作为一种至关重要的同步工具,承担着协调多个线程对共享资源访问秩序的任务.其核心作用在于确保在特定时间段内,仅有一个线程能够对资源进行访问或修改操作,从而有效地保护数据的 ...

- 冰河开始对Dubbo下手了!

写在前面 对冰河有一定了解的读者都知道,冰河经历了一个高并发电商系统用户从零到上亿的整个研发过程,后期也由此衍生出电商系统(商城+秒杀)和基于海量数据的实时精准商品推荐平台.部分核心知识已总结到我出版 ...

- CLion和WSL配置MPI运行及调试环境

本文将介绍 Windows 下,使用 CLion 和 WSL 配置 MPI 运行及调试环境的方法. 0. 前提 阅读本文前,请确保: Windows 下已启用 WSL2,并安装了任一 Linux 发行 ...

- KingbaseES V8R6 集群运维系列 -- trusted_server

案例说明: 在KingbaseES V8R3及V8R6早期的版本,对于读写分离的集群如果网关地址无法连通,将会导致整个集群关闭,数据库服务无法访问.在后期版本的改进中,降低了对网关的依赖性,当网关地址 ...

- 陈海波:OpenHarmony技术领先,产学研深度协同,生态蓬勃发展

11月4日,以"技术筑生态,智联赢未来"为主题的第二届OpenHarmony技术大会在北京隆重举办.本次大会由OpenAtom OpenHarmony(简称"Open ...

- OpenAtom OpenHarmony分论坛,今天14:00见!附大事记精彩发布

2022开放原子全球开源峰会 OpenAtom OpenHarmony分论坛 万物互联,使能千行百业 整装待发!精彩今日揭晓与您相约7月27日 14:00

- 深入理解 Java 方法重载与递归应用

Java 方法重载 方法重载 允许在同一个类中定义多个具有相同名称的方法,但 参数列表 必须不同. 语法: returnType methodName(parameter1, parameter2, ...

- Pandas统计计算

基本的统计方法 Method Description count Number of non-NA values describe Compute set of summary statistics ...