信号监测---verilog

信号监测---verilog

此模块用于监测某一信号源是否持续稳定的传送。

监测思路:监测信号源高电平或者低电平的宽度是否始终保持一致(一定范围内允许有误差)

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/10/12 14:43:57

// Design Name:

// Module Name: signal_detection

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module signal_detection #(

parameter WIDTH = ,

parameter MAXIMUM_ERROR = ,

parameter CNT_CLK_FREQUENCY = ,

parameter DELAY_SIGNAL_OUT = ,

parameter TOTAL_TIME_HIGH = ,

parameter TOTAL_TIME_LOW =

)

(

input wire clk ,

input wire clk_out_syn ,

input wire rst ,

input wire signal_src ,

output wire lock

); //---------------------------------------------------------------------- // Signal source synchronization reg signal_src_delay_1 = ;

reg signal_src_delay_2 = ; always @(posedge clk or posedge rst)

begin

if(rst)

begin

signal_src_delay_1 <= 'b0 ;

signal_src_delay_2 <= 'b0 ;

end

else

begin

signal_src_delay_1 <= signal_src ;

signal_src_delay_2 <= signal_src_delay_1 ;

end

end //---------------------------------------------------------------------- //Rising edge detection assign rising_edge = signal_src_delay_1 && (!signal_src_delay_2) ;

assign falling_edge = (!signal_src_delay_1) && signal_src_delay_2 ; //---------------------------------------------------------------------- //count enable 信号上升沿开始计数,下降沿停止计数,此模块采用的是计算高电平的宽度 reg cnt_en = ; always @(posedge clk or posedge rst)

begin

if(rst)

cnt_en <= 'b0 ;

else if(rising_edge)

cnt_en <= 'b1 ;

else if(falling_edge)

cnt_en <= 'b0 ;

end //---------------------------------------------------------------------- //count clock period reg [:] cnt = ; always @(posedge clk or posedge rst)

begin

if(rst)

cnt <= 'd0 ;

else if(cnt_en)

cnt <= cnt + 'b1 ;

else

cnt <= 'd0 ;

end //---------------------------------------------------------------------- //total 存储两个相邻高电平的宽度 reg [:] total_number = ;

reg [:] total_number_delay = ;

reg [:] total_number_delay_1 = ;

always @(posedge clk or posedge rst)

begin

if(rst)

begin

total_number <= 'd0 ;

total_number_delay <= 'd0 ;

total_number_delay_1 <= 'd0 ;

end

else if(falling_edge)

begin

total_number <= cnt ;

total_number_delay <= total_number ;

total_number_delay_1 <= total_number_delay ;

end

else if(get_total_time_high || get_total_time_low)

begin

total_number <= 'd0 ;

total_number_delay <= 'd0 ;

total_number_delay_1 <= 'd0 ; end

end

//此处或得了相邻三个高电平的宽度值

//---------------------------------------------------------------------- localparam UNLOCK = 'b0;

localparam LOCK = 'b1; //---------------------------------------------------------------------- wire lock_state_1 ;

wire lock_state_2 ;

//考虑高电平宽度误差量

assign lock_state_1 = (total_number >= total_number_delay_1) && ((total_number - total_number_delay_1) <= MAXIMUM_ERROR) && (total_number > 'd100) ;

assign lock_state_2 = (total_number < total_number_delay_1) && ((total_number_delay_1 - total_number) <= MAXIMUM_ERROR) && (total_number > 'd100) ;

//用total_number 与 total_number_delay_1 两个值来参与运算,是考虑到了隔行视频,相邻两个高电平的宽度是不一样的,因为一帧有两场,即一帧中有两个V信号的有效区间

//---------------------------------------------------------------------- // 1us reg get_time_1us ;

reg [WIDTH-:] m ;

always @ ( posedge clk or posedge rst )

begin

if( rst )

begin

get_time_1us <= 'b0;

m <= ;

end

else if( m == CNT_CLK_FREQUENCY - )

begin

get_time_1us <= 'b1;

m <= ;

end

else

begin

get_time_1us <= 'b0;

m <= m + 'b1;

end

end //---------------------------------------------------------------------- reg get_total_time_high ;

reg get_total_time_low ;

reg [WIDTH-:] i ;

reg [WIDTH-:] k ; always @ (posedge clk or posedge rst)

begin

if(rst)

begin

get_total_time_high <= 'b0 ;

get_total_time_low <= 'b0 ;

i <= ;

k <= ;

end else

begin

get_total_time_high <= 'b0 ;

get_total_time_low <= 'b0 ; if(signal_src_delay_2 == 'b0)

begin

if( i == TOTAL_TIME_LOW - )

begin

get_total_time_low <= 'b1 ;

i <= ;

end else if(get_time_1us)

i <= i + 'b1 ;

end else

i <= ; if(signal_src_delay_2 == 'b1)

begin

if( k == TOTAL_TIME_HIGH - )

begin

get_total_time_high <= 'b1 ;

k <= ;

end else if(get_time_1us)

k <= k + 'b1 ;

end else

k <= ;

end

end //---------------------------------------------------------------------- reg current_state ;

reg next_state ; always @ ( posedge clk or posedge rst )

begin

if( rst )

current_state <= UNLOCK;

else

current_state <= next_state;

end //---------------------------------------------------------------------- always @ ( * )

begin

case( current_state )

UNLOCK:

if( lock_state_1 || lock_state_2 )

next_state = LOCK;

else

next_state = UNLOCK;

LOCK:

if( get_total_time_high || get_total_time_low )

next_state = UNLOCK;

else

next_state = LOCK;

endcase

end //---------------------------------------------------------------------- //output reg reg lock_r; always @ (posedge clk or posedge rst)

begin

if(rst)

lock_r <= 'b0 ; else

begin

case(current_state)

UNLOCK: lock_r <= 'b0;

LOCK : lock_r <= 'b1;

endcase

end

end reg dly_reg[:DELAY_SIGNAL_OUT-]; genvar var_i;

generate

for (var_i=;var_i<=DELAY_SIGNAL_OUT-;var_i=var_i+)

begin:delay_generate_block

if (var_i==)

begin

always @ (posedge clk_out_syn or posedge rst)

if (rst)

dly_reg[var_i] <= ;

else

dly_reg[var_i] <= lock_r;

end

else

begin

always @ (posedge clk_out_syn or posedge rst)

if (rst)

dly_reg[var_i] <= ;

else

dly_reg[var_i] <= dly_reg[var_i-];

end

end

endgenerate assign lock = dly_reg[DELAY_SIGNAL_OUT-]; endmodule

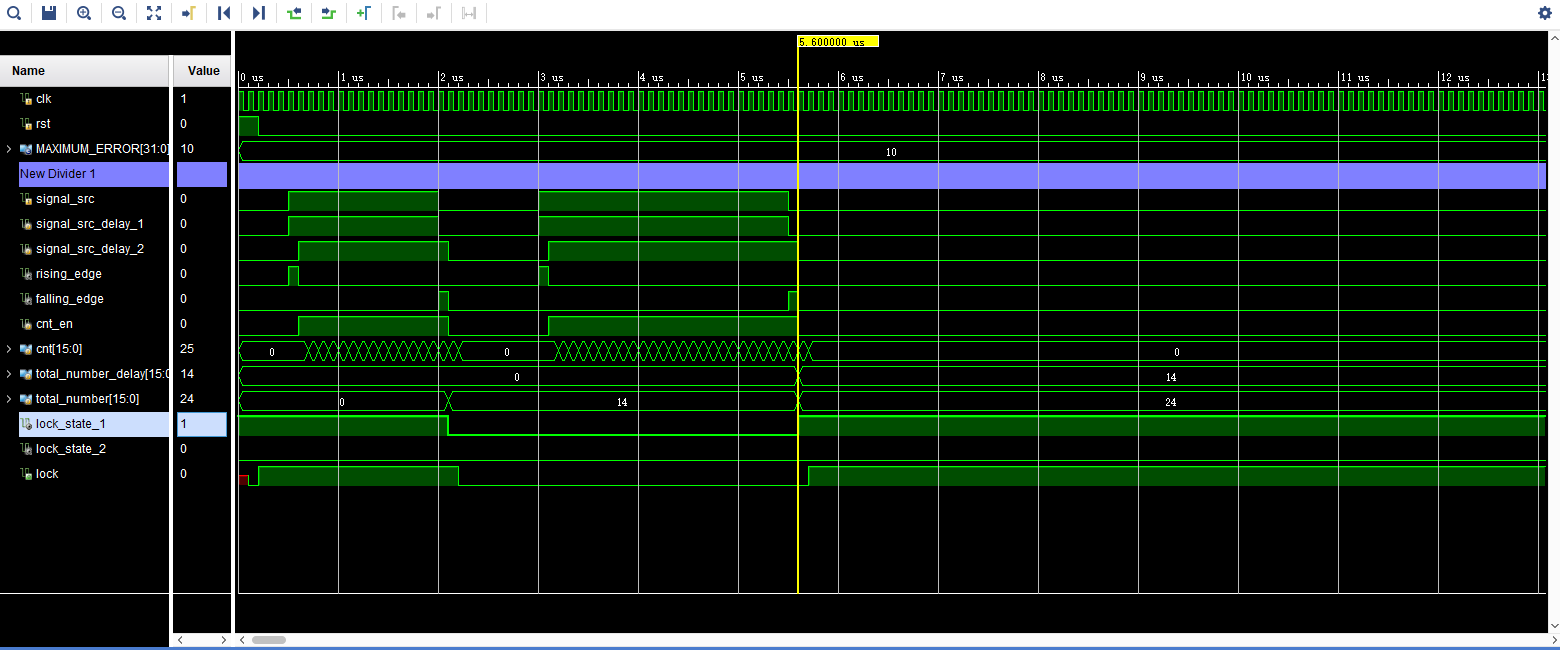

仿真结果:

信号监测---verilog的更多相关文章

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- 时钟分频方法---verilog代码

时钟分频方法---verilog代码 本文以SDI播出部分的工程为例,来说明一种时钟分频的写法.SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据 ...

- Verilog学习笔记基本语法篇(一)·········数据类型

Verilog中共有19种数据类型. 基本的四种类型: reg型.wire型.integer型.parameter型. 其他类型:large型.medium型.small型.scalared型.tim ...

- modelsim脚本文件的编写

第一章 ModelSim介 绍 本指南是为 ModelSim5.5f版本编写的,该版本运行于UNIX和Microsoft Windows 95/98/Me/NT/2000的操作系统环境中.本指南覆盖了 ...

- IZT复杂电磁环境记录回放和模拟系统

结合实验室复杂电磁环境特性与模拟研究需求,实现对复杂多变的电磁环境录制.分析.重构和模拟,记录回放系统应具备如下几项能力: 1.电磁环境信号记录能力:能够实现对9KHz-18GHz频带范围内射频信号的 ...

- passat / maintenance / baoyang

s s 南京迎客隆汽车租赁有限公司 / 地址:常府街54号 / 电话:025-84546836 84507610 二手车养不起.修不起?果真如此吗?http://www.che168.com/list ...

- APM飞控系统详细介绍

APM飞控系统详细介绍2013-04-05 12:28:24 来源: 评论:2 点击:10303 APM飞控系统是国外的一个开源飞控系统,能够支持固定翼,直升机,3轴,4轴,6轴飞行器.在此我 ...

- [Idea Fragments]2013.08.08

# 1 今晚看到好几篇文章把golang,Node.js还有Nginx-lua拿来说事,Node.js现在自然比较熟悉,golang则有过一些了解,而Nginx-lua则少有听到. 有好事者对Node ...

- 基于TI 多核DSP 的大数据智能计算处理解决方案

北京太速科技有限公司 大数据智能计算,是未来的一个发展趋势,大数据计算系统主要完成数据的存储和管理:数据的检索与智能计算. 特别是在智能城市领域,由于人口聚集给城市带来了交通.医疗.建筑等各方面的压力 ...

随机推荐

- KendoUi 学习笔记一

本系列主要是记录KendoUI的学习过程. KendoUi的特点有以下特点: 1. 70+UI控件 控件有DataGrids,DropDowns,Menus和Buttons,还有一些商业的控件,比如C ...

- 2018-2019-2 《网络对抗技术》Exp5 MSF基础应用 20165326

Exp5 MSF基础应用 实践内容 主动攻击实践 ms17_010_enternalblue 靶机:win7 x64成功 针对浏览器的攻击 ms14_064_ole_code_execution 靶机 ...

- IP通信基础原理课堂笔记----HCL(1)

PC端配置:打开接口,配置ip地址 交换机配置:①创建VLAN system-view vlan 10 vlan 20 ②配置PC端接口 interface gi 1/0/1 port link-ty ...

- ViewBag赋值Html格式值

今天再给自己总结一下,关于ViewBag赋值Html格式值,但是在web页显示不正常; 例如,ViewBag.Content = "<p>你好,我现在测试一个东西.</p& ...

- 北大poj-1021

2D-Nim Time Limit: 1000MS Memory Limit: 10000K Total Submissions: 4066 Accepted: 1851 Descriptio ...

- python2入门(3)

六.python列表(List) python最常见的序列类型python列表List使用[]表示,元素之间以逗号分隔,元素类型不需要相同 内置操作: list = [1,2,3,'four'] li ...

- Inside a low budget consumer hardware espionage implant

The following analysis was performed on a S8 data line locator which replied to the hidden SMS comma ...

- python(pygame)滑稽大战(类似飞机大战) 教程

成品已录制视频投稿B站(本文目前实现了基础的游戏功能),点击观看项目稽忽悠不(github)地址:https://github.com/BigShuang/From-simple-to-Huaji 本 ...

- Python 死锁现象

import time from threading import Thread,Lock,RLock def f1(locA,locB): locA.acquire() print('f1>& ...

- Java前后端依赖

有时候我们的一个类需要依赖另外一个类,这种就是依赖关系,创建对象的工作一般由spring容器来完成然后注入给调用者,这种就是依赖注入. 代码可参考1227210565朋友空间 DispatcherSe ...