HDLbits——Shift18

// Build a 64-bit arithmetic shift register,

// with synchronous load. The shifter can shift both left and right,

// and by 1 or 8 bit positions, selected by amount.

// An arithmetic(算数) right shift shifts in the sign bit of the number in the shift register (q[63] in this case) instead of zero as done by a logical right shift. Another way of thinking about an arithmetic right shift is that it assumes the number being shifted is signed and preserves the sign, so that arithmetic right shift divides a signed number by a power of two.

// There is no difference between logical and arithmetic left shifts.

// load: Loads shift register with data[63:0] instead of shifting.

// ena: Chooses whether to shift.

// amount: Chooses which direction and how much to shift.

// 2'b00: shift left by 1 bit.

// 2'b01: shift left by 8 bits.

// 2'b10: shift right by 1 bit.

// 2'b11: shift right by 8 bits.

// q: The contents of the shifter.

**注意**:算数右移和逻辑右移的区别

>>逻辑右移不考虑符号位,空缺的位置补领操作即可

>>算数右移动需要考虑符号位,右移一位,如果符号位为1,则在符号位补1,如果符号位为0,则在符号位补0.即算数右移后,空缺的位置补符号位的数字即可

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @(posedge clk)begin

if(load)begin

q <= data;

end

else if(ena) begin

case(amount)

2'b00: q <= {q[62:0],1'b0};

2'b01: q <= {q[55:0], 8'b0};

2'b10: q <= {q[63],q[63:1]};//有符号数右移动 如果符号位为1,则右移后是补1;如果符号位为0,则右移后是补0

2'b11: q <= { { 8{q[63]} },q[63:8]};

endcase

end

else q <= q;

end

endmodule

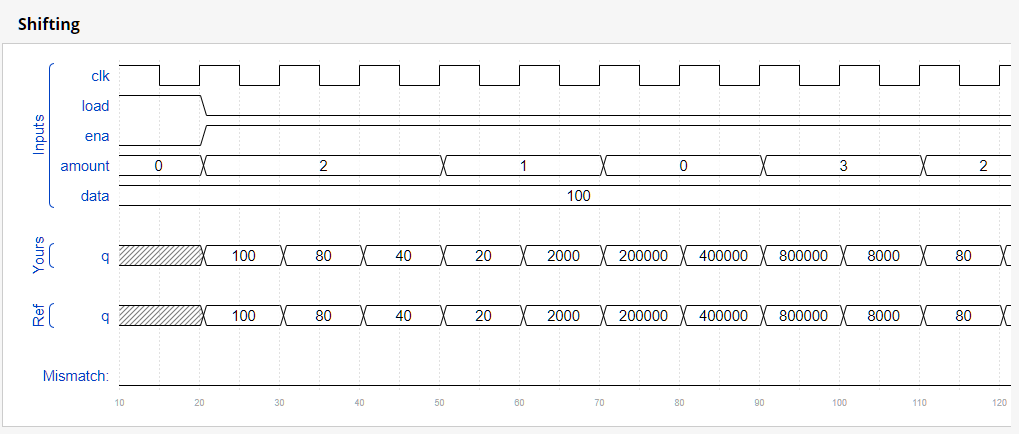

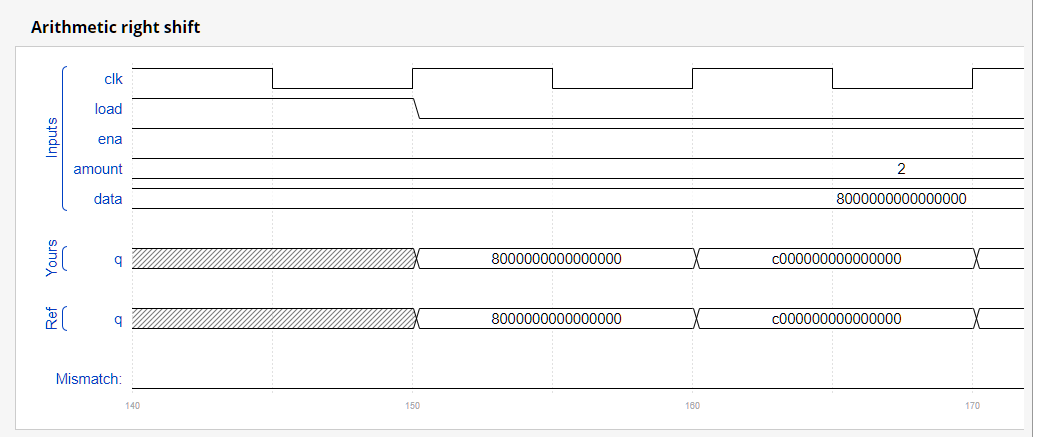

仿真图:

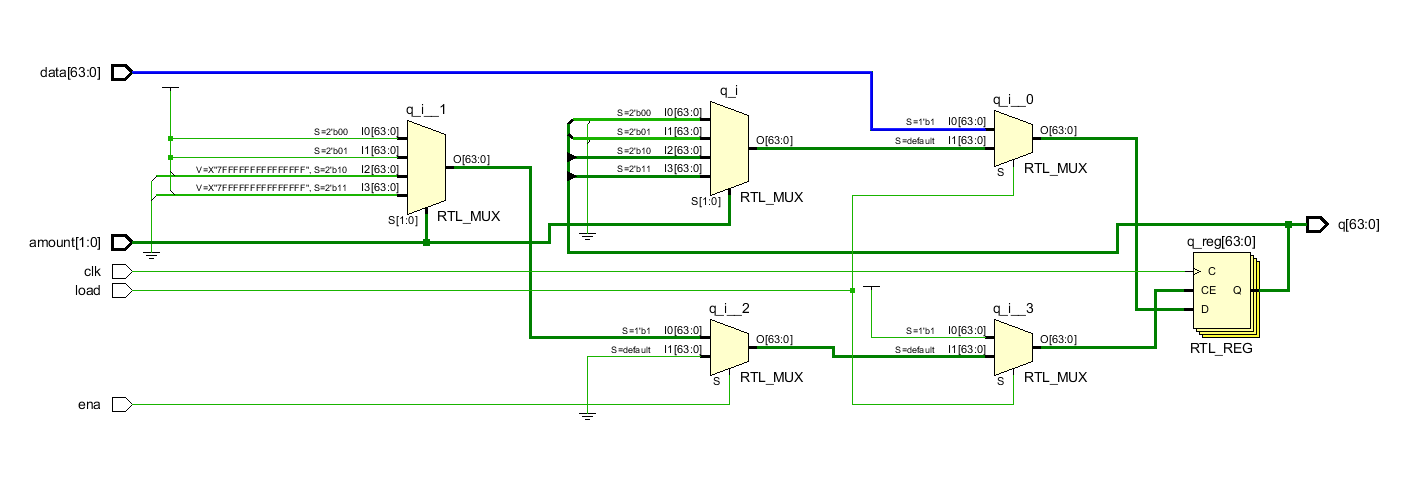

原理图:

HDLbits——Shift18的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- mysql中int、bigint、smallint 和 tinyint四种数据类型

最近在做数据库表设计的时候,对于多种数字的数据类型的选择存在很多顾虑,不是很清楚到底如何选择.总结一下int.bigint.smallint 和 tinyint四种数据类型. bigint:从 -2^ ...

- 深入理解JVM - 自动内存管理

对于从事C.C++程序开发的开发人员来说,在内存管理领域,他们既是拥有最高权力的"皇帝",又是从事最基础工作的劳动人民--既拥有每一个对象的"所有权",又担负着 ...

- JS:获取元素属性

元素上属性字段 const el = document.getElementById('documentLabel') console.log(el.clientWidth) // 可见区域宽 con ...

- HID类的JoyStick描述符

目录 应用程序改自沁恒官网的CH583EVT包中的CompoundDev工程,配合下方的描述符能够实现①直接接电脑,在设备管理器中能够查到被电脑识别为HID- compliant game conto ...

- mathjs 数字处理

// mathjs 四舍五入取整 val:值export function roundingInt(val) { if (val) { return math.round(val, 0) }}// m ...

- 文件下载,后端接口,django,flask

Django后端接口 def download_excel(request): """ get excel file from url param and upload ...

- 【实验】B站资源免费下载技巧you-get

搭建环境, python pip3 install you-get 查看可以下载格式 you-get -i https://www.bilibili.com/video/BV1yN411d7KH?p ...

- Ubuntu下安装Node.js+ThreeJs

以具有sudo特权的用户身份运行以下命令,以下载并执行NodeSource安装脚本 curl -sL https://deb.nodesource.com/setup_16.x | sudo -E b ...

- Java_类与对象

类与对象 概念 类是抽象的,概念的,代表一类事物,比如人类.猫类--,即它是数据类型. 对象是具体的,实际的,代表一个具体事物,即使实例. 类是对象的模板,对象是类的一个个体,对应一个实例 对象在内存 ...

- 性能测试-dstat以及sar(网络相关数据查看)

1.dstat参数说明 # 安装 yum install dstat -y dstat命令不加任何参数时,会收集CPU.磁盘.网络.分页.系统的数据信息,每秒收集一次.缺省参数时相当于dstat -c ...