https://mp.weixin.qq.com/s/afRVgTCYs1Mxu898uSmVaQ

整理一篇介绍Diplomacy和TileLink的文章。

0. ABSTRACT

Modern systems-on-chip (SoCs) incorporate a large and growing number of specialized hardware units that must be integrated into a unified address space via a shared bus topology.

This process is labor-intensive and error-prone because the interface requirements of all connected blocks must be mutually satisfied.

The design productivity gains derived from the modularity of RISC-V are bottlenecked by the need to integrate the cross product of processor variants, bus ordering behaviors, and slave device capabilities.

This growing complexity has stimulated development of new tools and methodologies to enable the completion of complex and parameterized SoC designs.

We present two tools used to create correct-by-construction interconnects in the Rocket Chip generator:

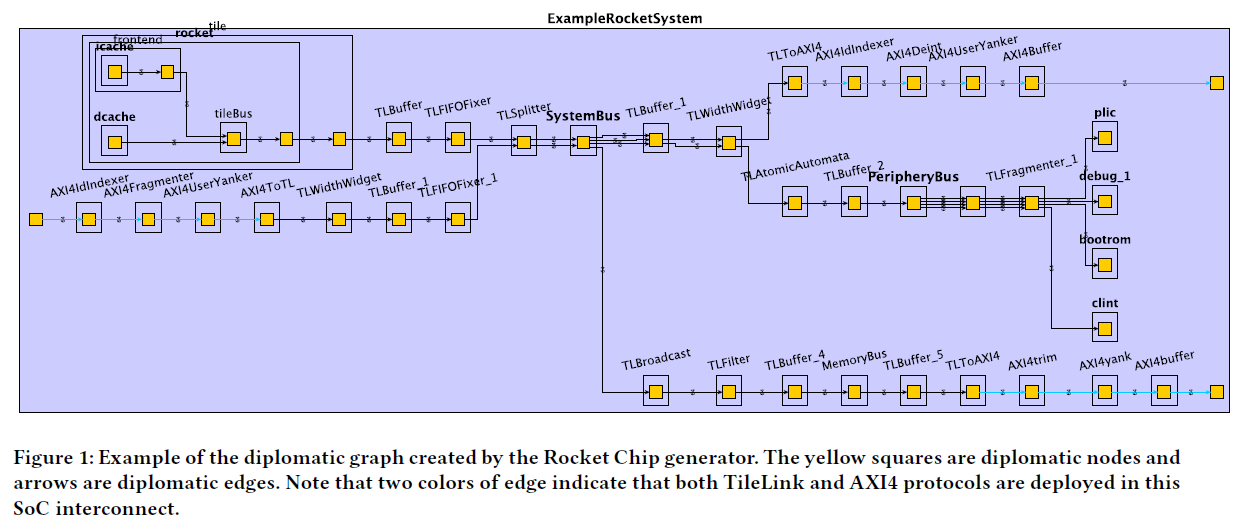

Diplomacy is a parameter negotiation framework for generating parameterized protocol implementations. Beyond confirming the mutual compatibility of the system endpoints, Diplomacy enables them to specialize themselves based on knowledge of the other endpoints included in a particular system.

TileLink is a highly-parameterized chip-scale shared-memory interconnect standard. The implementation of TileLink in the Rocket chip generator exploits Diplomacy to specialize the interconnect to different levels of protocol conformance.

1. INTRODUCTION

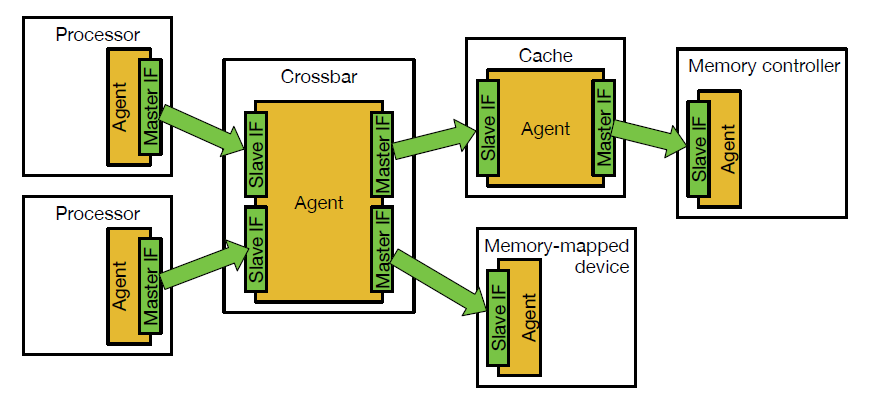

Modern systems-on-chip (SoCs) incorporate an ever-growing number of hardware units specialized to perform particular computational tasks. In order to communicate with one another and memory, these diverse compute resources must be integrated into a shared interconnection network. Such a network typically consists of a hierarchical topology of buses that provide the compute engines with a shared global address space.

The process of creating such interconnects is labor-intensive and error-prone because the interface requirements of all connected blocks must be mutually satisfied.

The design productivity gains derived from the modularity of RISCV are bottlenecked by the need to integrate the cross product of processor variants, bus ordering behaviors, and slave device capabilities. This growing complexity has stimulated development of new tools and methodologies to enable the completion of complex and parameterized chip designs [8].

We present two tools used to create provably-correct interconnects in the Rocket Chip SoC generator [1].

Our approach is centered around first constructing a graphical model of the properties

of the proposed interconnect design, and then using this model to reason as to whether the solution provides all required functionality and will exhibit correct behavior.

"Correct" in this case means (a)the generated design will be free from protocol-level deadlock, (b)is guaranteed to make forward progress, and that (c)the cross-product of masters' and slaves' operational requirements is satisfied.

Diplomacy is a framework for negotiating the parameterization of protocol implementations.

Given (a)a description of sets of interconnected master and slave devices, and (b)a bus protocol template,

Diplomacy cross-checks the requirements of all connected devices, negotiates free parameters, and supplies final parameter bindings to adapters and endpoints for use in their own hardware generation processes.

Beyond confirming the mutual compatibility of the system endpoints, Diplomacy enables them to specialize themselves based on knowledge about the capabilities of other endpoints included in a particular system.

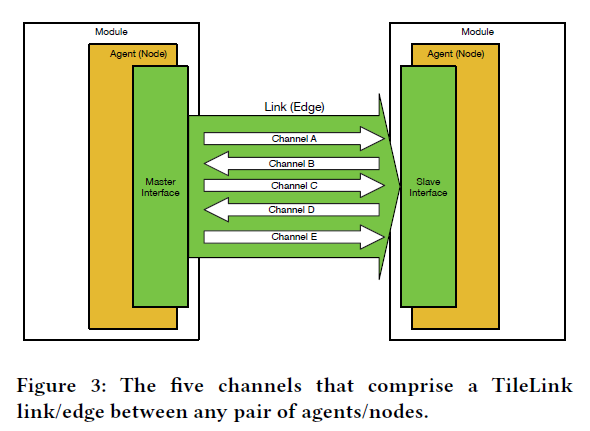

TileLink is a highly-parameterized chip-scale shared-memory interconnect protocol standard [5].

The protocol is hierarchically composable and guaranteed to deadlock-free at the transaction level[9]. The implementation of TileLink in the Rocket Chip generator exploits Diplomacy to supply a heterogeneous level of protocol conformance across the interconnect, specialized for the capabilities of devices connected to certain buses.

This paper discusses how various features of diplomatic TileLink have guided the design patterns we have adopted in the Rocket Chip generator.

(a)We avoid manually specifying any protocol parameters that can be inferred from a declarative description of the system interconnection network graph.

(b)We parameterize our generators to emit hardware based on their view of the rest of the system.

(c)We deploy a set of graph transformation patterns that make it easy to re-time links by inserting queues, that comprise thin single-purpose adapters, and that safely create hierarchies of interoperable components.

2. DIPLOMACY

3. TILELINK

4. DESIGN PATTERNS

4.1 DRYing Out Parameterization

4.2 Hardware Generation with A View

4.3 Correct By Composition

5. CONCLUSION

In this paper we have discussed how various features of diplomatic TileLink have guided the design patterns adopted in the Rocket Chip generator.

We avoid re-specifying any parameters that can be inferred from a declarative description of the system interconnect graph.

We parameterize our generators to emit hardware based on a diplomatically negotiated view of the system.

We deploy a set of safe graph transformation patterns that make it easy to re-time

links with queues, that compose more complicated adapters from single-purpose ones, and that inject hierarchies of composable components at standardized attachment points.

We see many forthcoming opportunities to deploy correct-by-construction

software development methods to other aspects of SoC hardware component integration.

Clock domains are one area where each mixed-in component could specify how it relates to the overall interconnect graph, and the correct clock and reset would be supplied to the second phase elaboration automatically.

Interrupts are another type of signal where we would like to avoid any explicit notion of cardinality and instead infer it from graphical structure.

Finally, we are working to develop endpoint generators that are protocol-independent, presenting generator authors with standard APIs that allow their device to be deployed regardless of the underlying interconnect protocol.

The Rocket Chip code base containing Diplomacy itself, all of our diplomatic bus protocol implementations, and a variety of TileLink-compatible cache, interconnect, and device generators, is open source and available as part of the Free Chips Project at

6. REFERENCES

略

- Rocket - 断句 - Diplomacy and TileLink from the Rocket Chip

https://mp.weixin.qq.com/s/rfgptF9YxDpzDoespYtQvA 整理Diplomacy and TileLink from the Rocket Chip这篇文 ...

- Head First Design Patterns

From Head First Design Patterns. Design Principle: Idnetify the aspects of your application that var ...

- 设计模式(Design Patterns)Java版

设计模式(Design Patterns) ——可复用面向对象软件的基础 设计模式(Design pattern)是一套被反复使用.多数人知晓的.经过分类编目的.代码设计经验的总结.使用设计模式是为了 ...

- java Design Patterns

设计模式(Design Patterns) ——可复用面向对象软件的基础 设计模式(Design pattern)是一套被反复使用.多数人知晓的.经过分类编目的.代码设计经验的总结.使用设计模式是为了 ...

- Java基础学习总结(37)——Java23中设计模式(Design Patterns)详解

设计模式(Design Patterns) --可复用面向对象软件的基础 设计模式(Design pattern)是一套被反复使用.多数人知晓的.经过分类编目的.代码设计经验的总结.使用设计模式是为了 ...

- 图书-软件架构:《Design Patterns: Elements of Reusable Object-Oriented Software》(即后述《设计模式》一书)

ylbtech-图书-软件架构:<Design Patterns: Elements of Reusable Object-Oriented Software>(即后述<设计模式&g ...

- Design Patterns Simplified - Part 3 (Simple Factory)【设计模式简述--第三部分(简单工厂)】

原文链接:http://www.c-sharpcorner.com/UploadFile/19b1bd/design-patterns-simplified-part3-factory/ Design ...

- word-break|overflow-wrap|word-wrap——CSS英文断句浅析

---恢复内容开始--- word-break|overflow-wrap|word-wrap--CSS英文断句浅析 一 问题引入 今天在再次学习 overflow 属性的时候,查看效果时,看到如下结 ...

- Design Patterns Simplified - Part 2 (Singleton)【设计模式简述--第二部分(单例模式)】

原文链接: http://www.c-sharpcorner.com/UploadFile/19b1bd/design-patterns-simplified-part-2-singleton/ De ...

随机推荐

- Java 设置PDF中的文本旋转、倾斜

本文介绍通过Java程序在PDF文档中设置文本旋转.倾斜的方法.设置文本倾斜时,通过定义方法TransformText(page);并设置page.getCanvas().skewTransform( ...

- Spring中bean的四种注入方式

一.前言 最近在复习Spring的相关内容,这篇博客就来记录一下Spring为bean的属性注入值的四种方式.这篇博客主要讲解在xml文件中,如何为bean的属性注入值,最后也会简单提一下使用注解 ...

- Power BI:社保、公积金增减

本月和上月比较,社保.公积金有增减,拓展开来,每两个相邻月份比较,社保.公积金有增减. 数据放在SQL Server Express,有公司.姓名.分类.个人缴费金额.单位缴费金额.年月等字段,uni ...

- BufferedInputStream:字节缓冲输入流

package com.itheima.demo01.BufferedStream; import java.io.BufferedInputStream; import java.io.FileIn ...

- HDU 2007 (水)

题目链接:http://acm.hdu.edu.cn/showproblem.php?pid=2007 题目大意:给你段连续数字,让你求 all sum of (偶数2 )and all sum of ...

- Linux 命令行下搜索工具大盘点,效率提高不止一倍!

在 Linux 命令行下进行文本关键字的搜索,大家肯定第一时间会想到 grep 命令.grep 命令确实十分强大,但如果需要用到它更加灵活的功能时,可能命令就会显得十分复杂. 于是,为了简化 grep ...

- DVWA-File Upload

0x01 文件上传 File Upload,即文件上传漏洞,通常是由于对上传文件的类型.内容没有进行严格的过滤.检查,使得可以通过上传webshell获取服务器权限,因此文件上传漏洞带来的危害常常是毁 ...

- 漫谈Huawei LiteOS五大内核模块

[摘要]Huawei LiteOS是华为面向IoT领域,构建的“统一物联网操作系统和中间件软件平台”,以轻量级(内核小于10k).低功耗(1节5号电池最多可以工作5年),快速启动,互联互通,安全等关键 ...

- 微信小程序var和let以及const有什么区别

微信小程序var和let以及const的区别: 在JavaScript中有三种声明变量的方式:var.let.const. var:声明全局变量,换句话理解就是,声明在for循环中的变量,跳出for循 ...

- xampp apache 安全性问题

要禁止 Apache 显示目录结构列表,只需将 Option 中的 Indexes 去掉即可.<Directory "D:/Apa/blabla"> Options I ...