DFT scan chain

现代集成电路的制造工艺越来越先进,但是在生产过程中的制造缺陷也越来越难以控制,甚至一颗小小的PM2.5就可能导致芯片报废,为了能有效的检测出生产中出现的废片,需要用到扫描链测试(scan chain),由此产生了可测性设计即 DFT flow。

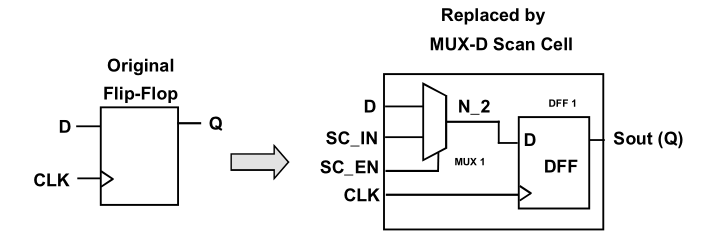

DFT 第一步是做 scan chain,首先将电路中的普通 DFF 换成 scan DFF:

scan DFF 是在原DFF 的输入端增加了一个 MUX,于是多了几个 pin :scan_in,scan_enable,scan_out

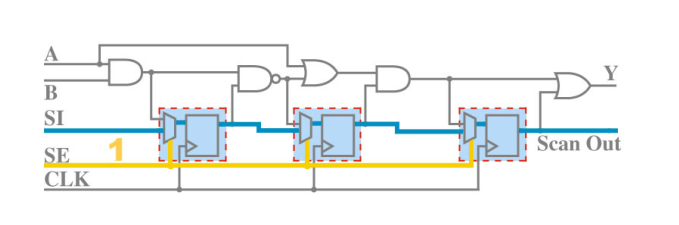

换完之后将所有的 scan DFF 首尾依次串接起来,就构成了一条 scan chain :

当 SE 信号(即 scan enable )有效时,电路进入scan 状态,此时数据通路如下图:

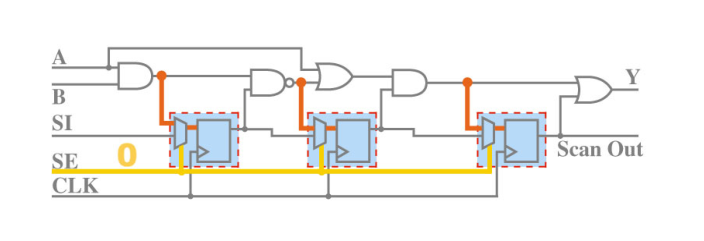

当 SE 信号无效时,电路工作在 normal 状态,数据通路如下图:

那么,这样一条 scan chain 是如何检测到电路中的缺陷呢?

简单来讲,scan chain 工作时分为三个步骤: load ····> capture ····> unload

load 是将input pattern 打入 scan chain

capture 是将每一级组合逻辑的结果打入下一级register

unload 是将scan chain 中的数据串行输出,得到 output pattern

下图是一个简单的 scan chain 工作原理示意图:

结合上图,可知scan mode 的工作步骤如下:

1. 将普通的 register 替换为 scan register

2. 将 scan register 首尾依次串接起来

3. 在 SE 有效拉高时,将 input pattern 串行打入scan register

4. 然后 SE 拉低,等 Reg/Q 的值经过组合逻辑运算后到达下一级 reg 的D 端

5. 再产生一个 capture pulse 将 D 端的值打入寄存器

6. 最后 SE 拉高,将 reg 中的值依次串行输出,得到 output pattern

7. 如果 output pattern 和预期的输出结果相同,说明电路工作正常

否则说明电路制造有问题,属于废片了

Question : 为什么 cts 时, func clock 和scan clock 经常出现长不齐?

|--------------------------------|

DFT scan chain的更多相关文章

- LPC43XX JTAG Scan Chain

Debug and trace functions are integrated into the ARM Cortex-M4. Serial wire debug and trace functio ...

- IC 设计中DFT的Boundary Scan功能

在很大规模的IC设计中,往往会有一些各种各样的bug出现,不论是在前期design的过程,还是在post silicon流片回来chip的flaw,都会导致chip的功能的失败,时钟频率无法达到期望频 ...

- scan design flow(一)

一个典型的scan实现的flow: clock mux和一些rst,在Scan中都被bypass掉,是不能测到的.所以DFT的test coverage一般就在97%或98%. scan design ...

- DFT设计绪论

DFT设计的主要目的是为了将defect-free的芯片交给客户. 产品质量,通常使用Parts Per million(PPM)来衡量. 但是随着IC从SSI到VLSI的发展,在test上花销的时间 ...

- scan & ATPG

Testability用来表征一个manufactured design的quality. 将testability放在ASIC前端来做,成为DFT(Design For Test),用可控(cont ...

- DFT 工程师三大法宝的使用

众所周知,芯片主要由三大部分构成. 芯片示例-可见下图 1.与电路板和其他芯片的接口-IO pad 2.存放程序的空间-RAM和ROM 3.搭建逻辑电路的基本组件 –标准逻辑单元 DFT工程师所有的工 ...

- DFT,可测试性设计--概念理解

工程会接触DFT.需要了解DFT知识,但不需要深入. 三种基本的测试(概念来自参考文档): 1. 边界扫描测试:Boundary Scan Test: 测试目标是IO-PAD,利用JTAG接口互连以方 ...

- DFT 问答 I

Q: Boundary Scan是什么?应用场景是什么?实现的方法是什么?挑战是什么? A: Boundary Scan就是边界扫描,是由Joint Test action Group起草的规范,最初 ...

- DFT测试-OCC电路介绍

https://www.jianshu.com/p/f7a2bcaefb2e SCAN技术,也就是ATPG技术-- 测试std-logic, 主要实现工具是: 产生ATPG使用Mentor的 Test ...

随机推荐

- Substrings(hdu1238)字符串匹配

Substrings Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/32768 K (Java/Others)Total Sub ...

- Codeforces485D(SummerTrainingDay01-K)

D. Maximum Value time limit per test:1 second memory limit per test:256 megabytes input:standard inp ...

- python学习之老男孩python全栈第九期_数据库day005知识点总结 —— MySQL数据库day5

三. MySQL视图(不常用) 给某个查询语句设置个别名(视图名),日后方便使用 - 创建: create view 视图名 as SQL; PS:视图是虚拟的 - 修改: alter view 视图 ...

- 使用PHP把图片上传到七牛

先从官网下载SDK,然后新建一个文件,里面包括上传,下载,删除 <?php header("Content-Type:text/html; charset=utf8"); r ...

- css翻译名词术语

原文 本书译法 其它译法(未采用) CSS - 层叠样式表.级联样式表.样式单 cascade 层叠(机制) 级联 fallback 回退(机制.措施.方案) 后备.回落.降级 selector 选择 ...

- HTML中的元素分类

HTML中有很多的标签(元素),可以按照这些元素在网页中所占的空间情况进行分类.具体可以这样简单的分类: 1.块级元素:指的是在网页中该元素独自占据网页的一行显示区域,即当使用了该元素后,该元素会使下 ...

- PostGIS安装

PostGIS安装 1.软件下载 postgresql-9.6.1-1-windows-x64-binaries.zip https://www.postgresql.org/download/win ...

- Nginx控制客户端请求的速率

使用ngx_http_limit_req_module模块的两个参数 ngx_http_limit_req_module模块用于限制每个IP访问每个定义key的请求速率 1.limit_req_zon ...

- fastjson 反序列化漏洞利用总结

比赛遇到了,一直没利用成功,这里做个记录. 环境搭建 首先用 vulhub 搭建 fastjson 的漏洞环境. 漏洞环境程序的逻辑为接收 body 的数据然后用 fastjson 解析. 漏洞利用 ...

- Android 限定符

Android中一些常见的限定符可以参考下表. 使用最小宽度限定符 在上一小节中我们使用large限定符成功解决了单页双页的判断问题,不过很快又有一个新的问题出现了,large到底是指多大呢?有的时候 ...