FPGA时钟分频(转)

http://www.cnblogs.com/fpga/archive/2009/10/24/1589318.html

占空比为50%的分频

偶数分频比较简单

比如N分频,那么计数到N/2-1,然后时钟翻转,代码如下:

1 module even(clk_in,clk_out,rst_n);

2 input clk_in;

3 input rst_n;

4 output clk_out;

5

6 parameter N=6;

7

8 reg [3:0] cnt;

9 reg clk_out;

10

11 always @(posedge clk_in or negedge rst_n) begin

12 if(!rst_n) begin

13 cnt<=4'b0000;

14 clk_out<=0;

15 end

16 else if(cnt==(N/2-1)) begin

17 clk_out<=~clk_out;

18 cnt<=4'b0000;

19 end else cnt<=cnt+1;

20 end

21 endmodule

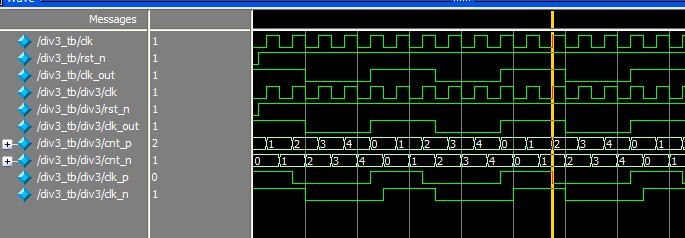

实现奇数分频,分别用上升沿计数到(N-1)/2-1,再计数到N-1,再用下降沿计数到(N-1)/2-1,再计数到N-1,,得到两个波形,然后相或即可 代码如下:

1 module div3(clk,clk_out,rst_n);

2 input clk,rst_n;

3 output clk_out;

4

5 reg [3:0] cnt_p,cnt_n;

6 reg clk_p,clk_n;

7 parameter N=5;

8

9 always @(posedge clk or negedge rst_n) begin

10 if(!rst_n)

11 cnt_p<=4'h0;

12 else if(cnt_p==N-1)

13 cnt_p<=0;

14 else cnt_p<=cnt_p+1;

15 end

16

17 always @(negedge clk or negedge rst_n) begin

18 if(!rst_n)

19 cnt_n<=4'h0;

20 else if(cnt_n==N-1)

21 cnt_n<=0;

22 else cnt_n<=cnt_n+1;

23 end

24

25 always @(posedge clk or negedge rst_n) begin

26 if(!rst_n)

27 clk_p<=1;

28 else if(cnt_p==(N-1)/2-1)

29 clk_p<=~clk_p;

30 else if(cnt_p==(N-1))

31 clk_p<=~clk_p;

32 end

33

34 always @(negedge clk or negedge rst_n) begin

35 if(!rst_n)

36 clk_n<=1;

37 else if(cnt_n==(N-1)/2-1)

38 clk_n<=~clk_n;

39 else if(cnt_n==(N-1))

40 clk_n<=~clk_n;

41 end

42 assign clk_out=clk_n|clk_p;

43 endmodule

FPGA时钟分频(转)的更多相关文章

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- 时钟分频方法---verilog代码

时钟分频方法---verilog代码 本文以SDI播出部分的工程为例,来说明一种时钟分频的写法.SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据 ...

- FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2.4.8.16.32.64等这些以2的整数倍的. 这里说的是奇数倍分频,如时钟是100MH ...

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- 基于FPGA的飞机的小游戏

基于FPGA的飞机的小游戏 实验原理 该实验主要分为4个模块,采用至上而下的设计方法进行设计.由50M的晶振电路提供时钟源,VGA显示控制模块.图形显示控制模块.移动模块的时钟为25M,由时钟分频电路 ...

- 实验箱FPGA部分测试报告及A8与FPGA链接测试报告

其实,我一开始还以为实验箱不会有什么问题只是让我们多学习东西才做这个测试的,结果发现还真的有不少问题. 1.实验准备部分 安装驱动时,win10系统无法正确安装usb-blaster Windows ...

- verilog实现奇数倍分频

在学习FPGA的过程中,最简单最基本的实验应该就是分频器了, 同时分频器也是FPGA设计中使用频率非常高的基本设计之一, 尽管在芯片厂家提供的IDE中集成了锁相环IP, 如altera 的PLL,Xi ...

随机推荐

- SVN版本控制图标经常延时显示或未显示问题解决方法

项目中,使用svn经常遇到,文件或文件夹图标延时显示或未显示的问题,终于找到办法解决 客户端:TortoiseSVN

- 客户机中PLSQL DEV访问虚拟机中的ORCLE11g,错误百出!

客户机中PLSQL DEV访问虚拟机中的ORCLE11g,错误百出! 创建时间: 2017/10/14 18:44 作者: CNSIMO 标签: ORACLE 忙了一下午,只有两个字形容:麻烦! ...

- Opencv怎么读入,显示,保存图像-OpenCV步步精深

怎么读入图像呢? 我们用 img = cv2.imread('图像路径\原图像名称',0) 原图像名称要有后缀 .png , .jpg等等原图像带有的后缀. 这里我们着重说明一下图像路径,这个路径一定 ...

- 使用wget做站点镜像及wget的高级用法

本文为大家介绍 使用wget做站点镜像及wget的高级用法,供大家学习参考. # wget -r -p -np -k http://xxx.edu.cn -r 表示递归下载,会下载所有的链接,不过要注 ...

- WPF 绑定密码

我们发现我们无法绑定密码框的密码,PasswordBox 的 Password 不能绑定. 我们想做 MVVM ,我们需要绑定密码,不能使用前台 xaml.cs 监听 密码改变得到密码的值,传到 Vi ...

- 【转】缓存淘汰算法系列之2——LFU类

原文地址 :http://www.360doc.com/content/13/0805/16/13247663_304916783.shtml 1. LFU类 1.1. LFU 1.1.1. 原理 L ...

- USACO奶牛博览会(DP)

Description 奶牛想证明他们是聪明而风趣的.为此,贝西筹备了一个奶牛博览会,她已经对N头奶牛进行了面试,确定了每头奶牛的智商和情商. 贝西有权选择让哪些奶牛参加展览.由于负的智商或情商会造成 ...

- Memcached存储命令

Memcached各个存储命令的语法格式都类似,且有相同的参数和参数含义,先将可能出现的各个参数的意义说明如下: key: 键值 key-value 结构中的 key,用于查找缓存值. flag ...

- LeetCode 112. Path Sum (二叉树路径之和)

Given a binary tree and a sum, determine if the tree has a root-to-leaf path such that adding up all ...

- LeetCode 31. Next Permutation (下一个排列)

Implement next permutation, which rearranges numbers into the lexicographically next greater permuta ...