Verilog-同步FIFO

参考博客:https://blog.csdn.net/hengzo/article/details/49683707

1、基本框图

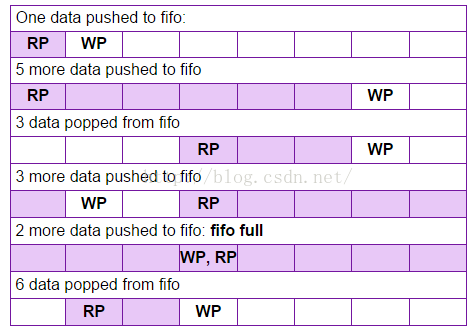

1)双端口RAM加两个读写指针

2)写数据、写使能、写满;读数据、读使能、读满

2、代码思路

1)Full和Empty的产生:使用fifo_counter记录FIFO RAM中的数据个数,等于0时,给出empty信号,等于BUF_LENGTH时,给出full信号

2)fifo_counter的更新:发生有效写操作时+1,发生有效读操作时-1,同时发生读写操作时不变

3)读写指针的控制:读写指针宽度与地址宽度相当,地址增加而溢出后,自动变成0。循环指针。初始时刻都指到0,发生有效写时写指针+1,写指针指向将要写的地址;发生有效读时读指针-1,读指针指向将要读的地址。

3、代码

`timescale 1ns / 1ps module synchronous_fifo

#(parameter BUF_WIDTH=, //地址宽度为3,

parameter BUF_SIZE=) //数据个数,FIFO深度

(

input clk,

input rst_n,

input wr_en,

input rd_en,

input [:] buf_in,

output [:] buf_out,

output buf_full,

output buf_empty,

output [BUF_WIDTH:] fifo_cnt

); reg [:] buf_mem [:BUF_SIZE-]; // 双端口RAM

reg [BUF_WIDTH-:] rd_ptr,wr_ptr; // 读写指针

reg [:] buf_out_reg;

reg [BUF_WIDTH:] fifo_cnt_reg; // 存入数据的计数,0-8,位宽要比地址位宽大1 //========= 写入 ============

always @(posedge clk) begin

if(wr_en&&!buf_full) begin

buf_mem[wr_ptr] <= buf_in;

end

end //========= 读出 ============

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

buf_out_reg <= 'd0;

end

else begin

if(rd_en&&!buf_empty) begin

buf_out_reg <= buf_mem[rd_ptr];

end

else buf_out_reg <= buf_out_reg;

end

end assign buf_out = buf_out_reg; //========= 数据计数 ============

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

fifo_cnt_reg <= {(BUF_WIDTH+){'b0}};

end

else begin

if((wr_en&&!buf_full)&&((rd_en&&!buf_empty)))

fifo_cnt_reg <= fifo_cnt_reg;

else if(wr_en&&!buf_full)

fifo_cnt_reg <= fifo_cnt_reg+'b1;

else if(rd_en&&!buf_empty)

fifo_cnt_reg <= fifo_cnt_reg-'b1;

else fifo_cnt_reg <= fifo_cnt_reg;

end

end

assign fifo_cnt = fifo_cnt_reg; //========= 读写指针控制 ============

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

rd_ptr <= {BUF_WIDTH{'b0}};

end

else begin

if(rd_en&&!buf_empty) rd_ptr <= rd_ptr + 'b1;

else rd_ptr <= rd_ptr;

end

end always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

wr_ptr <= {BUF_WIDTH{'b0}};

end

else begin

if(wr_en&&!buf_full) wr_ptr <= wr_ptr + 'b1;

else wr_ptr <= wr_ptr;

end

end //========= 空满判断 ============

assign buf_full = (fifo_cnt_reg == BUF_SIZE)?'b1:1'b0;

assign buf_empty = (fifo_cnt_reg == {(BUF_WIDTH+){'b0}})?1'b1:'b0; endmodule

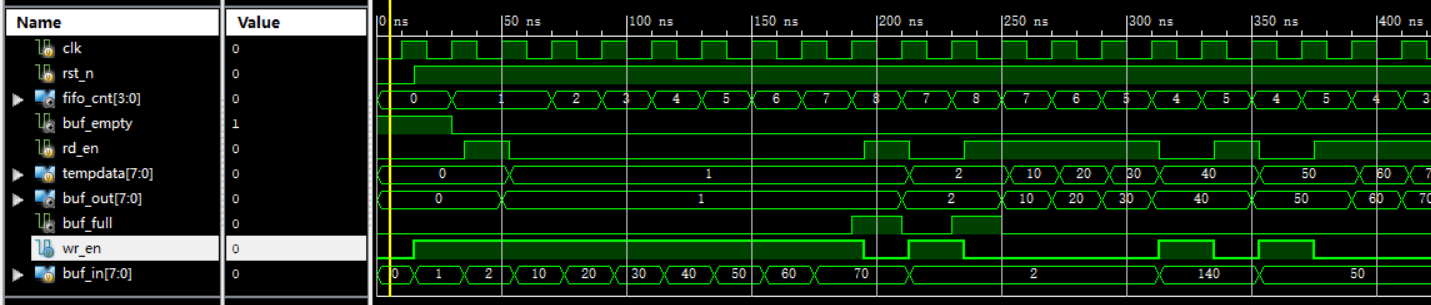

his is a Full version of ISim.

Time resolution is ps

Simulator is doing circuit initialization process.

Finished circuit initialization process.

Push

Push

------Poped:

Push

Push

Push

Push

Push

Push

Push

---Cannot push : Buffer Full---

---Cannot push : Buffer Full---

---Cannot push : Buffer Full---

---Cannot push : Buffer Full---

---Cannot push : Buffer Full---

---Cannot push : Buffer Full---

------Poped:

Push

------Poped:

------Poped:

------Poped:

------Poped:

Push

------Poped:

Push

------Poped:

------Poped:

------Poped:

------Poped:

------Poped:

---Cannot Pop: Buffer Empty---

---Cannot Pop: Buffer Empty---

---Cannot Pop: Buffer Empty---

---Cannot Pop: Buffer Empty---

---Cannot Pop: Buffer Empty---

---Cannot Pop: Buffer Empty---

Push

------Poped:

Verilog-同步FIFO的更多相关文章

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- 怎么用Verilog语言描述同步FIFO和异步FIFO

感谢 知乎龚大佬 打杂大佬 网上几个nice的博客(忘了是哪个了....) 前言 虽然FIFO都有IP可以使用,但理解原理还是自己写一个来得透彻. 什么是FIFO? Fist in first out ...

- 同步fifo的Verilog实现

FIFO是一种先进先出的数据缓存器,他与普通存储器相比: 优点:没有外部读写地址线,这样使用起来非常简单: 缺点:只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存 ...

- 同步FIFO学习

在网上找的一个经典同步FIFO例子. 一.前言 FIFO (First-In-First-Out) 是一种先进先出的数据交互方式,在数字ASIC设计中常常被使用.FIFO按工作时钟域的不同又可以分为: ...

- 同步FIFO design and IP level verification

一.前言 应聘IC前端相关岗位时,FIFO是最常考也是最基本的题目.FIFO经常用于数据缓存.位宽转换.异步时钟域处理.随着芯片规模的快速增长,灵活的system verilog成为设计/验证人员的基 ...

- 同步fifo与异步fifo

参考以下帖子: https://blog.csdn.net/hengzo/article/details/49683707 https://blog.csdn.net/Times_poem/artic ...

- 同步fifo的verilogHDL设计实例

原创 设计一个fifo,输入16bit,输出16bit的data,寻址宽度5bit,有空满标志. top 层如下所示: /* date : 2014/10/14 version : modelsim ...

- E203 同步fifo

1. 输入端, 输入信号, i_vld,表示输入请求写同步fifo,如果fifo不满,则fifo发送i_rdy 到输入端,开始写fifo.i_vld和i_rdy是写握手信号. 2.输出端 o_rdy表 ...

- CYPEESS USB3.0程序解读之---同步FIFO(slaveFifoSync)

上一篇文章解读了CYPRESS FX3的GPIO的操作过程,下面解读同步FIFO的一个例子(slaveFifoSync). *生产者,消费者. 1.首先看DMA的回调函数(cyu3dma.h): ty ...

- FPGA SD 卡 之 乒乓操作 、同步fifo

这里记录一个实际的需要使用乒乓操作的例子:读sd卡数据的时,在spi的模式下.发送单数据块的读取命令,在回应之后会有 512字节的数据.使用乒乓操作,可以用两个八位的寄存器,就可以完成连续的512字节 ...

随机推荐

- ovirt kvm嵌套虚拟化

嵌 套式虚拟nested是一个可通过内核参数来启用的功能.它能够使一台虚拟机具有物理机CPU特性,支持vmx或者svm(AMD)硬件虚拟化.关于 nested的具体介绍,可以看这里 .该特性需要内核升 ...

- 练习2-14 求奇数分之一序列前N项和 (15 分)

练习2-14 求奇数分之一序列前N项和 (15 分) 本题要求编写程序,计算序列 1 + 1/3 + 1/5 + ... 的前N项之和. 输入格式: 输入在一行中给出一个正整数N. 输出格式: 在一行 ...

- mysql常用语句及实题训练

基本语句操作 创建数据库: create database database-name 1 删除数据库: drop database database-name 1 修改数据名: RENAME DAT ...

- Grevl旅游注册的初步界面,以源代码和运行图片展示

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <title> ...

- Selenium实现微博自动化运营:关注、点赞、评论

目录 Selenium 是什么? 一.核心代码 二.步骤分解 1.打开浏览器 2.访问微博登录页 3.输入账号密码 4.点击登录 5.通过人机验证 6.打开我们的中公题库君首页 7.加一下关注 8.定 ...

- WeChall_ Training: Stegano I (Training, Stegano)

This is the most basic image stegano I can think of. 解题: 一张小图片,文本方式打开.

- MVVM框架(二)---生命周期

一.Vue 生命周期图解: 这张图是官方给出的,大家可能都看过.其中我们重点讲述以下几个钩子函数: beforeCreate --> created beforeMount --> ...

- [Effective Java 读书笔记] 第三章类和接口 第十六条

第十六条 复合优先于继承 如果不确定B和A的关系是,is-a的关系,B确实也是A,那么久不应该使用B继承A,否则会暴露实现细节, 你的实现都会限制在原始的实现上. 书中举的第一个例子,实现了一个类ex ...

- pytorch --Rnn语言模型(LSTM,BiLSTM) -- 《Recurrent neural network based language model》

论文通过实现RNN来完成了文本分类. 论文地址:88888888 模型结构图: 原理自行参考论文,code and comment: # -*- coding: utf-8 -*- # @time : ...

- GNU C相关

GNU __attribute__ 用于在函数声明时,定义函数参数的一些特殊属性,比如,如果函数的某个参数可能用不到,那么,将该参数增加unused属性即可,如下(一般用两个括号包括属性unused) ...