FPGA中的时序分析(五)

时序约束实例详解

本篇博客结合之前的内容,然后实打实的做一个约束实例,通过本实例读者应该会实用timequest去分析相关的实例。本实例以VGA实验为基础,介绍如何去做时序约束。

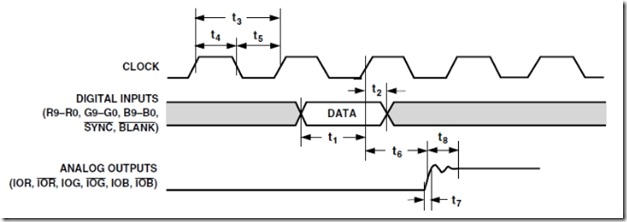

首先VGA这种情况属于供源时钟情况,不明白供源时钟的可以参看之前博客讲解。首先查看ADV7123的数据手册,查看其时序图。如下图所示,是建立时间和保持时间要求。

下图是时序图,可见t1和t2在时钟上升沿的位置,数据在时钟的上升沿进行采集。

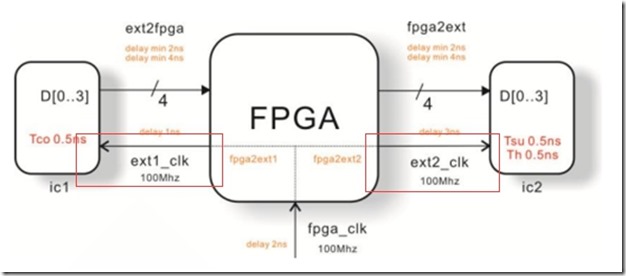

对于VGA实验来说,FPGA是发送端,ADV7123是接收端,如果传输的速率比较高的话,数据和时钟上升沿的严格对齐就要依靠PLL产生可调相位的时钟信号来保证,不过对于对于25MHz时钟通过较好的时序约束和分析后,则不必动用PLL。

接下来需要产生虚拟时钟,对于reg2reg路径的分析,其时钟都是FPGA内部,不用产生虚拟时钟,但是对于pin2reg或者reg2pin这种情况,需要产生一个虚拟时钟,作为pin端的时钟来分析时序。如下图中的标注所示。

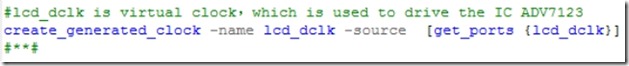

所以ADV7123和FPGA进行时钟相关的信号就是ADV7123的驱动时钟,明白这个信号之后,需要设置其虚拟时钟约束,如下图所示。

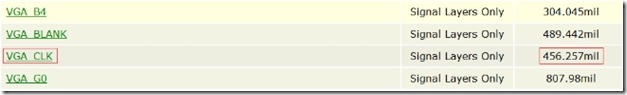

由于FPGA是相对于ADV7123为输出ADV7123所需要的信号,所以需要设置输出延迟约束。这一部分结合上一篇博客的分析,首先需要计算FPGA到ADV7123芯片的延迟,这一部分主要是PCB上面的信号走线延时。所以需要结合PCB走线来估计延迟时间。

打开altium designer,然后查看VGA模块的走线长度如下图1所示,长度大约是11.589mm。

图1 VGA模块走线长度

在FPGA核心板(笔者设计的一款学习板)上面的lcd_dclk的走线长度如下图2所示。长度大约是41.4mm。

图2 核心板走线长度

根据上述的计算,所以lcd_dclk总得走线长度 = 52.989mm。

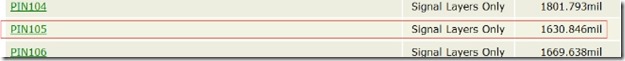

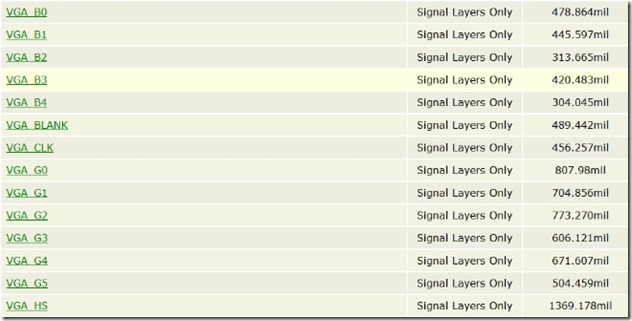

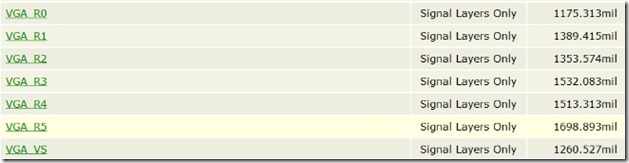

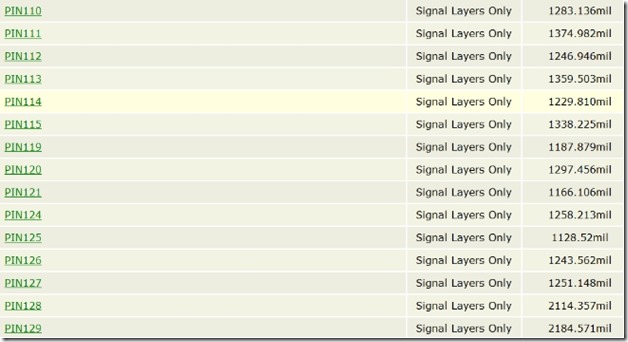

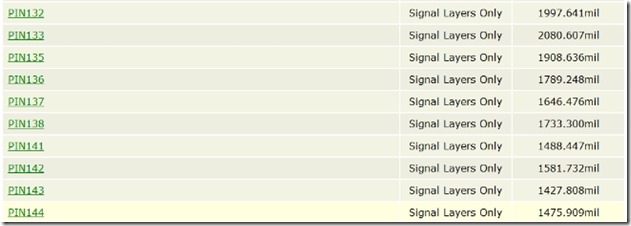

同样的道理,数据走线长度如下图3所示,此走线长度是VGA模块上面的长度,长度大约在7.72~43.152mm,那么对于核心板上面的走线模块长度如图4所示,大概长度约为28.65 ~ 53.32mm,总的长度为36.37mm~96.472mm,根据0.17ns/25.4mm,lcd_clk走线延迟0.35ns,数据总线延迟0.24ns~0.646ns。

图3 各信号走线延迟

图4 核心板各信号走线延迟

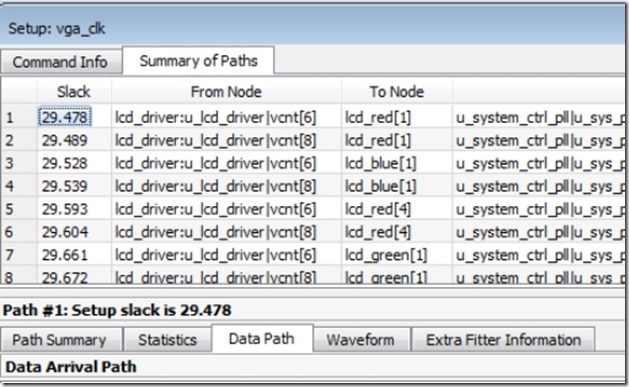

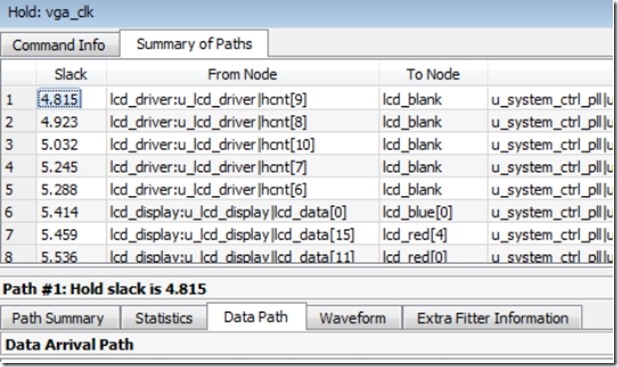

若是不考虑时钟偏移,那么进行时序分析得到的余量如图5所示。

图5 建立和保持余量

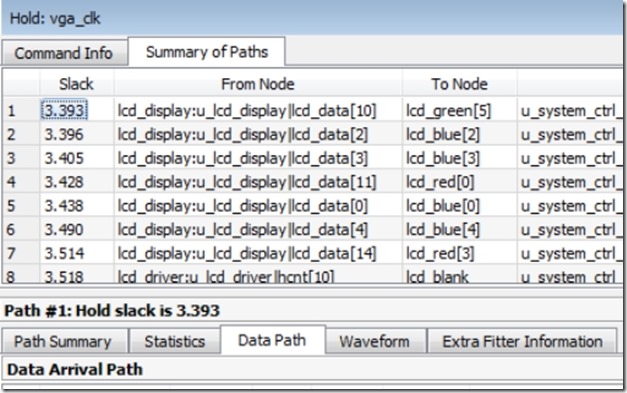

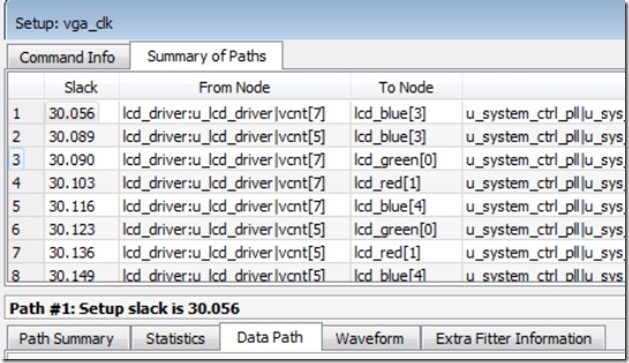

上述是计算完了FPGA到外部IC的延迟,但是还有时钟偏斜没有计算,那么需要用到set max/min delay 命令,对于lcd_dclk先估计一个范围,如0~5ns即可,这个范围肯定是满足要求,但是可能会不能够留有更多的余量。然后在将有时钟偏移的延迟时间代入set output delay的表达式中,此处利用公式将lcd_dclk 最大延迟设为3ns,lcd_dclk最小延迟设为1ns,那么考虑时钟偏斜的输出最大值 = 0.646 + 0.2 -3 = -2.154ns;输出最小值 = 0.24 - 1.5 - 1 = -2.26ns;

图6是约束后的建立余量和保持余量,可以看到满足时序要求,并保有很大的时序余量。

图6 建立余量和保持余量

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================

FPGA中的时序分析(五)的更多相关文章

- FPGA中的时序分析(一)

谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获.笔者 ...

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- FPGA中的时序分析(三)

验证公式正确性 前两篇博客提及了关于时序的建立余量和保持余量的计算.结合实际情况,验证公式的运算正确性.结合之前博客提及的LED实验,看一下建立余量和保持余量是否都合格. 建立余量 图1是最大时钟 ...

- FPGA中的时序分析(二)

使用Timequest 笔者对Altera较熟悉,这里以quartus ii中的timequest作为讲解. Timequest分析时序的核心,也就是在于延迟因数的计算.那么建立约束文件,去告诉tim ...

- 【转载】FPGA 中的latch 锁存器

以下这篇文章讲述了锁存器的一些概念和注意事项.原文标题及链接: FPGA 中的latch 锁存器 - 快乐至永远上的博客 - 与非博客 - 与网 http://www.eefocus.com/liuy ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- Android中Button的五种监听事件

简单聊一下Android中Button的五种监听事件: 1.在布局文件中为button添加onClick属性,Activity实现其方法2.匿名内部类作为事件监听器类3.内部类作为监听器4.Activ ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

随机推荐

- vivado中设置多线程编译

VIVADO中一个run编译时支持的线程数如下表:(综合时一般是2线程) Place Route Windows默认 2 2 Linux默认 4 4 Windows开启maxThreads=8 4 4 ...

- Vivado与SDK的联合调试方法-使用ILA

首先介绍一下我的硬件平台:使用的开发板为米联客出的MIZ702,这个开发板与ZedBoard是兼容的. Vivado硬件调试有几种手段:ILA(集成逻辑分析器Integrated Logic Anal ...

- 【Unity】12.3 Off Mesh Link组件

开发环境:Win10.Unity5.3.4.C#.VS2015 创建日期:2016-05-09 一.简介 Off Mesh Link组件用于手动指定路线来生成分离的网格连接.例如,游戏中让行进对象上下 ...

- 【Unity】3.5 导入音频文件

分类:Unity.C#.VS2015 创建日期:2016-04-05 一.简介 音频文件 (Audio File) 资源的选择原则应该以无故障地流畅运行为宗旨.下面列出了常用的音频文件. .AIFF ...

- 【小白的CFD之旅】20 计算区域的构建

计算域是什么计算域如何创建常用的建模软件计算域几何的特殊之处具体的计算域提取方法小白总结 自从上次在食堂听了小牛师兄关于计算网格的一些问题后,小白决定在寒假期间好好的补习一下关于计算网格的划分内容.在 ...

- [Windows Azure] How to Configure Cloud Services

How to Configure Cloud Services To use this feature and other new Windows Azure capabilities, sign u ...

- iOS 添加功能引导图

iOS 添加功能引导图 首次安装app之后,打开app首页,有一张功能引导图,其实最简单的一种做法是,直接在这个首页上加一个蒙层图片. 在蒙层上用气泡显示文字注明功能介绍,这个蒙层图片,让你们的UI设 ...

- 九章面试题:Find first K frequency numbers 解题报告

Find first K frequency numbers /* * Input: int[] A = {1, 1, 2, 3, 4, 5, 2}; k = 3 * return the highe ...

- Python 调用datetime或者time获取时间的时候以及时间转换,最好设置一下时区 否则会出现相差8个小时的情况

在使用调用datetime或者time获取时间的时候以及时间转换,最好设置一下时区, 因为不同机器设置的时区不同,获取的时间可能就不对,正好我们使用的这两个服务器使用的都是东八区,所以没有问题,设置方 ...

- 【Linux】crontab 每隔1小时 2小时的执行job写法

crontab -l crontab -e 每五分钟执行 */5 * * * * 每小时执行 0 * * * * 每2小时执行 0 */2 * * * 每天执行 0 0 ...