Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi、Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号。列表有:

| Xi | Yi | Cin | Sum | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

由左边表格可知:

Sum=X’Y'Cin+X'YCin'+XY'Cin'+XYCin=X'(Y⊕Cin)+X(Y⊙Cin)=X'(Y⊕Cin)+X(Y⊕Cin)'=X⊕Y⊕Cin

Cout=X’YCin+XYCin'+XY'Cin+XYCin=XY+(X⊕Y)Cin

如果取:P=X⊕Y ; G=XY

那么:Sum=P⊕Cin Cout=PCin+G

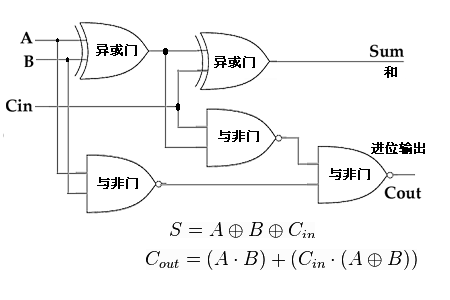

图中对Cout的公式进行了,即Cout'=(AB)'(PCin)'=(AB)'((A⊕B)Cin)'

下面是全加器的门级Verilog语言描述:

module Fadd(x,y,Cin,Cout,Sum);

input x,y,Cin;

output Cout,Sum;

wire a,b,c; xor xor1(a,x,y);

xor2(Sum,a,Cin);

and and1(b,x,y);

and2(c,Cin,a);

or or1(Cout,b,c); endmodule

全加器的行为描述:

module add(x,y,Cin,Sum,Cout);

input x,y,Cin;

output Sum,Cin;

assign Sum=x^y^Cin;

assign Cout=x&y+(x^y)&Cin;

endmodule

module add_N(x,y,Cin,Cout,Sum);

input x,y,Cin;

output Sum,Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

利用行为级描述的Verilog全加器可以很简单的扩展成4位或者16位等全加器:

module add_4(x,y,Cin,Cout,Sum);

input [:]x,y;

input Cin;

output [:]Sum;

output Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

module add_N(x,y,Cin,Cout,Sum);

input [N-:]x,y;

input Cin;

output [N-:]Sum;

output Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

Verilog学习笔记简单功能实现(二)...............全加器的更多相关文章

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(五)...............序列检测设计

这里采用夏宇闻教授第十五章的序列检测为例来学习; 从以上的状态转换图可以写出状态机的程序: module seqdet(x,out,clk,rst); input x,clk,rst; output ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(七)...............接口设计(并行输入串行输出)

利用状态机实现比较复杂的接口设计: 这是一个将并行数据转换为串行输出的变换器,利用双向总线输出.这是由EEPROM读写器的缩减得到的,首先对I2C总线特征介绍: I2C总线(inter integra ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- Verilog学习笔记简单功能实现(一)...............D触发器

module D_flop(data,clk,clr,q,qb); input data,clk,clr; output q,qb; wire a,b,c,d,e,f,ndata,nclk; nand ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第二十二章:四元数(QUATERNIONS)

原文:Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第二十二章:四元数(QUATERNIONS) 学习目标 回顾复数,以及 ...

随机推荐

- java stopwatch 功能

C#中有一个stopwatch的功能,主要是用来监测程序执行时间的.java之前一直都在用如下方式完成: public static void main(String[] args) { long s ...

- Android开发-之第一个程序:HelloWorld!

小编觉得不管学习什么编程的时候,第一个程序都是要求打印输出一个"HelloWorld!",那就从最简单的HelloWorld开始吧!哈哈~~~~ 一.创建一个Android工程 1 ...

- SQL语句来查询今天、昨天、7天内、30天的数据,经典!

---恢复内容开始--- 今天的所有数据:select * from 表名 where DateDiff(dd,datetime类型字段,getdate())=0 昨天的所有数据:select * f ...

- ClickOnce部署(3):使用证书

在讲述证书的使用前,我们先来了解另外一个知识——发布网页. 在前面所说的ClickOnce部署中,如果大家细心的话,应该会发现这么个问题. 如上图,发布成功后,在"输出"窗口中提示 ...

- 推荐12个漂亮的 CSS3 按钮实现方案

在过去,我们都是使用图片或者JavaScript来实现漂亮的按钮效果,随着越来越多的浏览器对CSS3的支持和完善,使用CSS3来实现美观的按钮已没有太多的障碍.今天,本文收集了12个很不错的CSS3按 ...

- nodejs+edatagrid读取本地excel表格

- VXLAN 概念(Part II)- 每天5分钟玩转 OpenStack(109)

上一节我们介绍了 VXLAN 的封装格式以及 VTEP.今天我们将通过例子讨论 VXLAN 封装和转发包的过程,以及 Linux 对 VXLAN 的原生支持. VXLAN 包转发流程 VXLAN 在 ...

- Web APi之HttpClient注意事项以及建议(四)

前言 之前对于用SelfHost来手动实现Web API的宿主模式,似乎不是太深入,所以本篇文章我们一起来讨论关于利用HttpClient来访问Web API上的资源来进行探讨以及注意相关事项,希望此 ...

- 关于JqueryEasyUI集合Kindeditor

写在前面 上一篇<初试JqueryEasyUI(附Demo)>: 在上一篇说过,下面要试下easyui集合编辑器,关于编辑器网上有很多,ckeditor.ueditor.kindedito ...

- spring源码分析之定时任务Scheduled注解

1. @Scheduled 可以将一个方法标识为可定时执行的.但必须指明cron(),fixedDelay(),或者fixedRate()属性. 注解的方法必须是无输入参数并返回空类型void的. @ ...