[转载]Vivado轻松实现IP封装

Vivado轻松实现IP封装

1、新建一个测试工程

工程化的设计方法是离不开工程的,第一步往往都是新建工程,后面我会学习去工程化的开发方法,可能会更加高效。

2、利用向导完成IP封装

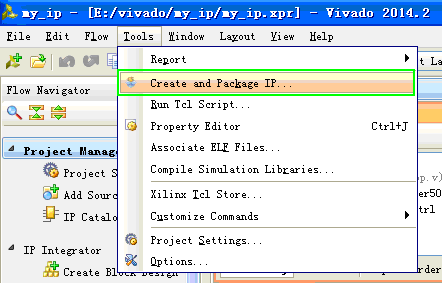

2.1、启动IP向导

方法为:ToolsàCreate and Package IP…,如图1所示。

图1 创建或者打包IP

点击Create and Package IP…命令,弹出向导,如图2所示。

图2 创建和封装IP向导

直接NEXT,进入下一界面,如图3所示。选择操作类型,我们这里不是新建IP,也不是要打包当前工程,而是要把runled_src文件夹下封装成一个IP,所以选择第2项。NEXT。

图3 选择操作类型为封装特定目录

接下来一步要注意了,选择你要打包的资源所在的文件夹,我这里是把要打包的3个文件放在了my_ip/runled_src下面,所以选择了这个路径,如图4所示。

图4 待打包资源所在文件夹

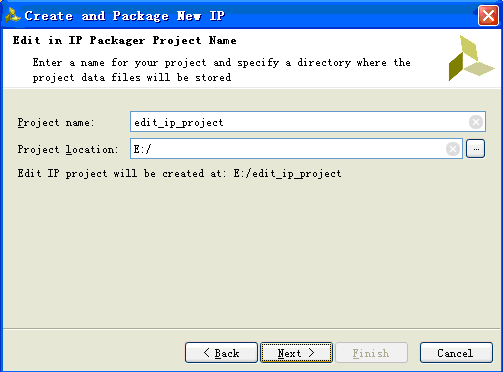

接下来,向导提示需要为IP工程制定一个名字和存储地址,如图5所示。这里采用默认名称即可,这个工程是临时的,IP封装完之后就会消失,再次编辑IP时才会再重新建立。

图5 临时工程名称、存储路径

NEXT,接下来就是最后一步了,是一些提示信息,大家可以自己看一下。点击Finish结束向导。

图6 summary

2.2、IP参数设置

注意,这里已经进入了edit_ip_project工程,是为打包IP核新建的那个工程,我们在上面指定了名称和路径(见图5).

对打包后的IP进行一些参数配置,如供应商,分类(默认是BaseIP,使用时要到该分类下查找我们封装的IP)等信息,这里不一一详述了,需要时,自行修改即可。

图7 IP参数设置

下一步:不做属性上的修改,直接进入最后一步(单击Review and Package),点击图8中的Package IP按钮,开始打包。

图8 开始打包

打包完成后,edit_ip_project工程会自动关闭,返回我们建立的测试工程。

3、查看IP封装结果

在Flow Navigator子窗体下找到Project Manager à IP Catalog,单击IP Catalog,右侧会弹出IP Catalog子窗体,将BaseIP目录展开,发现runled_top_v1_0已经成功导入。

到这里,封装已经完成了,本文要叙述的主题也已经完毕。

------------------------------------------------------分割线---------------------------------------------------------------

但由于是第一次使用,不太放心,所以测试一下,接下爱来各小节是测试用的,不想看的可以直接略过。

4、测试

建立一个Block Design,将runled_top_v1_0添加进去,添加输入输出端口,最终结果如图9所示。

图9 Block Design

5、添加约束、综合、实现、生成Bitstream

约束文件:

#In the following the XDC constraint is matched to the origanal UCF constraint, XDC above, UCF below # Commented

set_property PACKAGE_PIN Y9 [get_ports {iClk}]

set_property IOSTANDARD LVCMOS33 [get_ports {iClk}]

#NET GCLK LOC = Y9 | IOSTANDARD=LVCMOS33; # "GCLK"

# Bank 33, Vcco = 3.3V

#set_property IOSTANDARD LVCMOS33 [get_ports -filter { IOBANK == 33 } ]

set_property PACKAGE_PIN T22 [get_ports {oLed[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[0]}]

#NET LD0 LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"

set_property PACKAGE_PIN T21 [get_ports {oLed[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[1]}]

#NET LD1 LOC = T21 | IOSTANDARD=LVCMOS33; # "LD1"

set_property PACKAGE_PIN U22 [get_ports {oLed[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[2]}]

#NET LD2 LOC = U22 | IOSTANDARD=LVCMOS33; # "LD2"

set_property PACKAGE_PIN U21 [get_ports {oLed[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[3]}]

#NET LD3 LOC = U21 | IOSTANDARD=LVCMOS33; # "LD3"

set_property PACKAGE_PIN V22 [get_ports {oLed[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[4]}]

#NET LD4 LOC = V22 | IOSTANDARD=LVCMOS33; # "LD4"

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[5]}]

set_property PACKAGE_PIN W22 [get_ports {oLed[5]}]

#NET LD5 LOC = W22 | IOSTANDARD=LVCMOS33; # "LD5"

set_property PACKAGE_PIN U19 [get_ports {oLed[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[6]}]

#NET LD6 LOC = U19 | IOSTANDARD=LVCMOS33; # "LD6"

set_property IOSTANDARD LVCMOS33 [get_ports {oLed[7]}]

set_property PACKAGE_PIN U14 [get_ports {oLed[7]}]

#NET LD7 LOC = U14 | IOSTANDARD=LVCMOS33; # "LD7"

# Bank 34, Vcco = Vadj

#set_property IOSTANDARD LVCMOS18 [get_ports -filter { IOBANK == 34 } ]

set_property IOSTANDARD LVCMOS18 [get_ports {iRst_n}]

set_property PACKAGE_PIN P16 [get_ports {iRst_n}]

#NET BTNC LOC = P16 | IOSTANDARD=LVCMOS18; # "BTNC"

生成Bitstream以便进行板级测试。

6、测试

利用Vivado内置的Hardware Manager向导将Bitstream烧写进FPGA,流水灯顺利出现,OK!

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521

EDN China: http://bbs.ednchina.com/BLOG_cuter521_356737.HTM

[转载]Vivado轻松实现IP封装的更多相关文章

- Vivado使用技巧:封装自己设计的IP核

概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原理图设计的方式,只需要在其中调用设计好的IP核连线.IP核一部分来自于Xilinx ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- 基于Vivado调用ROM IP core设计DDS

DDS直接数字式频率合成器(Direct Digital Synthesizer) 下面是使用MATLAB生成正弦波.三角波.方波的代码,直接使用即可. t=:*pi/^:*pi y=0.5*sin ...

- vivado自定IP例化的问题,怎么生成VHDL的例化

在tools 下面选中project settings.然后选targat language为VHDL .这样就会生成一个以VHDL语言为模板的ip. 转载:https://zhidao.baidu. ...

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断.PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势. 一.PL 侧定时 ...

- JavaScript面向对象轻松入门之封装(demo by ES5、ES6、TypeScript)

本章默认大家已经看过作者的前一篇文章 <JavaScript面向对象轻松入门之抽象> 为什么要封装? 封装(Encapsulation)就是把对象的内部属性和方法隐藏起来,外部代码访问该对 ...

- 【转载】 禁止国外IP访问你的网站

在网站的运维过程中,我们通过网站记录的IP列表记录有时候会发现很多国外的IP的访问,如美国的IP等,而很多的服务器攻击行为的发起点很有可能在国外,此时为了服务器安全的考虑,我们可以考虑禁止国外IP访问 ...

随机推荐

- Default Title

測試的標誌 代表意義 1. 關於某個檔名的『檔案類型』判斷,如 test -e filename 表示存在否 -e 該『檔名』是否存在?(常用) -f 該『檔名』是否存在且為檔案(file)?(常用) ...

- sass在mac中安装

$ curl -L https://get.rvm.io | bash -s stable $ source ~/.rvm/scripts/rvm $ rvm -v $ rvm install 2.0 ...

- Arrays.asList()注意

api: public static <T> List<T> asList(T... a) 返回一个受指定数组支持的固定大小的列表.(对返回列表的更改会“直接写”到数组.)此方 ...

- 关于<head></head>标签;<form></form>标签

<head> <title>此处写标题</title> 这是唯一能被用户看到的标记 <meta/>标签: 1.设置字符集:<meta http-e ...

- HTML CSS中比较重要的

在网页中有了HTML和CSS之后,我们还需要学会布局,我们可以将整个网页看做是一个DIV,然后将所有内容放入到这个DIV中. 内容中的每一块我们都可以用DIV包起来,我们将这个DIV看做一个盒子,然后 ...

- Visual Studio 创建C++或C#Windows程序

使用工具Visual Studio,创建一个C++或C#Windows程序,在主窗口中显示“Hello World”,用户可以用鼠标拖动“Hello World”在主窗口中移动 首先创建一个项目 选 ...

- php 函数strpos()

strpos() 函数查找字符串在另一字符串中第一次出现的位置. strpos(string,find,start) 返回 从string中的start位置开始找find第一次出现的位置 注意: s ...

- Linux下的网卡驱动程序的编写过程(转)

工作需要写了我们公司一块网卡的linux驱动程序.经历一个从无到有的过程,深感技术交流的重要.Linux作为挑战微软垄断的强有力武器,日益受到大家的喜爱.真希望她能在中国迅速成长.把程序文档贴出来,希 ...

- FizzBuzz 问题

public class FizzBuzz { static int start = 1; static int end = 100; public static void main(String[] ...

- C++ exception

从没用过C++STL中的exception(异常类),在使用rapidxml,操作XML文件时,发现在一个抛出异常的错误.关注了下,就模范着做. 我也专门写了个函数来分配内存,如果发现分配不成功,就抛 ...