Verilog的非阻塞语句放到顺序块中,综合出来怎样的逻辑电路?

情境:

FPGA里面计数器需要复位(计数值置零),与计数器状态有关的行为是状态机控制的,即状态机为CLEAR_TIMER状态时,计数器才完成清零动作。

清零有两个条件:(1)计数器值溢出(达到OVF门限);(2)清零信号有效(1有效)。这两个条件是独立的,没有先后关系的约束。

问题是:如何写Verilog语句,才使得这两个触发的优先级相同?

有两个思路:

一个是:

always@(posedge clk)begin

if(!rst_n)begin

stat_preload <= STAT_IDLE;

end

else begin

//*** Combined Transition

if((tim_cnt >= TIIM_OVF) || (1'b1 == tim_rst))begin // OR

stat_preload <= STAT_CLEAR_TIMER;

end

else begin

stat_preload <= stat_preload; // Status Latch

end

end

end

另一个:

always@(posedge clk)begin

if(!rst_n)begin

stat_preload <= STAT_IDLE;

end

else begin

//*** Separate Transition

if(tim_cnt >= TIM_OVF)begin

stat_preload <= STAT_CLEAR_TIMER;

end

else begin

stat_preload <= stat_preload; // Stay

end

if(1'b1 == tim_rst)begin

stat_preload <= STAT_CLEAR_TIMER;

end

else begin

stat_preload <= stat_preload; // Stay

end

end

end

这两种写法的区别在于:第一种,状态转移语句放在两个条件参与的单个if选择结构里面;第二种,状态转移语句放在分别的两个if选择结构里面。

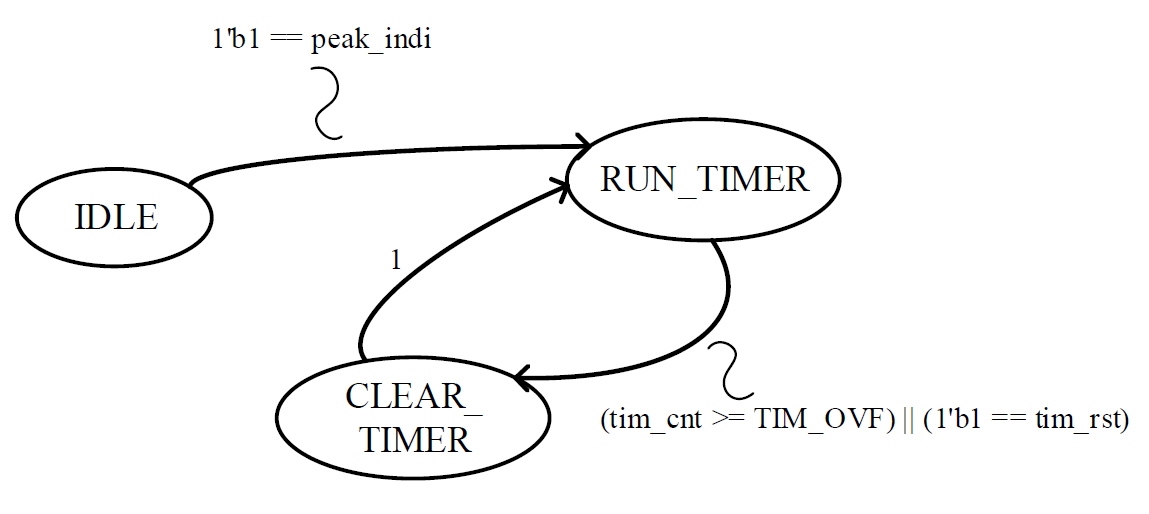

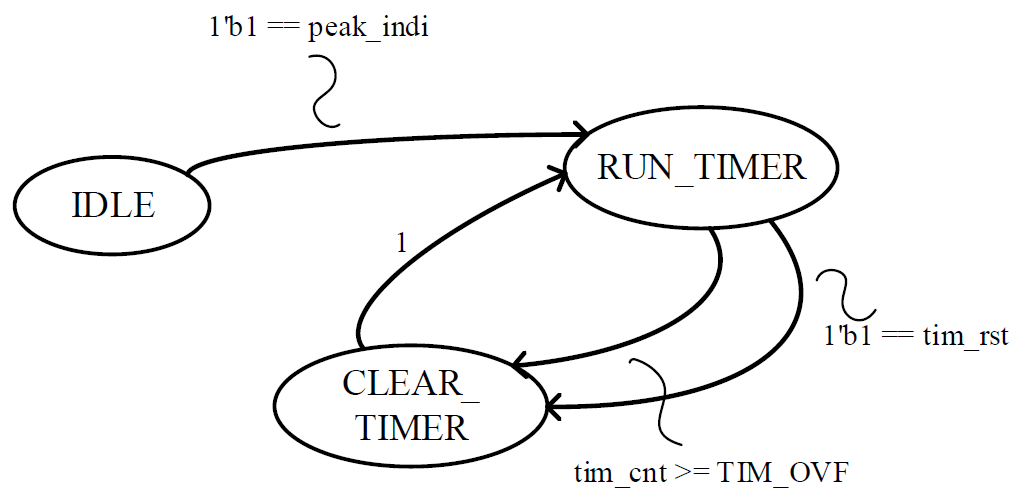

状态转移图中表现为这样的两种情况:

实现和测试:

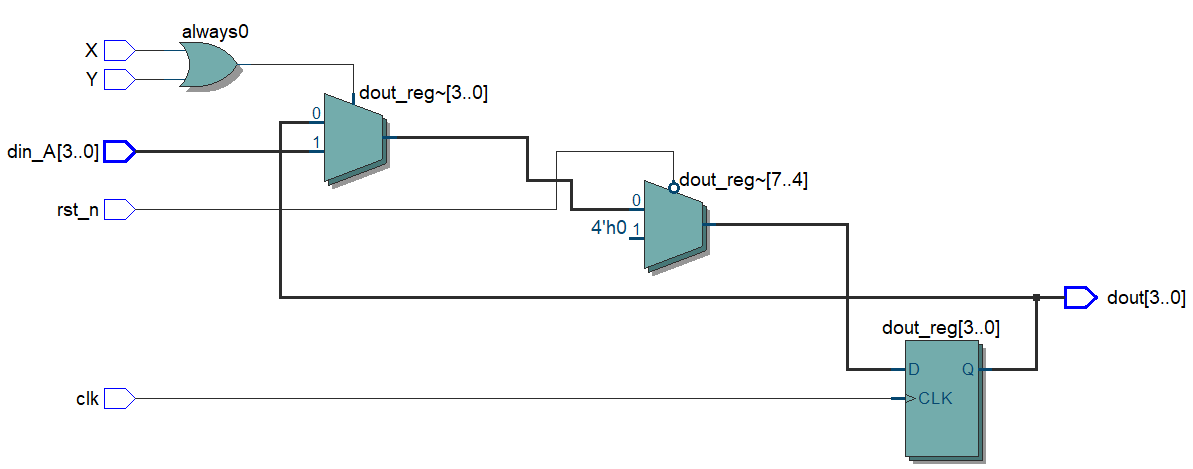

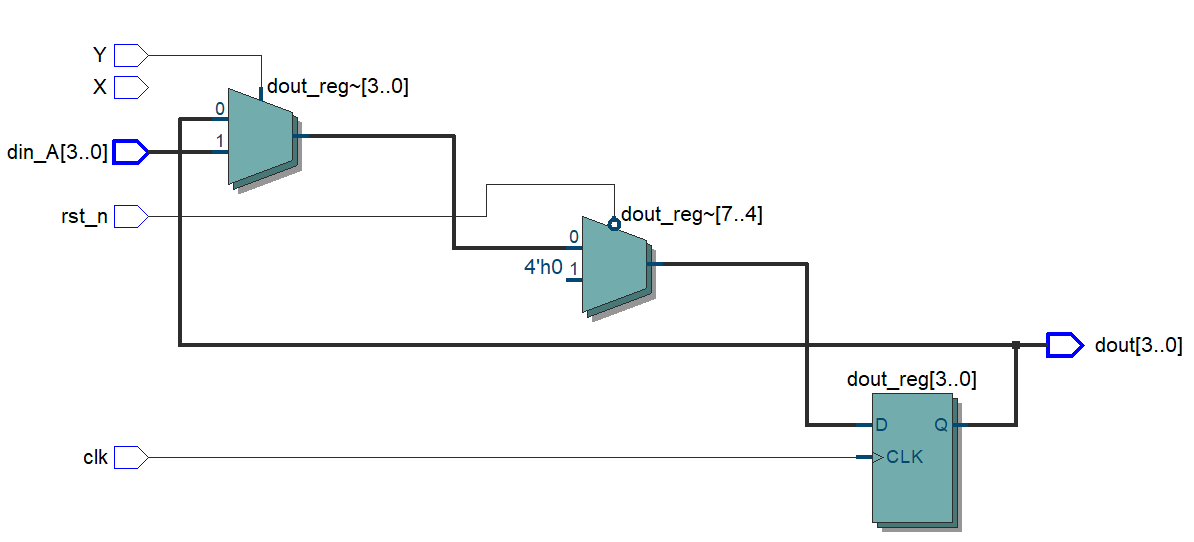

上述两种的代码和综合结果如下:

module top(

rst_n,

clk,

X,

Y,

din_A,

dout

); //****************************************

// Port Def.

//****************************************

input wire rst_n;

input wire clk; input wire X; // Conditions

input wire Y; input wire[:] din_A; output wire[:] dout; //****************************************

// Variables

//****************************************

reg[:] dout_reg; //****************************************

// Behaviour

//**************************************** assign dout = dout_reg; always@(posedge clk)begin

if(!rst_n)begin

dout_reg <= 'b0;

end

else begin

if(('b1 == X) || (1'b1 == Y))begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

end

end endmodule

module top(

rst_n,

clk,

X,

Y,

din_A,

dout

); //****************************************

// Port Def.

//****************************************

input wire rst_n;

input wire clk; input wire X; // Conditions

input wire Y; input wire[:] din_A; output wire[:] dout; //****************************************

// Variables

//****************************************

reg[:] dout_reg; //****************************************

// Behaviour

//**************************************** assign dout = dout_reg; always@(posedge clk)begin

if(!rst_n)begin

dout_reg <= 'b0;

end

else begin

if('b1 == X)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == Y)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

end

end endmodule

综合器是Quartus 15.1内置的。

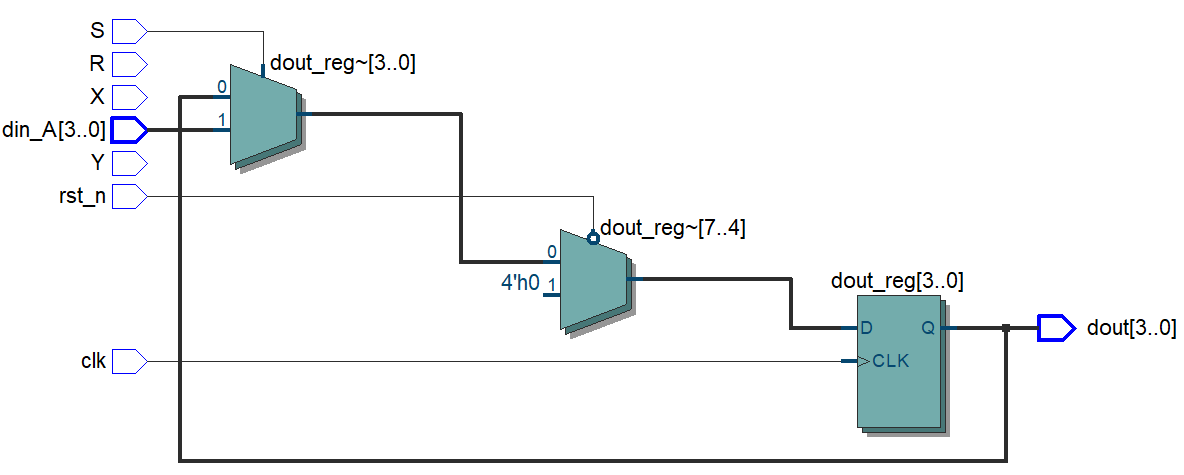

可以看到,第二种写法的综合结果让输入信号X没有驱动逻辑了,这样就与需求不符。

原因是什么?

第二种(分开if)情况下,虽然赋值语句都是非阻塞的<=,但是由于if语句放在顺序的begin::end结构内,所以判断和执行都是顺序处理的,状态转移和状态停留操作是一模一样的,所以X条件被省略了。

为了验证这个结论,在X,Y两个条件的基础上再加R,S两个条件,进行X,Y,R,S的顺序if,然后查看结果:

module top(

rst_n,

clk,

X,

Y,

R,

S,

din_A,

dout

); //****************************************

// Port Def.

//****************************************

input wire rst_n;

input wire clk; input wire X; // Conditions

input wire Y;

input wire R;

input wire S; input wire[:] din_A; output wire[:] dout; //****************************************

// Variables

//****************************************

reg[:] dout_reg; //****************************************

// Behaviour

//**************************************** assign dout = dout_reg; always@(posedge clk)begin

if(!rst_n)begin

dout_reg <= 'b0;

end

else begin

if('b1 == X)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == Y)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == R)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == S)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

end

end endmodule

显然,只有S条件有效了。

结论:顺序块begin::end中的语句是顺序执行的。

Verilog的非阻塞语句放到顺序块中,综合出来怎样的逻辑电路?的更多相关文章

- verilog中阻塞复制,非阻塞复制,顺序块,并行块之间的关系

这几个概念是不一样的 顺序块:顺序块中的语句是按顺序执行的,每条语句中的延迟值是与其前一条语句执行的仿真时间有关. 并行块:并行块语句是并行执行的,它里面的每条语句中指定的延迟值都是相对于语句块开始执 ...

- Verilog HDL中阻塞语句和非阻塞语句的区别

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“<=”).正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要. Verilog语言中讲的阻塞赋值与非 ...

- Verilog-FPGA硬件电路设计之一——if语句优先级(always块中的阻塞赋值生成的组合逻辑电路是按照顺利执行的)

出处:http://bbs.ednchina.com/BLOG_ARTICLE_3013262.HTM 综合软件:Quartus II 一.有优先级的if语句 if..else if.. else i ...

- Verilog中的阻塞与非阻塞

这篇文档值得阅读 按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈.但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过.当然一般情况程序中也是推荐用非阻塞的. ...

- Verilog之阻塞赋值非阻塞赋值

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1. 阻塞赋值与非阻塞赋值: 2. 代码测试: 3. 组合逻辑电路和时序逻辑电路. 阻塞赋值与非阻塞赋值: 1. 阻塞赋值" ...

- 07-阻塞赋值与非阻塞赋值原理分析——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:掌握阻塞赋值与非阻塞赋值的区别 实验平台:无 实验原理: 阻塞赋值,操作符为"=","阻塞"是指在进程语句( ...

- 用Java实现非阻塞通信

用ServerSocket和Socket来编写服务器程序和客户程序,是Java网络编程的最基本的方式.这些服务器程序或客户程序在运行过程中常常会阻塞.例如当一个线程执行ServerSocket的acc ...

- 非阻塞同步算法与CAS(Compare and Swap)无锁算法

锁(lock)的代价 锁是用来做并发最简单的方式,当然其代价也是最高的.内核态的锁的时候需要操作系统进行一次上下文切换,加锁.释放锁会导致比较多的上下文切换和调度延时,等待锁的线程会被挂起直至锁释放. ...

- 【Java并发编程】9、非阻塞同步算法与CAS(Compare and Swap)无锁算法

转自:http://www.cnblogs.com/Mainz/p/3546347.html?utm_source=tuicool&utm_medium=referral 锁(lock)的代价 ...

随机推荐

- 如何判断WLC的FUS版本

有些时候,我们在升级WLC的时候,被告知需要升级WLC的FUS,以防止某些漏洞和不必要的情况发生. 1.什么是FUS? Field Upgrade Software (FUS),翻译过来,叫“现场升级 ...

- Jmeter_用户定义的变量

1.线程组->添加->配置原件->用户定义的变量 2.自定义变量引用: ${ }

- Nginx笔试题!

1.Nginx实现HTTP及TCP负载均衡的模块?HTTP就是工作在七层协议TCP工作在四层协议 Nginx七层负载:七层通过虚拟的URL或主机名接收请求在server里面配置location反向代理 ...

- FTP文件传输服务!

一.FTP 连接及传输模式 1.控制连接:TCP 21,用于发送 FTP 命令信息2.数据连接:TCP 20,用于上传.下载数据3.数据连接的建立类型: (1)主动模式:服务器主动发起数据连接 (2 ...

- linux/centos之配置tomcat

一:下载tomcat压缩包 在http://archive.apache.org/dist/tomcat/中下载合适版本的tomcat,也可以在官网上下载,只是一般只有最新版本,选择二进制的后缀为ta ...

- 实现纸牌游戏的随机抽牌洗牌过程(item系列几个内置方法的实例)

实现纸牌游戏的随机抽牌洗牌过程(item系列几个内置方法的实例) 1.namedtuple:命名元组,可以创建一个没有方法只有属性的类 from collections import namedtup ...

- Linux进程内消息总线设计

文章目录 Windows平台进程内消息总线 如果没有消息总线,会产生什么问题 死循环包含关系 高耦合.低内聚 消息总线 结构图 原理 生产者与总线的关系 总线与消费者的关系 Linux进程内消息总线设 ...

- oracle的decode、sign、nvl,case...then函数

ORACLE几种常用的方法 1.decode 常见的用法 : 格式:decode(condition,value1,result[, value2,result2], default_result) ...

- Java 模拟斗地主

模拟斗地主 public class M1 { public static void main(String args[]) { DouDiZhu02(); } private static void ...

- Python 基础之linux基础相关

一: python3.6.x在Ubuntu16.04下安装过程 #(1)保证网络正常连接 sudo add-apt-repository ppa:jonathonf/python-3.6 (如果超时 ...