Verilog学习笔记

作者:桂。

时间:2017-06-24 11:07:40

链接:http://www.cnblogs.com/xingshansi/p/7039237.html

前言

Verilog是硬件描述语言,不算FPGA的核心部分,以前没有接触过,找了本书翻看一下(《Verilog数字系统设计教程第三版》),顺便记录一些基础知识,从第三章开始。

第三章:模块结构、基本数据类型、基本运算符

A-模块的结构

0、模块基本定义

一个基本的模块就是:

module name(in1,in2,...out1,out2,...)

//内部逻辑

endmodulw

模块基本定义涉及两个要点:1)其他模块作为input的调用;2)I/O位宽的设定。

1、always用法

情形一:

有

always @(a or b) begin

if(a) q<=b;

else q<=0;end

这个块是每当 a b发生变化时执行 还是a或者b中有一个是1或2个都是1时执行?答:每当A,B变化时,这个块就执行。 ALWAYS后面的叫敏感参数列表,不表示信号值,而是信号变化触发这个块的执行。

一般的,

如果ALWAYS块的敏感参数列表没有带时钟,这个块将被综合成一个组合回路。参照组合回路的真值表。当输入端任何一个信号变化时,输出将立即做相应的变化。

如果ALWAYS后代的是时钟,那ALWAYS块将被综合成一个时序回路。一般情况下,当时钟变化时,ALWAYS块执行。情形二:

always @(a) begin

如果这个a被定义为一个reg [4:0]时 程序怎么判断执行?答:如果综合逻辑没有问题,就是a的每一个元素变化时,这个块都要执行。

2、assign、wire、always

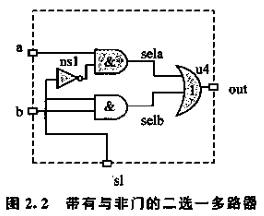

则块的描述语言为:

module muxtwo(out,a,b,s1)

input a,b,s1;//输入信号

output out;//输出

wire ns1,sela,selb; //定义内部连接线

assign ns1 = ~s1;

assign sela = a&ns1;

assign selb = b&s1;

assign out = sela|selb;

endmodule

其中assign声明语句。相当于连线,一般是将一个变量的值不间断地赋值给另一个变量.

对于reg与wire:

reg:

reg用在过程赋值语句中,而wire用在连续赋值语句中。(或者说reg在过程块内赋值,而wire在过程块外赋值)举个简单的例子module test(a, b, c);

input a;

input b;

output c;

reg c;

always @(posedge a)

begin

c = b;

end

endmodule这个时候,c只能声明为reg,因为c的赋值是在过程(procedure)中进行的。wire:module test(a, b, c);

input a;

input b;

output c;

wire c;assign c = a&b;

endmodule这里只能用wire。结合上图,wire定义了内部的连接节点,assign指定了逻辑关系。

3、实例元件

如:and #2 u1(q,a,b);

该语句表示:输入为a、b,逻辑关系为“与”,输出为q,延迟2个单位时间(#2)输出。

B-数据基本类型

0、常量

1)数字

二进制整数:b/B;十进制整数:d/D,八进制整数:o/O,十六进制整数:h/H;

8‘ha2 //位宽为8的十六进制

2)x、z、?

x:不定值

z/?:高阻值

3)负数

-8’d5

4)下划线

只能用在数字之间

16b'1010_1011_1111_0000

不说明位数,默认是32位。

5)parameter

parameter 参数名1=表达式, 参数名2= 表达式, 参数名3=表达式......

1、变量

1)wire型

上文已提及,wire型数据常用来表示用以assign关键字指定的组合逻辑信号。

2)reg型

reg数据默认的初始值为不定值x,常用来表示“always模块内的指定信号。”

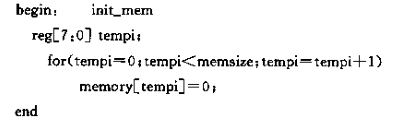

3)memory型

主要用来表示数组。

reg [n-1,0] 存储器名[m-1,0];

C-运算符及其表达式

最多只能三个?待验证

第四章:运算符、赋值语句和结构说明语句

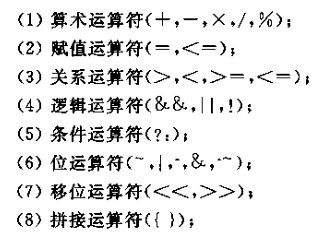

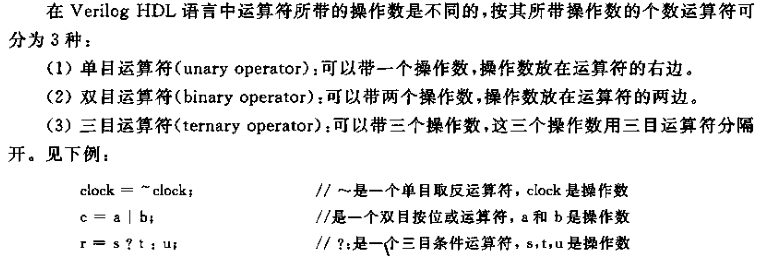

A-运算符

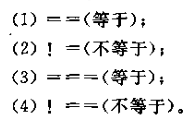

0、等式运算符

其中3、4包括x/z/?也进行比较,1、2则对此进行忽略。

1、拼接运算符

{a,b,c,...}实现拼接,

特别的,{4{w}};//表示{w,w,w,w}

2、缩减运算符

reg[3:0] B;

reg C;

C = &B;

相当于:

C = ((B[0]&B[1])&B[2])&B[3];//类似多米诺骨牌

B-赋值语句和块语句

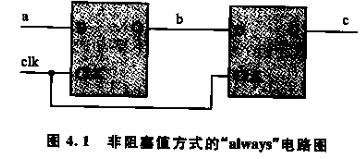

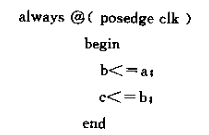

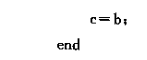

0、非阻塞赋值

1)赋值不是立刻发生;2)时序电路常用

对应就是

非阻塞:<=,阻塞:=

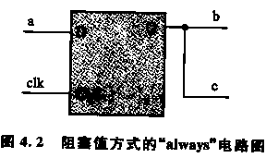

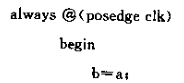

1、阻塞方式(相当于 值 直接塞过来,阻塞。)

1)立即赋值;2)时序电路慎用

对应

2、顺序块(begin ... end)

按顺序逐条执行。

—>A:表示触发事件A。

begin

语句1;

语句2;

end

或者

begin:块名

语句;

end

3、并行块(fork... join)

同时执行。

与begin ... end定义同。

第五章:条件语句、循环语句、块语句和生成语句

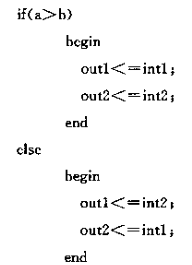

A-条件语句

0、条件语句

条件语句必须在过程块中使用,即由initial/always构成的语句(initial第六章提及)。

ex:

always@(some_event)

begein

if ....

end

if同样可以内嵌:

另外,$display,$write用于信息的显示和输出。

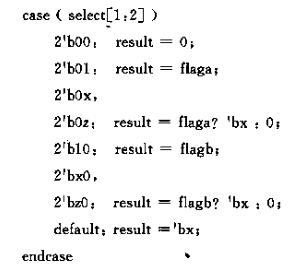

1、case语句

2、循环语句

1)forever语句:周期性执行,只能在initial中使用。

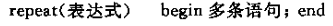

2)repeat:

表达式通常指定循环次数。

3)while语句

4)for语句

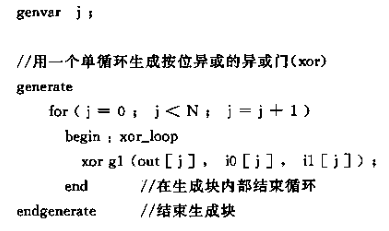

3、生成块

感觉这个在重复操作/子模块切割(如只修改局部)应该会起作用。

genvar j;//借助genvar定义变量,且变量只能在generate中使用 ,generate variant → genvar.

结构为:

generate

.....

endgenerate

另外,generate可以与for 、case、if等语句搭配使用,如:

第六章:结构语句、系统任务、函数语句和显示系统任务

A-结构说明语句

verilog语言中,任何模块都从属于以下4类说明语句:

1)initial语句;

2)always语句;

3)task语句;

4)function语句。

1、initial

顾名思义:initialize,初始化。初始化通常有两个作用:1)赋初始值;2)生成测试用的激励波形。

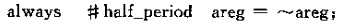

2、always

always跟着触发条件,

例如:

特别的,always @(*),则囊括所有变量。

这里遇到了wait语句:

若count_enable为0,则继续等待,直到非零,执行#20 count = count+1;

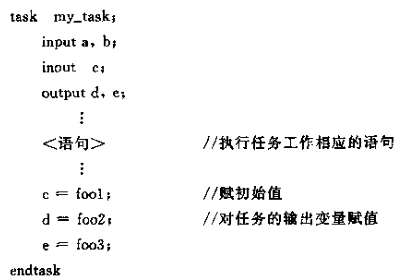

3、task

task基本用法

task调用形式:

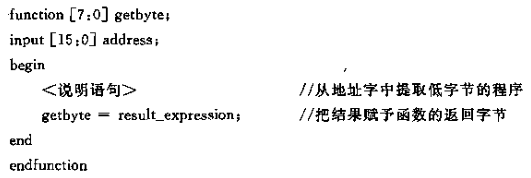

4、function

function基本用法:

调用与task类似。function细节定义较多,用到再补充。

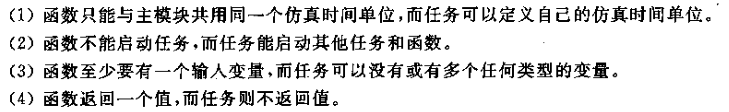

task与function的不同点:

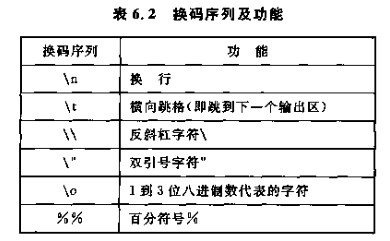

B-常用系统任务

文件读写则是fopen、fclose那一套。

常用的为$display $write。

第七章:调试用系统任务和常用编译预处理语句

A-系统任务

1、$monitor

$monitoron:开,off:关,因为可能涉及到多处的monitor,因此借助off/on进行管理。

2、$time

当前时刻,不过受时间精确度的影响:`timescale 10 ns/1 ns//用法:`timescale <时间单位>/ <时间精度>

3、$realtime

同time,返回实数型。

4、$finish

退出仿真器

5、$stop

暂停模式。

6、$random

随机数。

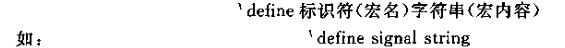

B-常用编译预处理

1、宏定义

`define

与其他语言的宏定义 类似,例如用 signal 代替 string。

也可以定义常量/表达式:

`define expression a+b+c+d

2、文件包含

`include

调用其它verilog 文件。

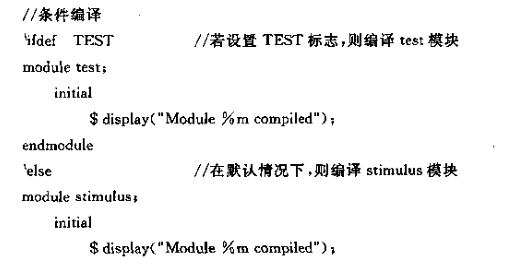

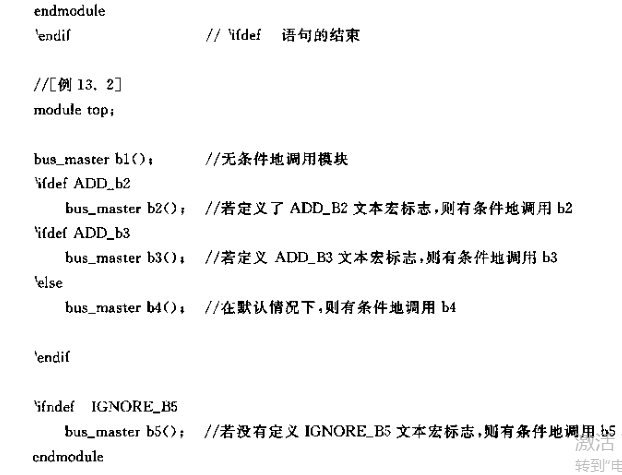

3、条件编译命令

`ifdef `else `endif

其他

- negedge:negative edge,下降沿触发,例如与always连用:always @ (negedge reset or posedge clkin)

- posedge:positive edge,上升沿触发

解释:

defparam Gen_ClkLed.divdWIDTH=23,Gen_ClkLed.divdFACTOR=10000000;//10_000_000分频

gen_divd Gen_ClkLed(.reset(Resetb),.clkin(ClkIn),.clkout(ClkLed));

涉及defparam 以及.v的调用

Verilog学习笔记的更多相关文章

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog学习笔记基本语法篇(十二)········ 编译预处理

h Verilog HDL语言和C语言一样也提供编译预处理的功能.在Verilog中为了和一般的语句相区别,这些预处理语句以符号"`"开头,注意,这个字符位于主键盘的左上角,其对应 ...

- Verilog学习笔记基本语法篇(十一)········ 常用系统函数

1)系统任务:$monitor 格式: $monitor(p1,p2,p3...pn); $monitor; $monitoron; $monitoroff; 任务$monitor提供了监控输出列 ...

- Verilog学习笔记基本语法篇(十三)...............Gate门

Verilog中已有一些建立好的逻辑门和开关的模型.在所涉及的模块中,可通过实例引用这些门与开关模型,从而对模块进行结构化的描述. 逻辑门: and (output,input,...) nand ( ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(五)...............序列检测设计

这里采用夏宇闻教授第十五章的序列检测为例来学习; 从以上的状态转换图可以写出状态机的程序: module seqdet(x,out,clk,rst); input x,clk,rst; output ...

- Verilog学习笔记设计和验证篇(五)...............层次化事件队列

详细的了解层次化事件队列有助于理解Verilog的阻塞赋值和非阻塞赋值功能.所谓层次化事件队列指的是用于调度仿真时间的不同Verilog事件队列.在IEEE的5.3节中定义了层次化事件队列在逻辑上分为 ...

- Verilog学习笔记设计和验证篇(三)...............同步有限状态机的指导原则

因为大多数的FPGA内部的触发器数目相当多,又加上独热码状态机(one hot code machine)的译码逻辑最为简单,所以在FPGA实现状态机时,往往采用独热码状态机(即每个状态只有一个寄存器 ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(一)...............D触发器

module D_flop(data,clk,clr,q,qb); input data,clk,clr; output q,qb; wire a,b,c,d,e,f,ndata,nclk; nand ...

随机推荐

- (转)初识 Lucene

Lucene 是一个基于 Java 的全文信息检索工具包,它不是一个完整的搜索应用程序,而是为你的应用程序提供索引和搜索功能.Lucene 目前是 Apache Jakarta 家族中的一个开源项目. ...

- php中对MYSQL操作之预处理技术(1)数据库dml操作语句

<?php //预处理技术 //创建一个mysqli对象 $mysqli = new MySQLi("主机名","mysqlusername"." ...

- 从Ubuntu12.04LTS到Foreda19再到Foreda8

装Ubuntu的初衷是以为它能识别我的PCI无线网卡,但装了两遍没有做到. 昨天在Ubuntu装jdk7,其过程与正常Linux安装jdk差别不小,有点背离的意思.另外VI的用法也和正常Unix/Li ...

- AutoPlay Menu Builder入门教程

1 拖动窗口可以设置主界面的窗口大小,在下面有版面预览 2 常用东西介绍.右侧的素材库除了按钮还有图像,背景,音乐等.使用按钮的时候选中需要的按钮样式,双击即可上屏.图形按钮即使可以使用图像作为背景的 ...

- Discuz常见大问题-如何自定义单个页面

比如我们先做一个最简单的网站的最后一页关于我们(插入了一幅图片,同时加入了几行文字) 先做好两个页面的文件(php页面是负责解析htm页面的,目前这两个页面都是空的) mypage_about.php ...

- PHP高级教程-JSON

PHP JSON 本章节我们将为大家介绍如何使用 PHP 语言来编码和解码 JSON 对象. 环境配置 在 php5.2.0 及以上版本已经内置 JSON 扩展. JSON 函数 函数 描述 json ...

- whereis 命令(转)

原文:http://www.cnblogs.com/peida/archive/2012/11/09/2761928.html whereis命令只能用于程序名的搜索,而且只搜索二进制文件(参数-b) ...

- Chrome 对于 glyphicon 字体图标不显示的解决的方法

在将Chome默认字体渲染为微软雅黑后,部分字体图标显示为方框,这里Chome扩展文档提供的解决的方法为: 找到 custom.css 文件,路径为: C:\Users\(username)\App ...

- Jacoco的原理(各个覆盖率的解释)

覆盖率计数器 Jacoco使用一系列的不同的计数器来做覆盖率的度量计算.所有这些计数器都是从java的class文件中获取信息,这些class文件可以(可选)包含调试的信息在里面.即使在没有源码的情况 ...

- TP自动生成模块目录

TP自动生成模块目录 例如我想在项目中增加一个AdminI模块 只需要在入口文件index.php中添加: define('BIND_MODULE','Admin'); 再访问127.0.0.1项目就 ...