verilog 常见单元描述

半加器:

//行为级建模

module half_adder2(a, b, sum, c_out);

input a, b;

output sum, c_out;

assign {c_out, sum} = a + b;

endmodule

// 结构级建模

module half_adder(a, b, sum, c_out);

input a, b;

output sum, c_out;

xor (sum, a, b);

and (c_out, a, b);

endmodule

进位选择加法器:

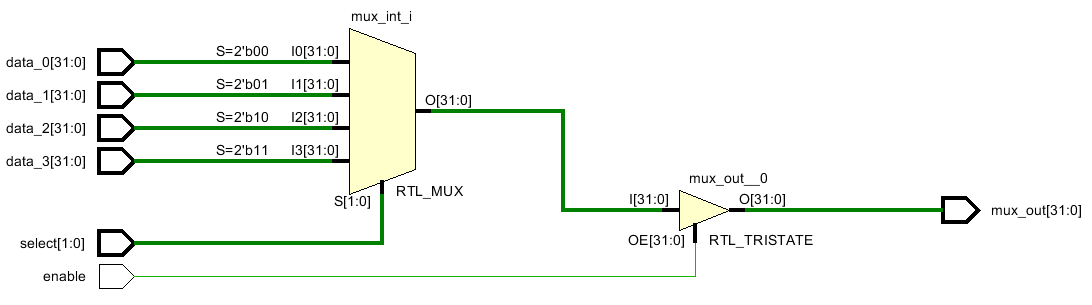

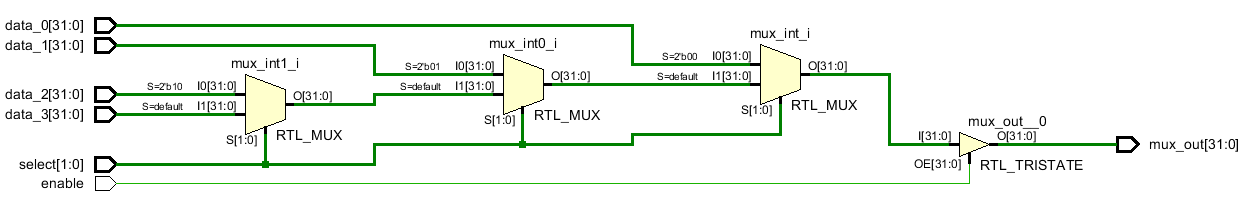

多路复用器:

//行为模型

module Mux_4_32_case(

output [:] mux_out,

input [:] data_3, data_2, data_1, data_0,

[:] select,

input enabel

);

reg [:] mux_int;

assign mux_out = enable ? mux_int : 32b'z;

always @ (data_3, data_2, data_1, data_0, select)

case (select)

: mux_int = data_0;

: mux_int = data_1;

: mux_int = data_2;

: mux_int = data_3;

default: mux_int = 32b'x; //当select包含z or x时的状态,不加default vivado综合出来的电路图没有区别,但是不知道在tb上会不会出问题

endcase

endmodule

//使用if条件语句行为级建模

module Mux_4_32_if(

output [:] mux_out,

input [:] data_3, data_2, data_1, data_0,

input [:] select,

input enable

);

reg [:] mux_int;

assign mux_out = enable ? mux_int : 'bz;

always @(data_3, data_2, data_1, data_0, select)

if(select == 'b00) mux_int = data_0; else

if(select == 'b01) mux_int = data_1; else

if(select == 'b10) mux_int = data_2; else

if(select == 'b11) mux_int = data_3; else

mux_int = 'bx;

endmodule

module Mux_4_32_CA(

output [:] mux_out,

input [:] data_3, data_2, data_1, data_0,

input [:] select,

input enable

);

wire [:] mux_int;

assign mux_out = enable ? mux_int : 'bz;

assign mux_int = (select==) ? data_0:

(select==) ? data_1:

(select==) ? data_2:

(select==) ? data_3: 'bx;

endmodule

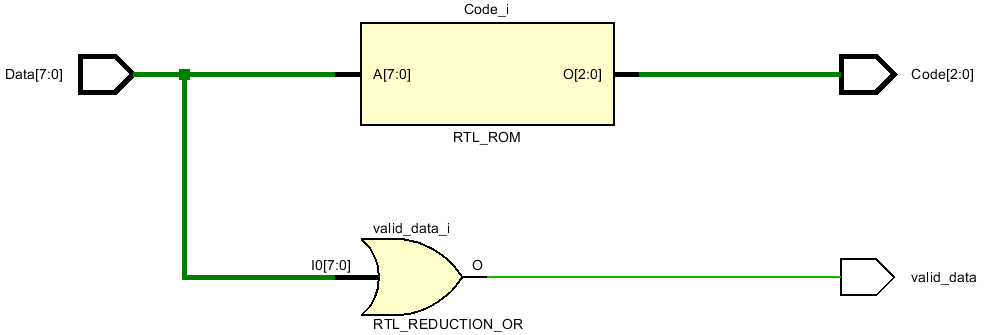

编码器

//case 优先编码器

module priority_case(

output reg [:] Code,

output valid_data,

input [:] Data

);

assign valid_data = |Data; //“reduction or" operator

always @(Data)

casex (Data)

'b1xxxxxxx : Code = 7;

'b01xxxxxx : Code = 6;

'b001xxxxx : Code = 5;

'b0001xxxx : Code = 4;

'b00001xxx : Code = 3;

'b000001xx : Code = 2;

'b0000001x : Code = 1;

'b00000001 : Code = 0;

default : Code = 'bx;

endcase

endmodul

verilog 常见单元描述的更多相关文章

- Quartus II 中 Verilog 常见警告/错误汇总

Verilog 常见错误汇总 1.Found clock-sensitive change during active clock edge at time <time> on regis ...

- No.2 Verilog 模块和描述风格

2-1 模块 Verilog语言基本的描述单元----模块,模块是用来描述某个设计的功能或结构,以及它与其它外部模块进行通信的端口. module module_name(port_list); De ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- spring中常见注解描述

@Qualifier如果一个接口类有多个实现类,那么可以用@Qualifier指定使用哪个实现类: /** * 定时器,用于处理超时的挂起请求,也用于连接断开时的重连. */ @Autowired @ ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- Verilog的数据流、行为、结构化与RTL级描述

Verilog语言可以有多种方式来描述硬件,同时,使用这些描述方式,又可以在多个抽象层次上设计硬件,这是Verilog语言的重要特征. 在Verilog语言中,有以下3种最基本的描述方式: 数据流描述 ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- python描述符理解

Python中的描述符是一个相对底层的概念 descriptor Any object which defines the methods get(), set(), or delete(). Whe ...

- Verilog HDL模型的不同抽象级别

所谓不同的抽象类别,实际上是指同一个物理电路,可以在不同层次上用Verilog语言来描述.如果只从行为功能的角度来描述某一电路模块,就称作行为模块.如果从电路结构的角度来描述该电路模块,就称作结构模块 ...

随机推荐

- go语言设计模式之Flyweight(享元模式)

flyweight.go package flyweight import ( "time" ) const ( TEAM_A = "A" TEAB_B = & ...

- 【转】bootstrap table轻松实现数据表格

在使用bootstrap table时可能在很多时候回用的表格来显示数据,如果自己写那肯定没问题,但是数据展示出来就麻烦多了,然而bootstrap table 封装了一套完善的数据表格组件,把从后台 ...

- autocad2014一直显示正在检查许可

64位CAD2014安装成功后启动时在检查许可卡住的解决方法,以下方法经本人测试,真实可行.1.下载CCcleaner.2.将CCcleaner设置成中文版,英文好的继续第三步.(设置方法:选项opt ...

- 解决谷歌浏览器在F12情况下自动断点问题(Paused in debugger)

解决谷歌浏览器在F12情况下自动断点问题(Paused in debugger) 最近在使用谷歌浏览器在调试js脚本的时候,每次按F12,再刷新页面,都会跳出如上图所示的图标,自动进入断点调试.如果不 ...

- Windows下同时安装python2和python3如何兼容版本

引言:因学习需要把python2和python3都安装了,为了避免使用过程中混淆版本在网上找了一些解决方案,亲测可用.方法如下: 分别下载并安装Python2.x和Python3.x. 配置环境变量. ...

- 【2019.8.20 NOIP模拟赛 T2】小B的树(tree)(树形DP)

树形\(DP\) 考虑设\(f_{i,j,k}\)表示在\(i\)的子树内,从\(i\)向下的最长链长度为\(j\),\(i\)子树内直径长度为\(k\)的概率. 然后我们就能发现这个东西直接转移是几 ...

- wepy安装后提示Cannot read property 'addDeps'

最近准备做一个微信小程序,以前一直用的小程序原始api做,但是这次准备用一个框架来做练习,当然在做之前需要比较一下现在小程序框架的优缺点. 经过认真挑选,选定wepy,Taro,uni-app,mpv ...

- 大话设计模式Python实现-中介者模式

中介者模式(Mediator Pattern):用一个对象来封装一系列的对象交互,中介者使各对象不需要显示地相互引用,从而使耦合松散,而且可以独立地改变它们之间的交互. 下面是一个中介者模式的demo ...

- Octave Convolution详解

前言 Octave Convolution来自于这篇论文<Drop an Octave: Reducing Spatial Redundancy in Convolutional Neural ...

- Spring Cloud Gateway-自定义异常处理

前提 我们平时在用SpringMVC的时候,只要是经过DispatcherServlet处理的请求,可以通过@ControllerAdvice和@ExceptionHandler自定义不同类型异常的处 ...