FPGA 状态机-序列检测器verilog

实现功能:检测出串行输入数据4位Data二进制序列0101,当检测到该序列的时候,out=1,否则out=0

(1)给出状态编码,画出状态图

(2)门电路实现

(3)verilog实现

首先规定Q3Q2Q1为刚输入的三位数,接下来要输入的数是A,Z为输入A以后的状态机的输出结果,则可以画出状态转换图如下:

然后根据状态图,我们可以得到状态表:

从而推导出激励方程,根据卡诺图化简得到序列检测的门级检测电路如下:

(3)根据状态图写出verilog代码:

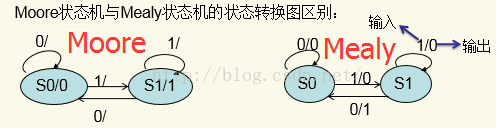

mealy型状态机的输出与其输入以及当前状态有关:

module xuliejiance(input clk,rst,q

output out);

reg [:]state,nexts;

parameter s1='d0,

s2='d1,s3=3'd2,s4='d3,s5=3'd4,

s6='d5,s7=3'd6,s8='d7; always@(posedge clk ir negedge rst)

begin

if(~rst)

state<='d0;

else

state<=nextstate;

end always@(q,state)

case(state)

:if(q==)

nextstate='d1;

else

nextstate='d0;

:if(q==)

nextstate='d3;

else

nextstate='d2;

:if(q==)

nextstate='d5;

else

nextstate='d4;

:if(q==)

nextstate='d5;

else

nextstate='d6;

:if(q==)

nextstate='d0;

else

nextstate='d1;

:if(q==)

nextstate='d0;

else

nextstate='d3;

:if(q==)

nextstate='d0;

else

nextstate='d4;

:if(q==)

nextstate='d7;

else

nextstate='d6;

default:

nextstate<='d0;

endcase

assign out=(state==3'd2)&&(x==0);

endmodule

moore型状态机的输出只与其当前状态有关:

module xuliejiance(

input clk,rst,q,

output out);

reg [:] state,nextstate;

parameter s0='d0,s1=3'd1,s2='d2,s3=3'd3,s4='d4;

always @(posedge clk or negedge rst)

begin

if(~rst)

state<='d0;

else

state<=nextstate;

end always@(*)

begin

case(state)

s0:

begin

if(q==)

nextstate=s1;

else

nextstate=s0;

end

s1:

begin

if(q==)

nextstate=s2;

else

nextstate=s0;

end

s2:

begin

if(q==)

nextstate=s2;

else

nextstate=s3;

end

s3:

begin

if(q==)

nextstate=s4;

else

nextstate=s0;

end

s4:

begin

if(q==)

nextstate=s0;

else

nextstate=s1;

end end

assign out=(state==s4)?1:0;

endmodule

以上写的都是两段式的状态机的实现,此外我们可以用更加正式的三段式的状态机实现

以下是一个可以用与参考的状态机的东西:

我们以1101序列检测器为例:

1101序列检测器Mealy状态机状态转移图

1101序列检测器Moore状态机状态转移图

我们以Mealy状态机为例

一段式状态机(部分核心代码):

两段式状态机(部分核心代码):

三段式状态机(部分核心代码):

FPGA 状态机-序列检测器verilog的更多相关文章

- 基于FPGA的序列检测器10010

最近在学习状态机,用状态机实现序列检测器10010. 思路如下: 1. S0代表当前数据0,如果检测到0就停在S0,如果检测到1就进入S1. 2. S1代表当前数据1,如果检测到0就进入S2,如果检测 ...

- 10010序列检测器的三段式状态机实现(verilog)

序列检测器是时序数字电路设计中经典的教学范例,夏宇闻的<verilog数字系统设计教程>一书中有这个例子,用verilog设计一个“10010”序列的检测器.看完后我觉得F和G两个状态多余 ...

- 每天进步一点点------基础实验_12_有限状态机 :Moore型序列检测器

/********************************************************************************* * Company : * Eng ...

- 每天进步一点点------基础实验_13_有限状态机 :Mealy型序列检测器

/********************************************************************************* * Company : * Eng ...

- fpga 状态机 检测1011序列

1011 可以使用4个状态:s0,s1,s2,s3. 即:(1)s0有0或1两个状态,当s0位0时,进入s0状态,自身打圈.为1那么进入下个状态s1来检测0. (2)s1有0或1两种情况,s1为1时s ...

- i2c状态机方法设计-verilog

2010-09-05 21:04:00 verilog语言基础学的差不多了.接着就是看看华为的语言编写规范.状态机设计方法是fpga的重要设计方法.所以我要记上一笔. 只要会FSM方法,用fpga编写 ...

- lattice diamond fpga 状态机的理解

比如序列检测101,需要三个状态 :so,s1,s2. 思路:(1)s0状态有两种情况0或1,若为0时在自身打圈,是1时进入s1状态. (2)s1状态有两种0或1,若为1自身打圈,因为1可以作为下次检 ...

- 【FPGA篇章四】FPGA状态机:三段式以及书写方法

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章 状态机是fpga设计中极其重要的一种技巧,状态机通过不同的状态迁移来完成特定的逻辑操作,掌握状态机的写法可以使fpga的开发事半功倍. 状态 ...

- FPGA 状态机设计

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy状态机. Moore状态机 其最大特点是输出只由当前状态确定,与输入无关.Moore状态机的 ...

随机推荐

- 使用js检测页面是在electron app中运行还是在浏览器中运行

<script type="text/javascript"> var userAgent = navigator.userAgent.toLowerCase() ){ ...

- 201771010123汪慧和《面向对象程序设计Java》第十二周实验总结

一.理论部分 1.在Java提供的GUI构建工具中可以分为组件和容器两类. 2.在Java中的组件有:按钮.标签.复选框.单选按钮.选择框.列表框.文本框.滚动条.画布.菜单. 3.在Java中的容器 ...

- 判断苹果和安卓端或者wp端

window.onload = function() { var u = navigator.userAgent; if(u.indexOf('Android') > -1 || u.index ...

- JAVA中汉字的Compare排序

当调用String.compare方法的时候,比较的是Unicode码,并不能对汉字进行准确的排序,所以汉字比较时会出现比较混乱的结果. java.text.Collator类中有一个getInsta ...

- 18 12 18 给服务器添加logging 日志功能

Python中有个logging模块可以完成相关信息的记录,在debug时用它往往事半功倍 1. 日志级别 日志一共分成5个等级,从低到高分别是: DEBUG INFO WARNING ERROR C ...

- JS-语句三

关于if语句的几个练习: 1. 输入三个整数,x,y,z,最终以从小到大的方式输出. 思路:先列举出每种可能,然后做if套嵌. var x = prompt("请输入一个数字 ...

- Java8集合框架——集合工具类Arrays内部方法浅析

java.util.Arrays 备注:本文只对 Java8 中的 java.util.Arrays 中提供的基本功能进行大致介绍,并没有对其具体的实现原理进行深入的探讨和分析.详情可自己深入观摩源码 ...

- 小白需要了解的Ajax和websocket的区别以及使用场景!

在我们日常使用的互联网产品中,很多都是前后端数据的交互来完成的,说到数据交互就不得不提Ajax和websocket,它们可是数据交互的利器,那么它们分别是什么?websocket与Ajax轮询的区别又 ...

- 吴裕雄--天生自然 JAVASCRIPT开发学习: JSON

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <title> ...

- Android前后台切换的监听

本文参考这位哥们:https://juejin.im/post/5b87f409e51d4538b0640f58 首先写两个类文件ActivityLifecycleCallbacksAdapter.L ...