Fast-settling synchronous-PWM-DAC filter has almost no ripple

An inexpensive way to implement high-resolution digital-to-analog conversion is to combine microcontroller-PWM (pulse-width-modulated) outputs with precision analog-voltage references, CMOS switches, and analog filtering (Reference 1). However, PWM-DAC design presents a big design problem: How do you adequately suppress the large ac-ripple component inevitably present in the switch’s outputs? The ripple problem becomes especially severe when you use typical 16-bit microcontroller-PWM peripherals for DAC control; such high-resolution PWM functions usually have long cycles because of the large 216 countdown modulus of 16-bit timers and comparators. This situation results in ac-frequency components as inconveniently slow as 100 or 200 Hz. With such low ripple frequencies, if you employ enough ordinary analog lowpass filtering to suppress ripple to 16-bit—that is, –96-dB—noise levels, DAC settling can become a full second or more.

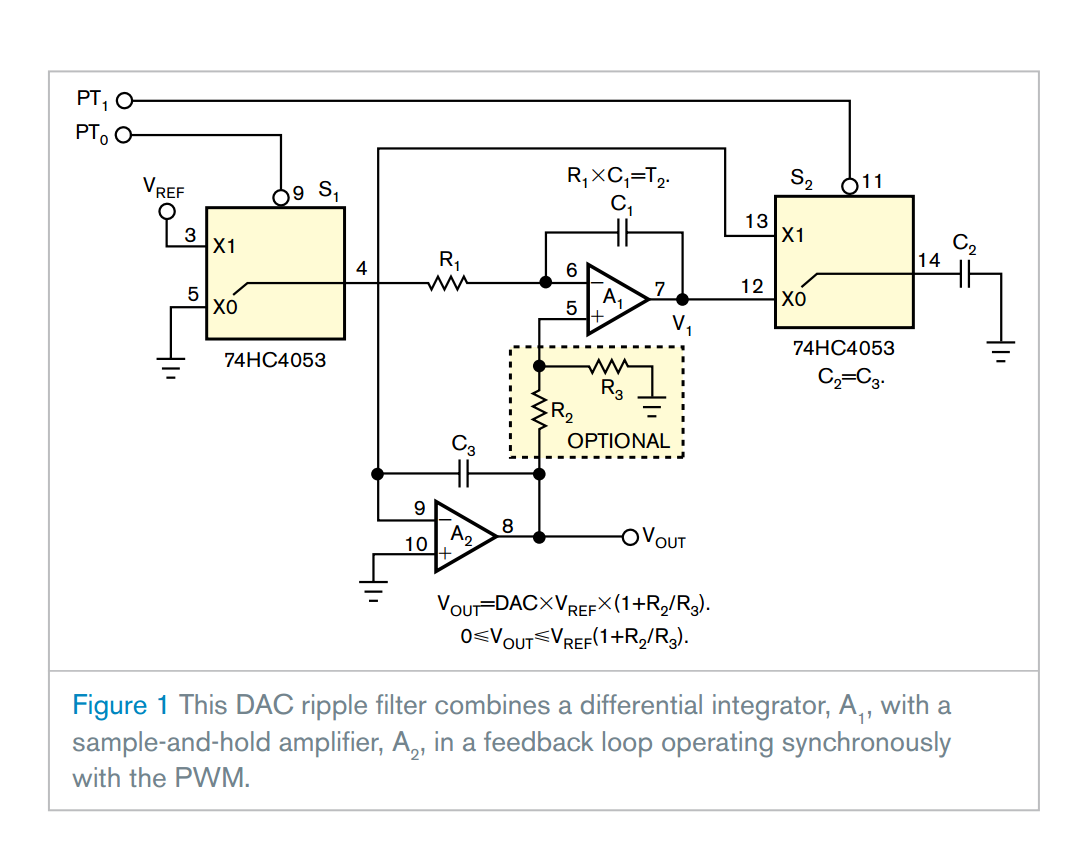

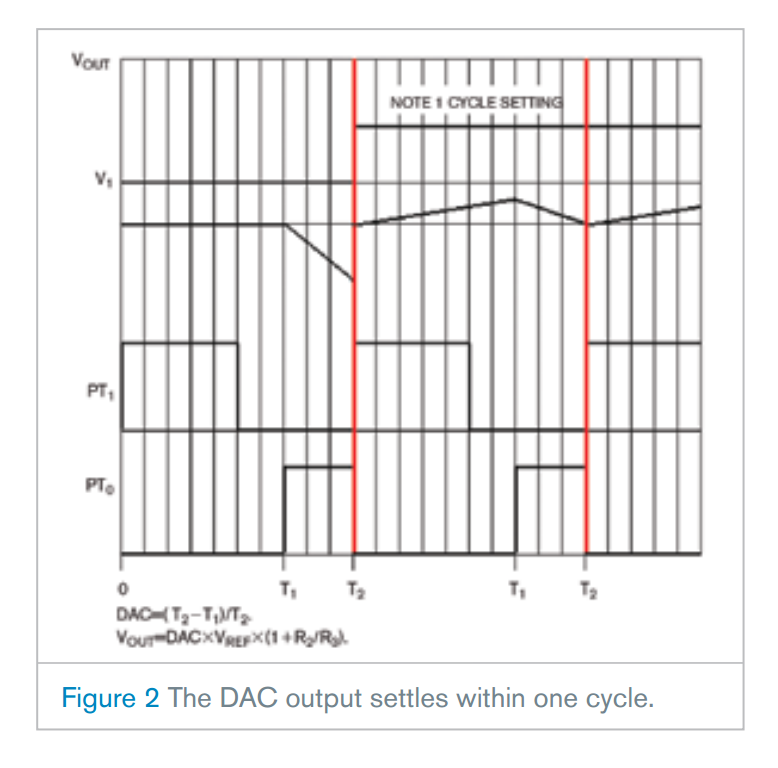

The circuit in Figure 1 avoids most of the problems of lowpass filtering by combining a differential integrator, A1, with a sample-and-hold amplifier, A2, in a feedback loop operating synchronously with the PWM cycle, T2 in Figure 2. If you make the integrator time constant equal to the PWM cycle time—that is, R1×C1=T2—and, if the sample capacitor, C2, is equal to the hold capacitor, C3, then the filter can acquire and settle to a new DAC value in exactly one PWM-cycle time. Although this approach hardly makes the resulting DAC exactly “high speed,” 0.01-sec settling is still 100 times better than 1-second settling. Just as important as speed, this improvement in settling time comes without compromising ripple attenuation. Ripple suppression of the synchronous filter is, in theory, infinite, and the only limit in practice is nonzero-charge injection from S2 into C3. The choice of a low-injected-charge switch for S2 and an approximately 1-µF capacitance for C3 can easily result in ripple amplitudes of microvolts.

Optional feedback-voltage divider R2/R3 provides flexibility in a DAC-output span with common voltage references. For example, if R2=R3, then a 0 to 10V output span will result from a 5V reference. An additional advantage of this method of span adjustment is that output ripple remains independent of reference amplification.

Fast-settling synchronous-PWM-DAC filter has almost no ripple的更多相关文章

- PWM DAC Low Pass Filtering

[TI博客大赛][原创]LM3S811之基于PWM的DAC http://bbs.ednchina.com/BLOG_ARTICLE_3005301.HTM http://www.fpga4fun.c ...

- PWM DAC vs. Standalone

http://analogtalk.com/?p=534 http://analogtalk.com/?p=551 Posted by AnalogAdvocate on April 09, 2010 ...

- 【STM32】PWM DAC基本原理(实验:PWM实现DAC)

虽然STM32F103ZET6具有内部DAC,但是也仅仅只有两条DAC通道,并且STM32还有其他的很多型号是没有DAC的.通常情况下,采用专用的D/A芯片来实现,但是这样就会带来成本的增加. 不过S ...

- How determine the RC time constant in PWM DAC low-pass filter?

how determine the RC time constant in PWM digital to analog low-pass filter? I 'm looking for the be ...

- MCU PWM DAC OP Voltage Output

- Make a DAC with a microcontroller's PWM timer

http://www.edn.com/design/analog/4337128/Make-a-DAC-with-a-microcontroller-s-PWM-timer Many embedded ...

- how to generate an analog output from a in-built pwm of Atmega 32AVR microcontrloller?

how to generate an analog output from a in-built pwm of Atmega 32AVR microcontrloller? you need a re ...

- The Secret Mixed-Signal Life of PWM Peripherals

The Secret Mixed-Signal Life of PWM Peripherals Pulse-width modulation (PWM) peripherals have enjoye ...

- PEM DAC note

开发指南V1.0库函数版本,PWM DAC实验 350页 STM32 的定时器最快的计数频率是72Mhz,8 为分辨率的时候,PWM 频率为72M/256=281.25Khz.如果是1阶RC滤波,则要 ...

随机推荐

- Petrozavodsk Winter Training Camp 2018

Petrozavodsk Winter Training Camp 2018 Problem A. Mines 题目描述:有\(n\)个炸弹放在\(x\)轴上,第\(i\)个位置为\(p_i\),爆炸 ...

- MYSQL三种安装方式--rpm包安装

1. 首先检查机器里是否已经存在MySQL $ rpm -qa | grep mysql 2. 去官网下载相应的rpm包:https://dev.mysql.com/downloads/mysql/ ...

- go语言入门(一)

环境安装 Go 语言支持以下系统: Linux FreeBSD Mac OS X(也称为 Darwin) Window 安装包下载地址为:https://golang.org/dl/. Windows ...

- [ python ] 字符串的操作及作业题

字符串的操作方法 capitalize() : 首字母大写 s1 = 'my heart will go on' print(s1.capitalize()) # 首字母大写 # 执行结果: # My ...

- Redis 常见面试题

使用Redis有哪些好处? 速度快 基于内存,避免了磁盘I/O的瓶颈. 单进程单线程,减少了线程上下文切换的开销 利用队列技术将并行访问变为串行访问,消除了传统数据库并发访问控制锁的开销. Redis ...

- Java学习(基本语句,语法,变量)

一.基本语法: public class Demo { //定义一个类 public static void main(String[] args) { //主方法,一切程序的起点 /* 在屏幕上打印 ...

- c++ 容器学习 理论

[转载]http://blog.csdn.net/acosoft/article/details/4395468 在面向对象的语言中,大多引入了容器的概念.那么 什么 是 容器?实质上就是一组相同类型 ...

- merc_timer_handle_t函数的使用

merc_timer_handle_t,是定义一个时间类型,这个时间类型可以用来接收2个函数之间的wasted time 但是在项目中出现这个情况: 因为在脚本中添加了该函数:

- poj1915 Knight Moves(BFS)

题目链接 http://poj.org/problem?id=1915 题意 输入正方形棋盘的边长.起点和终点的位置,给定棋子的走法,输出最少经过多少步可以从起点走到终点. 思路 经典bfs题目. 代 ...

- java浅拷贝和深拷贝(基础也是很重要的)

对象的copy你兴许只是懵懂,或者是并没在意,来了解下吧. 对于的github基础代码https://github.com/chywx/JavaSE 最近学习c++,跟java很是相像,在慕课网学习c ...