使用Vivado的block design

使用Vivado的block design

(1)调用ZYNQ7 Processing System

(2)配置ZYNQ7系统

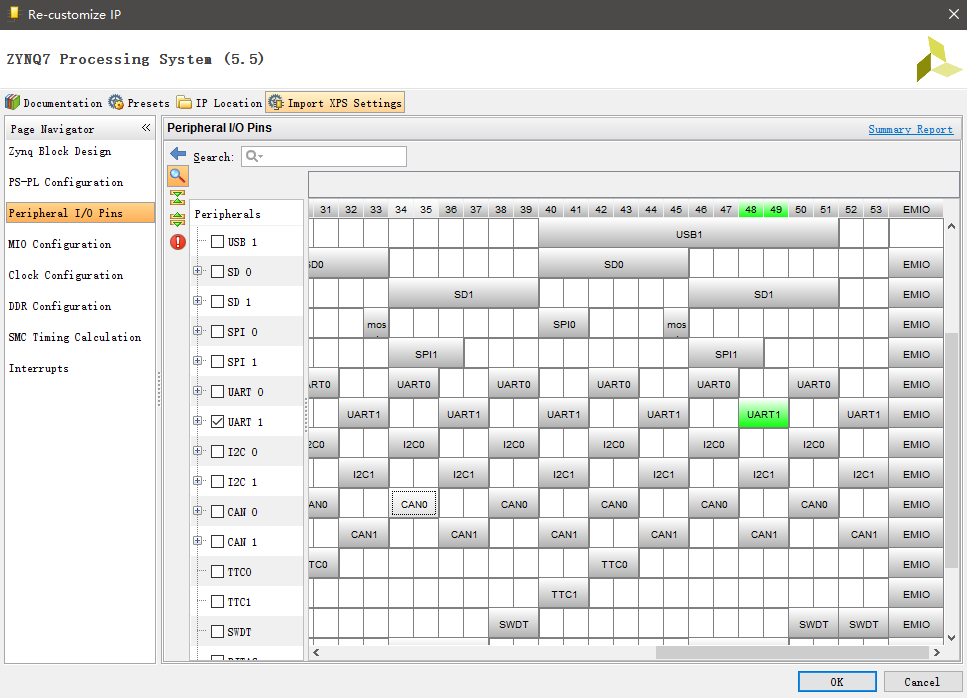

(3)外设端口配置

根据开发板原理图MIO48和MIO49配置成了串口通信。

(4)串口波特率的配置

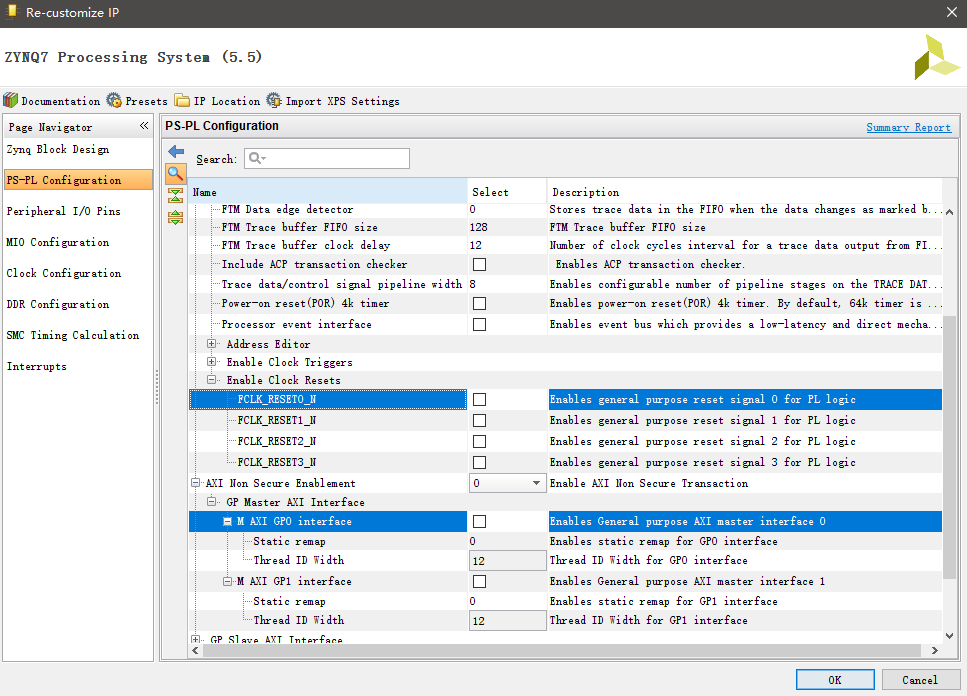

(5)关于AXI总线的配置

(6)时钟配置界面

这里可以配置ZYNQ系统输入时钟,CPU的工作时钟,DDR工作时钟,还有其他外设的工作时钟。

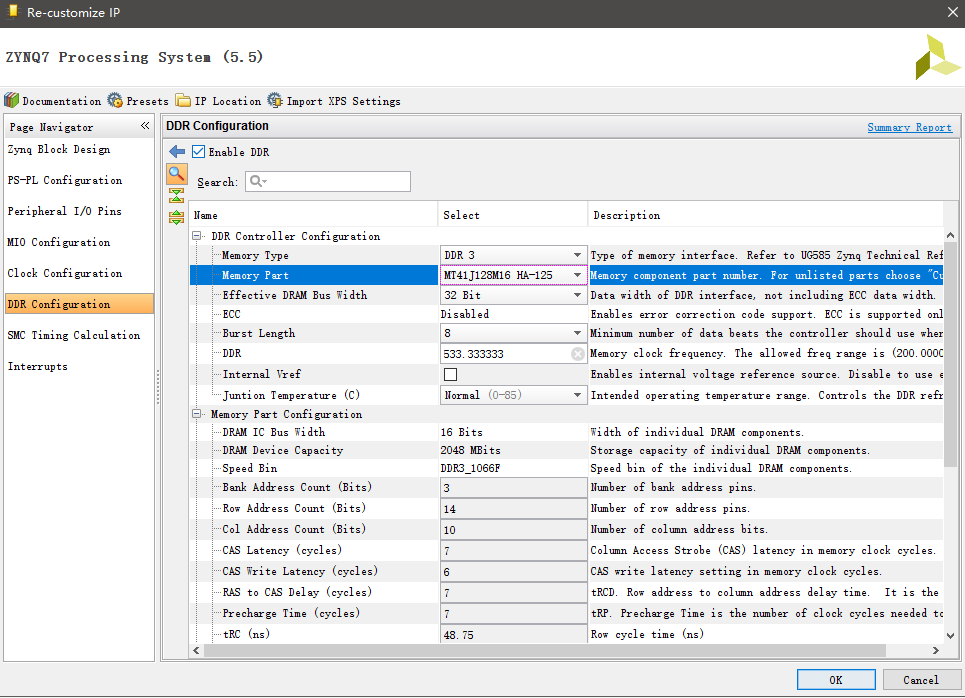

(7)DDR的配置

重点在于选择DDR的信号,其他参数会自适应。

(8)Run Block Automation完成对ZYNQ7 Processing System IP核的配置

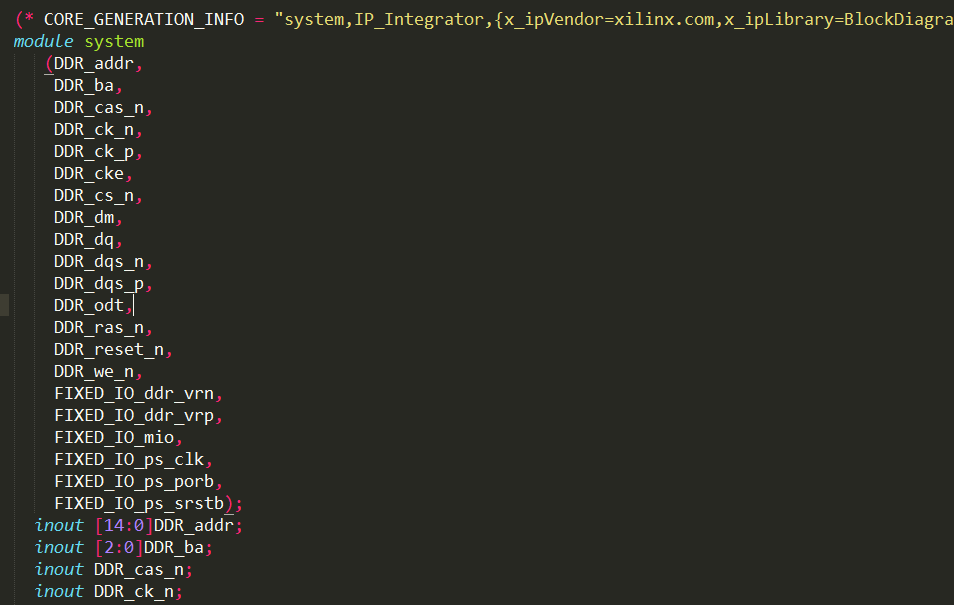

运行完Run Block Automation之后,会生成ZYNQ系统外部管脚,如下图:一个是DDR接口,一个是FIXED_IO接口。

(9)Generate Output Products

此步骤是用来生成Diagram Block Design的HDL源文件以及相应端口的约束文件。

生成的system.v文件内容如下图所示,其实就是这个block design的顶层文件:

(10)生成整个工程的顶层文件

生成结果为:

注意:如果系统只使用了PS部分的资源,没有使用PL部分的资源,则不需要再vivado下编译和生成bit文件了。

(11)硬件导入SDK

File ->Export->Export Hardware..

(12)启动SDK开发环境

File->Launch SDK

(13)SDK软件编程

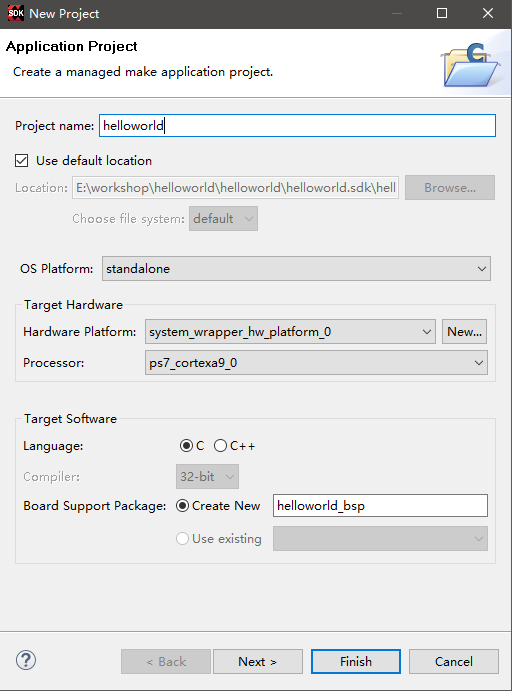

File->New->Application Project,即新建一个SDK的软件工程。

选择工程模板Hello World

新建的Hello World工程

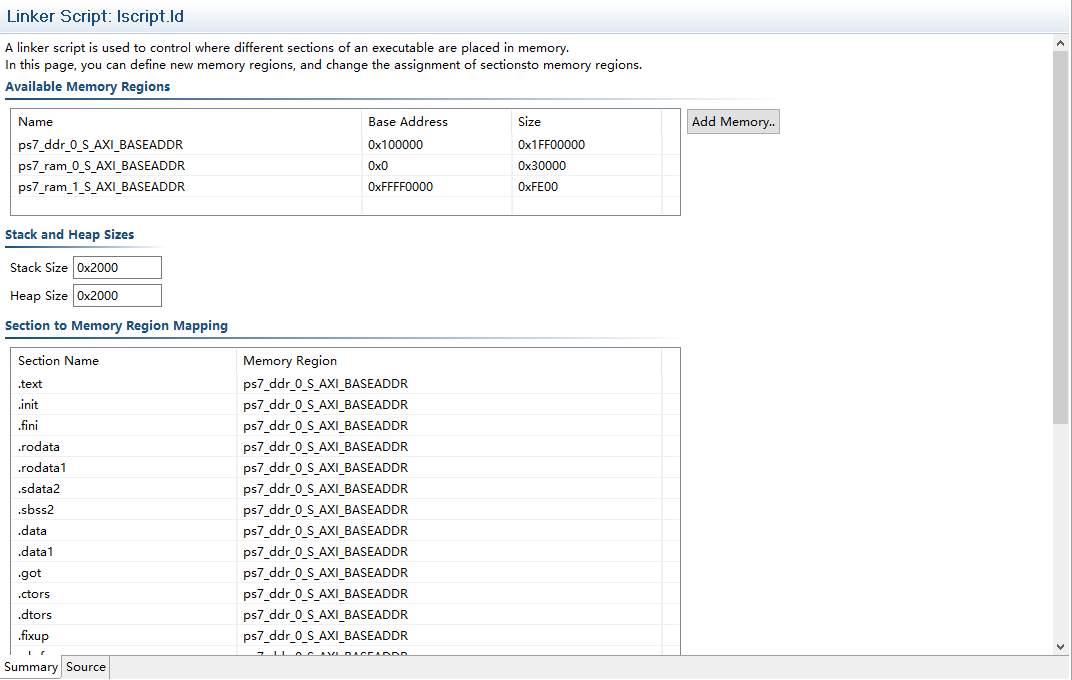

其中工程里面的lscript.ld文件是用来定义程序或者数据是在内部的RAM还是外部的DDR里面。

(14)编译软件程序

Build Project

使用Vivado的block design的更多相关文章

- Vivado中备份设计好的block design

参考链接 https://blog.csdn.net/dimples_song/article/details/81391615 前言 为了不每次都重新生成block design,避免重复劳动. 可 ...

- ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言 在Block design中引出AXI接口给外部,检查设计告警如下: [BD 41-968] AXI interface port /axi_lite4 is not associated to ...

- Block Design 小技巧之添加RTL代码到block_design

Block Design 小技巧之添加RTL代码到block_design 1.首先得打开Block Design,右击RTL文件,才会出现Add module to Block Design选项. ...

- ZYNQ Block Design中总线位宽的截取与合并操作

前言 在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作. 在verilog下,截位操作可如下所示: wire [7:0] w_in; wire ...

- 方差分析|残差|MSA/MSE|Completely randomized design|Randomized block design|LSD|主效应|intercept|多重比较|

符合方差分析的三个条件: 残差=实际值-预测值(其实是均值). 在原假设下,MSA的期望会等于MSE的期望:在备选假设下,MSA的期望会大于MSE的期望,所以MSA/MSE的取值范围在(1,正无穷), ...

- Vivado_MicroBlaze_问题及解决方法_汇总(不定时更新)

Vivado_MicroBlaze_问题及解决方法_汇总(不定时更新) 标签: Vivado 2015-07-03 14:35 4453人阅读 评论(0) 收藏 举报 分类: 硬件(14) 版权声 ...

- [转载]Vivado轻松实现IP封装

Vivado轻松实现IP封装 1.新建一个测试工程 工程化的设计方法是离不开工程的,第一步往往都是新建工程,后面我会学习去工程化的开发方法,可能会更加高效. 2.利用向导完成IP封装 2.1.启动IP ...

- Vivado的helloword计划(一个):硬件project部分

硬件平台:ZedBoard 软件平台:vivado2013.3 本演示样例通过综合.实现,生成比特流,发送到SDK实现. 启动vivado而且创建一个项目 依据提示操作一步步创建新项目的时候记得选择R ...

- Zedboard(二)使用Vivado+SDK开发嵌入式应用程序——实例一

本次介绍用Vivado构建Zedboard开发板的硬件平台+SDK开发应用程序(Zedboard裸机开发) 过程如下: 一.运行Vivado,建立新工程 指定好工程路径,下一步,选择RTL Proje ...

随机推荐

- jQuery中$的三种关系

要搞清楚$('div','li') 和 $('div , li') 和 $('div li') 区别 $('div','li')是$(子,父),是从父节点里找子,而不是找li外面的div $('div ...

- python3:利用SMTP协议发送QQ邮件+附件

转载请表明出处:https://www.cnblogs.com/shapeL/p/9115887.html 1.发送QQ邮件,首先必须知道QQ邮箱的SMTP服务器 http://service.mai ...

- 【转载】 DeepMind用ReinforcementLearning玩游戏

原文地址: https://blog.csdn.net/wishchin/article/details/42425145 原文 : http://dataunion.org/?p=639 1.引言 ...

- Kafka高可用实现原理

数据存储格式 Kafka的高可靠性的保障来源于其健壮的副本(replication)策略.一个Topic可以分成多个Partition,而一个Partition物理上由多个Segment组成. Seg ...

- P1373 小a和uim之大逃离(动态规划)

题目链接:传送门 题目大意: 一个N行M列的矩阵,从任意点开始往右或者往下走,每走一格获得所到达的格子的分数. 要求总步数必须为偶数.问有多少种走法,使得奇数步得到的总分和偶数步得到的总分对K+1取模 ...

- 给Linux服务器设置共享文件目录

通过samba软件 :yum install samba 修改配置文件:vi /etc/samba/smb.conf 添加 [WORKSPACE] comment = workspace ...

- CUDA学习

CUDA(Compute Unified Device Architecture,统一计算架构)是由NVIDIA所推出的一种集成技术,是该公司对于GPGPU的正式名称.通过这个技术,用户可利用NVID ...

- EasyUI datagrid 一个可以 直接运行例子一个文件 六

<!DOCTYPE html> <html> <head> <meta charset="utf-8" /> <meta ht ...

- hdu3642 Get The Treasury 线段树--扫描线

Jack knows that there is a great underground treasury in a secret region. And he has a special devic ...

- LOJ2135 「ZJOI2015」幻想乡战略游戏

题意 题目描述 傲娇少女幽香正在玩一个非常有趣的战略类游戏,本来这个游戏的地图其实还不算太大,幽香还能管得过来,但是不知道为什么现在的网游厂商把游戏的地图越做越大,以至于幽香一眼根本看不过来,更别说和 ...