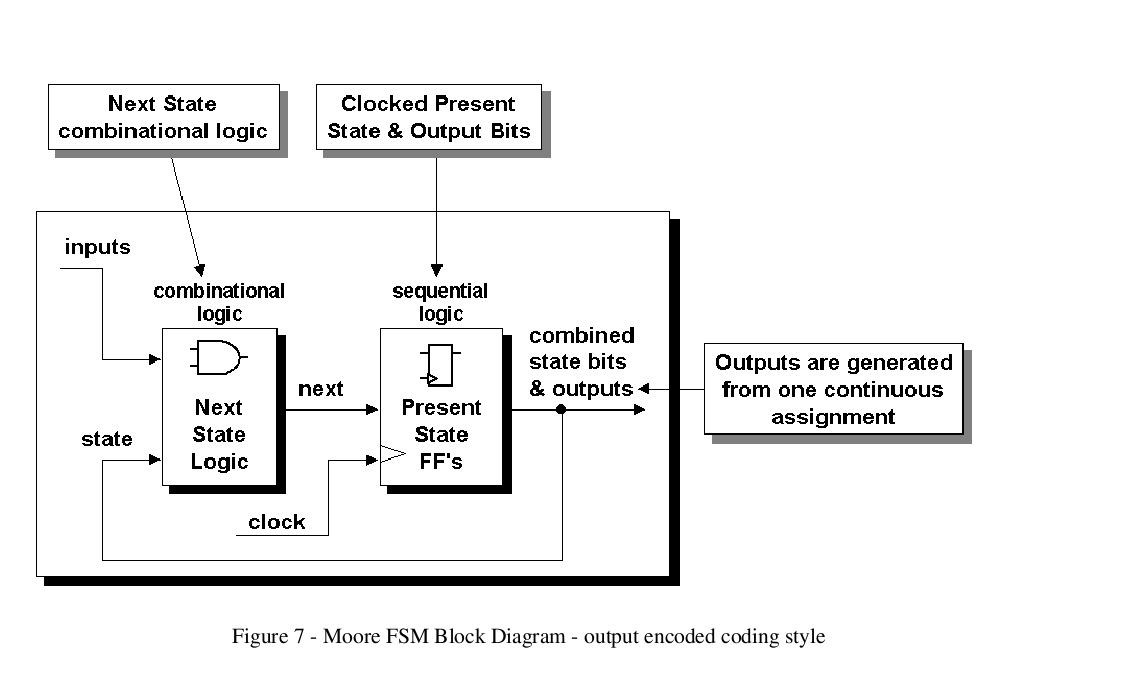

paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之output encoded style with registered outputs(Good style)

把输出跟状态编码结合起来,即使可以省面积又是寄存器输出。但是没有讲解如何实现这种高效的编码。

paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之output encoded style with registered outputs(Good style)的更多相关文章

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(index-parameter style with registered outputs)

case语句中,对于state/next 矢量仅仅做了1-bit比较. parameter 值不是表示FSM的状态编码,而是表示state/next变量的索引.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm summary

主要是1.不要用1段式写FSM 2.不要用状态编码写one-hot FSM ,要用索引编码写one-hot FSM.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之全0/1/z/x的SV写法

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之enhanced coding styles

1.ANSI style 的代码比较紧凑. 下面规范推荐,比较好. 下面是带有parameter的module header的完整规范 一般1bit ,大家都是wire signal1 = gen_s ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm1各种style的timing/area比较

整体说,一般还是用2段式,再加上output encodecd/default -X技巧.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(encoded-parameter style with registered outputs不推荐但是经常有人写这样的代码)

这样写法,不利与综合,case语句中比较也是full-vector比较.

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(二段式)

1.Two always block style with combinational outputs(Good Style) 对应的代码如下: 2段式总结: (1)the combinational ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 FSM Coding Goals

1.the fsm coding style should be easily modifiable to change state encoding and FSM styles. FSM 的的 状 ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(三段式)

Three always block style with registered outputs(Good style)

随机推荐

- CoreCLR源码2

CoreCLR源码 前一篇我们看到了CoreCLR中对Object的定义,这一篇我们将会看CoreCLR中对new的定义和处理new对于.Net程序员们来说同样是耳熟能详的关键词,我们每天都会用到ne ...

- java Integer

Java 中的数据类型分为基本数据类型和引用数据类型 int是基本数据类型,Integer是引用数据类型: Ingeter是int的包装类,int的初值为0,Ingeter的初值为null. 初始化 ...

- LinkedList源码及原理

简介 内部结构分析 LinkedList源码分析 构造方法 添加(add)方法 根据位置取数据的方法 根据对象得到索引的方法 检查链表是否包含某对象的方法: 删除(remove/pop)方法 Link ...

- 在MasterPage中检验session是否存在~

在母板頁中檢查user是否登入過,這樣就不用在每個頁中去作檢驗.在其Init事件中寫入如下代碼: protected void ContentPlaceHolder1_Init(object ...

- 实例练习——轮播图 & 全选/全不选

1 实例1:轮播图 1)实质就是改变图片的src 2)把图片的路径用数组存起来 3) “下一张”的实现就是改变数组的下标,用一个变量i控制,每次点击下标加1.“上一张”的实现正好相反.注意“i的变化” ...

- vue2.0:(九)、外卖App弹窗部分星星评分

本篇是星星评分部分,先上代码: 1.header.vue: <template> <transition name="fade"> & ...

- Mysql中WHERE IN,UNION 用法详解

WHERE IN 用法 这里分两种情况来介绍 1.in 后面是记录集,如: select * from table where uname in(select uname from ...

- JavaScript笔记2

1.浮点数在运算过程中会产生误差,因为计算机无法精确表示无限循环小数. 要比较两个浮点数是否相等,只能计算它们之差的绝对值,看是否小于某个阈值(某个可接受的范围):Math.abs(1 / 3 - ( ...

- python+selenium之验证码的处理

对于web应用来说,大部分的系统在用户登录时都要求用户输入验证码.验证码的类型很多,有字母数字的,有汉字的.甚至还有需要用户输入一道算术题的答案的.对于系统来说,使用验证码可以有效地防止采用机器猜测方 ...

- 洛谷 P3353 在你窗外闪耀的星星

题目描述 飞逝的的时光不会模糊我对你的记忆.难以相信从我第一次见到你以来已经过去了3年.我仍然还生动地记得,3年前,在美丽的集美中学,从我看到你微笑着走出教室,你将头向后仰,柔和的晚霞照耀着你玫瑰色的 ...