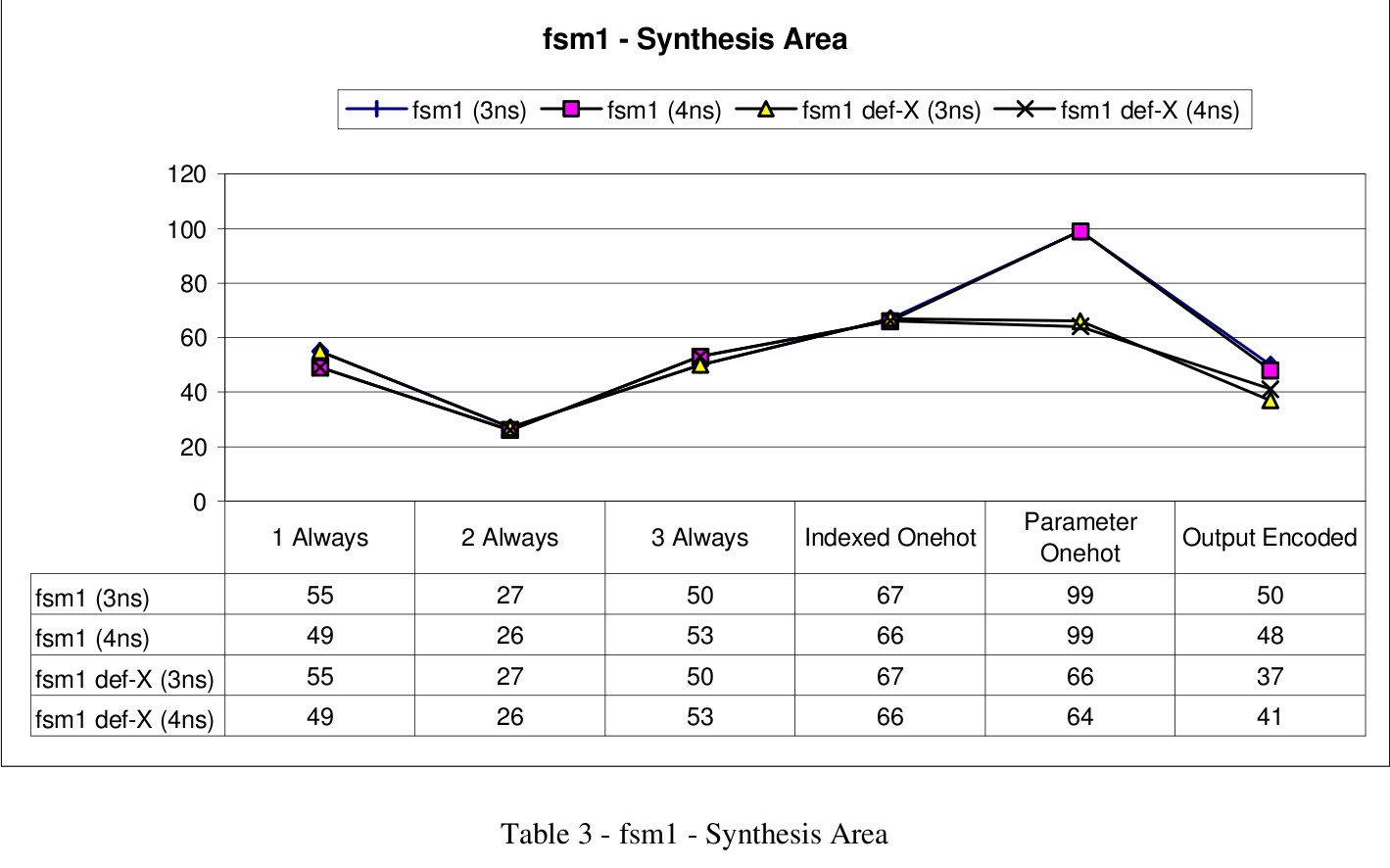

paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm1各种style的timing/area比较

整体说,一般还是用2段式,再加上output encodecd/default -X技巧。

paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm1各种style的timing/area比较的更多相关文章

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之output encoded style with registered outputs(Good style)

把输出跟状态编码结合起来,即使可以省面积又是寄存器输出.但是没有讲解如何实现这种高效的编码.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(index-parameter style with registered outputs)

case语句中,对于state/next 矢量仅仅做了1-bit比较. parameter 值不是表示FSM的状态编码,而是表示state/next变量的索引.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm summary

主要是1.不要用1段式写FSM 2.不要用状态编码写one-hot FSM ,要用索引编码写one-hot FSM.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之全0/1/z/x的SV写法

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之enhanced coding styles

1.ANSI style 的代码比较紧凑. 下面规范推荐,比较好. 下面是带有parameter的module header的完整规范 一般1bit ,大家都是wire signal1 = gen_s ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(encoded-parameter style with registered outputs不推荐但是经常有人写这样的代码)

这样写法,不利与综合,case语句中比较也是full-vector比较.

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 FSM Coding Goals

1.the fsm coding style should be easily modifiable to change state encoding and FSM styles. FSM 的的 状 ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(二段式)

1.Two always block style with combinational outputs(Good Style) 对应的代码如下: 2段式总结: (1)the combinational ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(三段式)

Three always block style with registered outputs(Good style)

随机推荐

- 2017浙江工业大学-校赛决赛 XiaoWei的战斗力

Description XiaoWei沉迷RPG无法自拔,但是他的战斗力只有5,所以他决定氪金提升战斗力.XiaoWei购买了n个福袋.打开1个福袋后,有以下三种情况出现:1.获得屠龙宝刀,概率为p1 ...

- Web自动化测试—PO设计模式(二)

PO设计模式要点一:页面类都继承于BasePage 目录结构 ui_auto_test --src --pages --__init__.py --base_page.py --login_page. ...

- ES5数组遍历

reduce() 方法接收一个函数作为累加器,数组中的每个值(从左到右)开始缩减,最终计算为一个值. array.reduce(function(total, currentValue, curren ...

- is 和 == 区别 编码的问题 id()函数

一丶is 和 == 的区别 == 比较的是值 is 比较的是内存地址 #字符串 a = "abc" b = "abc" print(a == b) print( ...

- js正则匹配获取文件名

//获取文件名,不带后缀 var file_name=file_path.replace(/(.*\/)*([^.]+).*/ig,"$2"); //获取文件后缀 1.var Fi ...

- The first step in solving any problem is recognizing there is one.

The first step in solving any problem is recognizing there is one.解决问题的第一步是要承认确实存在问题.

- 记录下关于SQL server1433端口监听不了的问题

CMD命令netstat -an |findstr 1433,即使在防火墙的入站规则里添加了1433端口的访问,发现1433的端口还是监听不了. 搞了老半天,最终调整了MSSQESERVER的协议下的 ...

- javaSe-字符型和布尔型

其实java数据类型一节就可以全部写完了,为什么还需要字符型和布尔型呢,原因是这俩个都很重要: 字符型用char表示,字符分三种: 普通字符:char a = 'a',普通字符表示一个普通的字符,没有 ...

- python爬虫之路——Python的re模块及其方法

介绍常用的三种方法:search(),sub(),findall() search():匹配并提取第一个符合规律的内容,然后返回一个正则表达式的对象 #提取字符串中的第一个数字 import re a ...

- [转]maven项目部署到tomcat

其实maven项目部署到tomcat的方式很多,我从一开始的打war包到tomcat/webapps目录,到使用tomcat-maven插件,到直接使用servers部署,一路来走过很多弯路. 下面就 ...