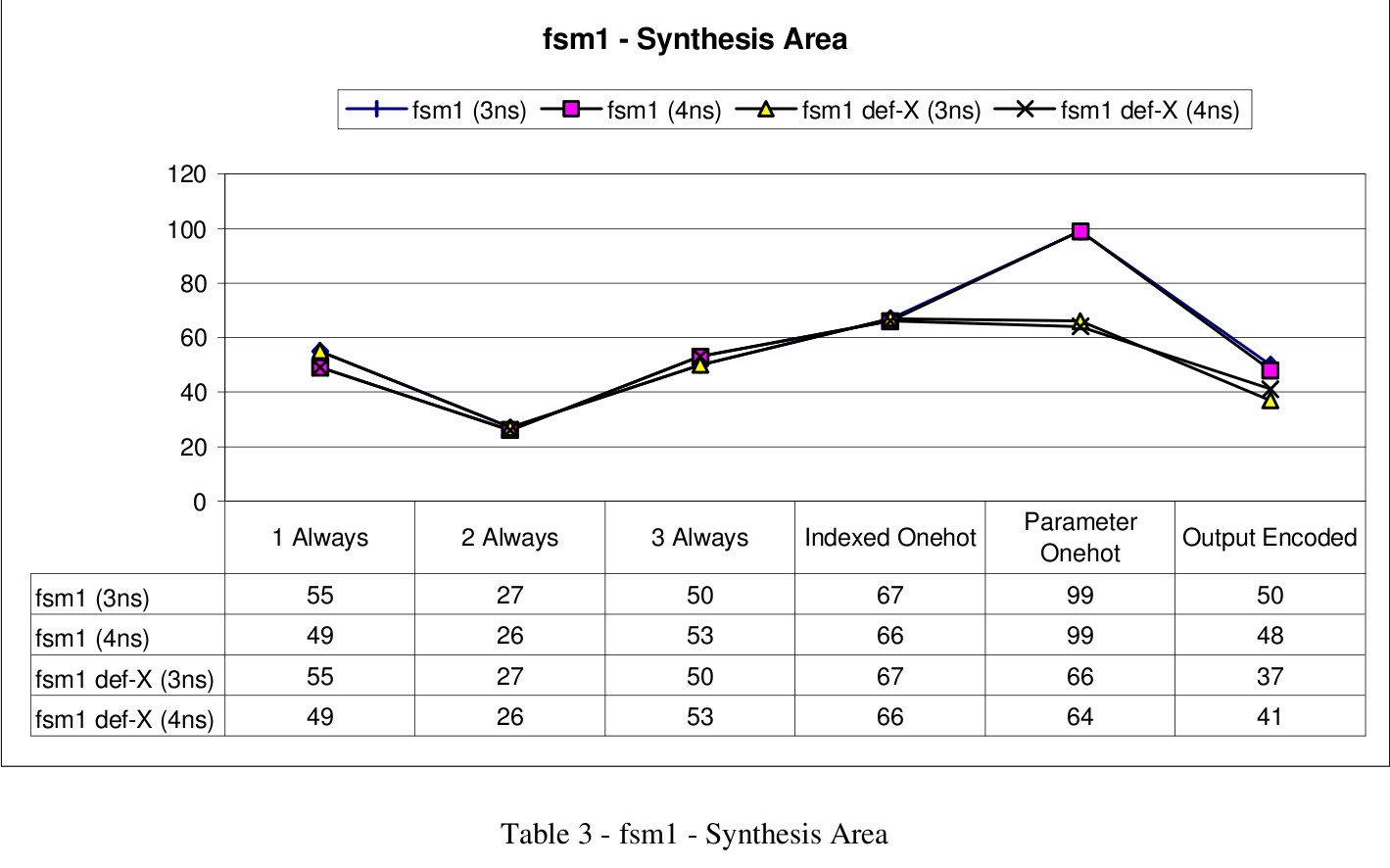

paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm1各种style的timing/area比较

整体说,一般还是用2段式,再加上output encodecd/default -X技巧。

paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm1各种style的timing/area比较的更多相关文章

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之output encoded style with registered outputs(Good style)

把输出跟状态编码结合起来,即使可以省面积又是寄存器输出.但是没有讲解如何实现这种高效的编码.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(index-parameter style with registered outputs)

case语句中,对于state/next 矢量仅仅做了1-bit比较. parameter 值不是表示FSM的状态编码,而是表示state/next变量的索引.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm summary

主要是1.不要用1段式写FSM 2.不要用状态编码写one-hot FSM ,要用索引编码写one-hot FSM.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之全0/1/z/x的SV写法

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之enhanced coding styles

1.ANSI style 的代码比较紧凑. 下面规范推荐,比较好. 下面是带有parameter的module header的完整规范 一般1bit ,大家都是wire signal1 = gen_s ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(encoded-parameter style with registered outputs不推荐但是经常有人写这样的代码)

这样写法,不利与综合,case语句中比较也是full-vector比较.

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 FSM Coding Goals

1.the fsm coding style should be easily modifiable to change state encoding and FSM styles. FSM 的的 状 ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(二段式)

1.Two always block style with combinational outputs(Good Style) 对应的代码如下: 2段式总结: (1)the combinational ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(三段式)

Three always block style with registered outputs(Good style)

随机推荐

- Codeforces Round #558 (Div. 2)

目录 Codeforces Round #558 (Div. 2) 题解 A Eating Soup B Cat Party C Power Transmission D Mysterious Cod ...

- Linux systemd 常用命令

系统管理 systemctl 显示系统状态: $ systemctl status 立即激活单元: # systemctl start [单元] 立即停止单元: # systemctl stop [单 ...

- 引入clipboard.js

引入clipboard.js var clipboardJS = new ClipboardJS('#accept-data'); // 括号内的是选择器

- 健康检查NET Core之跨平台的实时性能监控

ASP.NET Core之跨平台的实时性能监控(2.健康检查) 前言 上篇我们讲了如何使用App Metrics 做一个简单的APM监控,最后提到过健康检查这个东西. 这篇主要就是讲解健康检查的内 ...

- 基于JAVA的设计模式之单例模式

概念 于大二上学期面向对象C++期中考试中有这么道题:一个Computer有多个USB插口,那么意味着这台电脑可以插多个鼠标,但是无论你如何拔插多少个鼠标,桌面上的鼠标一直只显示一个,且多个硬件鼠标都 ...

- Class 学习 (Es6阮一峰)

es5 构造函数 实例: function Point(x, y) { this.x = x; this.y = y; } Point.prototype.toString = function () ...

- 学JS的书籍

1.JavaScript DOM 编程艺术 [说明] 这本书最大的特点就是简明易懂,循序渐进,适合初学者,非常容易上手. 计划:三天读完 读书总结:待写 2.Javascript权威指南 特点是权威. ...

- webm视频转换 其他视频格式转换为webm格式

将其他视频格式转换为webm格式 https://files.cnblogs.com/files/bubuchu/html5videoshipingeshizhuanhuanqi.zip

- 手机安全卫士——在设置中心 自定义view和自定义属性

自定义组合控件 1. 自定义一个View, 继承ViewGroup,比如RelativeLayout,此文中是SettingItemView 2. 编写组合控件的布局文件,在自定义的View中加载 ...

- Android中,Broadcas介绍

什么是广播 在Android中,Broadcast是一种广泛运用的在应用程序之间传输信息的机制.我们拿广播电台来做个比方.我们平常使用收音机收音是这样的:许许多多不同的广播电台通过特定的频率来发送他们 ...